基于多堆叠直接键合铜单元的功率模块封装方法

描述

摘要:碳化硅(SiC)功率模块在电动汽车驱动系统中起着至关重要的作用。为了提高功率模块的性能、减小体积、提高生产效率,本文提出了一种基于多堆叠直接键合铜(DBC)单元的功率模块封装方法,以并行更多的芯片。该方法利用互感对消效应来减小寄生电感。由于新封装中的导电面积增加了一倍,因此可以减小功率模块的整体面积。整个功率模块被分成更小的单元,以提高制造成品率,并提高设计自由度。

本文对所提出的封装结构提供了详细的设计、分析和制作过程。此外,本文还提出了几种可行的电源终端与DBC Units的连接方案。采用这种结构,在一个商用尺寸的功率模块中,每个相腿并联18个芯片。仿真和双脉冲测试结果表明,与传统的封装方式相比,该封装方式的寄生电感减小了74.8%,占地面积减小了34.9%。

一、介绍

随着电动汽车的发展,人们对功率器件性能的要求不断提高,宽禁带器件变得越来越流行,并得到了广泛的应用和研究。例如,碳化硅器件具有低导通电阻、高开关速度、高导热性和高耐压性,显示出其替代硅基功率模块的巨大潜力。然而,制造限制带来过多的内部缺陷,限制了单个芯片的电流传导能力。因此,在大功率、大电流应用中,电源模块往往需要并联大量SiC芯片,多芯片并联的电源模块的布局设计就显得尤为重要。

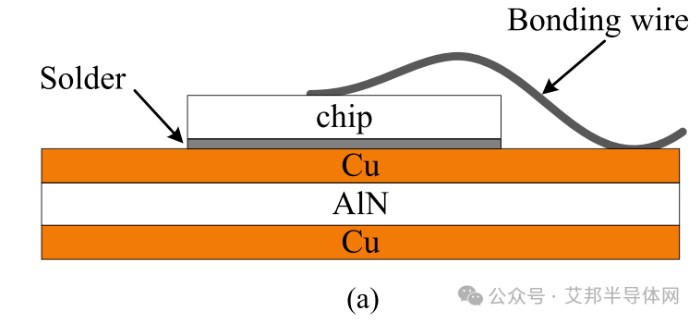

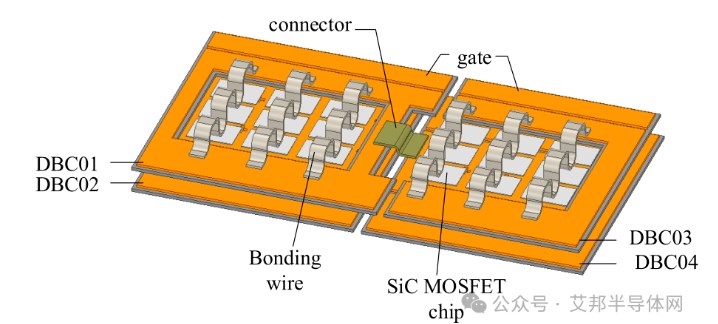

图1 传统2D布局功率模块结构

由于成熟且制造工艺简单,传统的2D引线键合封装结构仍然广泛应用于商用SiC功率模块中。如图1所示,引线键合互连具有相对较大的寄生电感,这可能会显着限制SiC器件的开关速度。典型的引线键合连接如图2(a)所示。

图2(a) 传统的引线键合封装

因此,多SiC芯片并联的功率模块主要存在两个问题:

1)功率模块的寄生电感会带来较大的电压过冲,di/dt急剧增加。目前,越来越多的电动汽车需要800V母线电压来支持1200V功率模块。出于安全原因,寄生电感越小越好。

2)更高的功率额定值需要更好的电流平衡能力和更宽的DBC传导路径。一般来说,1mm宽的DBC设计用于传导100A电流,这意味着1000A的功率模块需要在DBC上有10mm的电流传导路径。在一篇参考文献中,功率模块的总面积估计为芯片总面积的4-5倍。更宽的传导路径可能会阻碍功率模块设计人员控制整齐的布线、良好的电流共享和先进的散热平衡,因此,当芯片数量增加时,整体面积增加更多,导致功率密度下降。

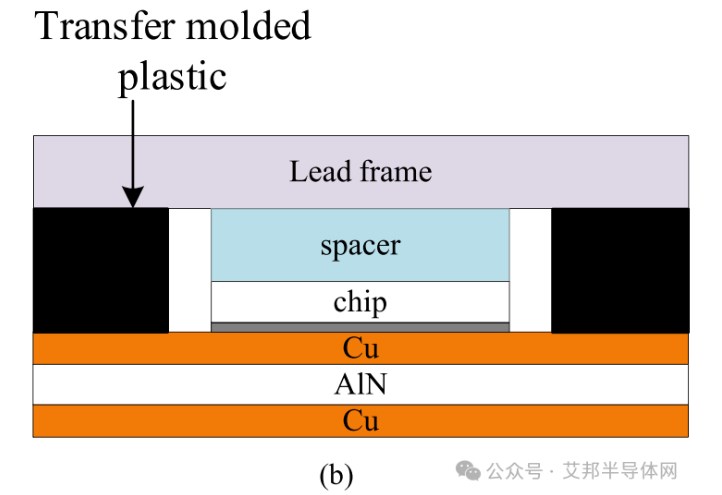

这些问题严重限制了宽带隙功率器件的应用,进一步制约了开关频率、功率密度和转换效率的提高。因此,有必要探索新的高功率密度封装设计来减少寄生,并改善功率模块内部的电流平衡。 近年来,许多研究人员提出了不同的新布局方法。如图2(b)所示,平面封装结构利用DBC的宽铜箔来降低寄生阻抗并具有更高的功率密度,并且可以实现双面冷却。但平面封装也有缺点:平面模组生产过程中需要引入注塑机等专用设备,导致工艺成熟度较低,短期内发展受到限制。此外,并行芯片的数量也受到限制。上述原因导致平面结构的商用模组最多只能并联8颗芯片。

图2(b) 平面封装结构

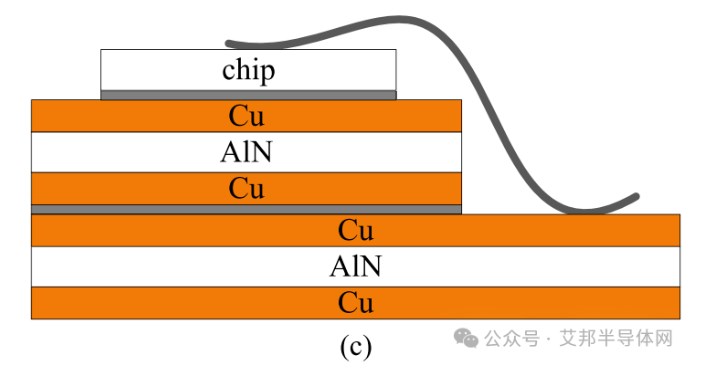

T. Huber 提出了一种1000V/200A半桥模块,其基板类似于多层基板,这两种模块都通过多个陶瓷基板实现了低寄生电感。然而,如图2(c)所示,两个模块都焊接在两个陶瓷基板的顶层上,这不仅使制造工艺复杂化,而且与常见的2D布局相比也增加了热阻。

图2(c) T.Huber提出的封装结构

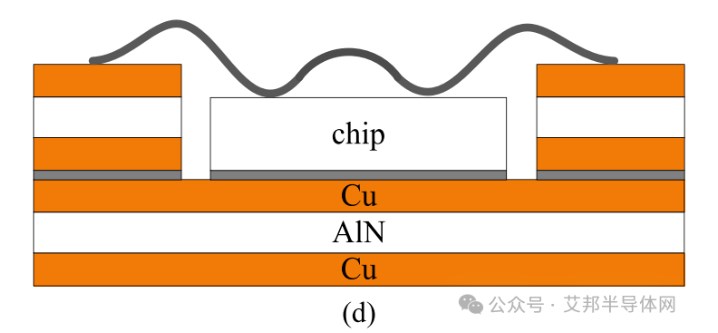

如图2(d)所示,陈等人改进芯片位置开发1200V/60A堆叠DBC封装SiC功率模块,将功率回路电感降至5nH,并将驱动器和散热器集成到封装中,但这种设计容错能力较低,没有考虑栅极对称性问题,无法并联多个芯片。

图2(d) 陈等人改进的封装结构

二、DBC固定单元包设计

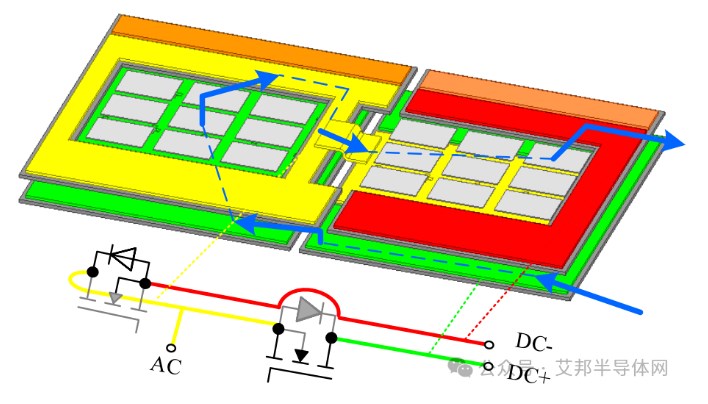

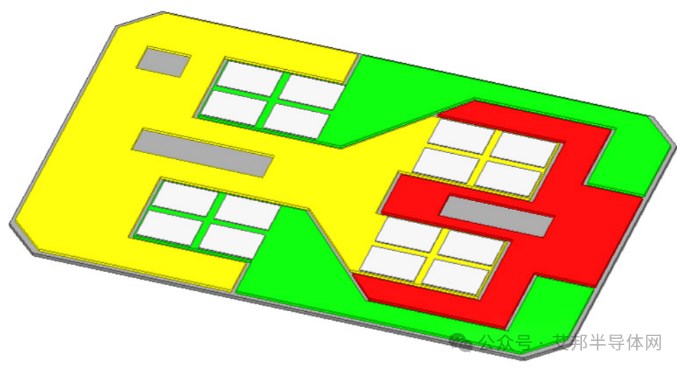

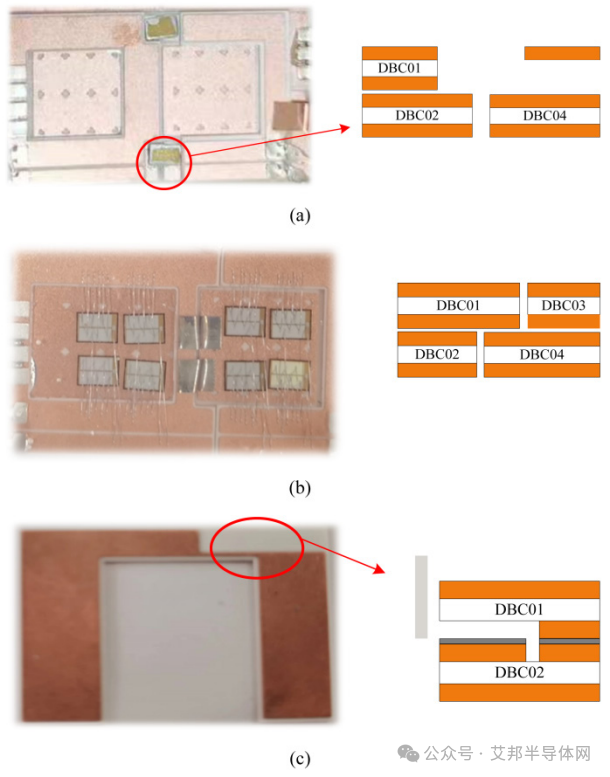

针对上述问题,本文提出了一种低寄生电感、小尺寸、高生产率的多DBC堆叠单元封装功率模块。如图3所示,模块基板由DBC堆叠而成,底部两个DBC上各焊接9个SiC MOSFET裸片,形成半桥电路。MOSFET的漏极焊盘通过焊料连接到底部DBC,而MOSFET的栅极和源极焊盘通过引线键合连接到顶部DBC。连接器被焊接以连接DBC 02上开关的源极和DBC 04上开关的漏极。DBC 02和DBC 04通过DBC 01的底部铜层连接。

图3 模拟 DBC 单元图示

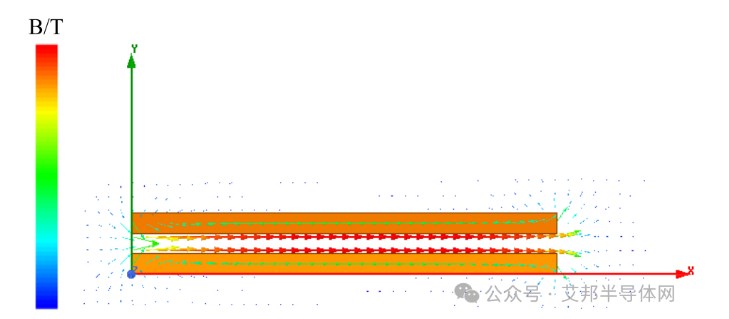

由于这种封装方法,整个DBC被分成更小的单元,以提高制造良率。小型DBC单元可以灵活组合,提高设计自由度并实现更复杂的模块布局。另外,该方法利用互感抵消效应,显着降低寄生电感,在堆叠母线设计中得到了广泛的应用。如图4所示,堆叠导体周围的磁场几乎被抵消。

图4 堆叠母线导体周围的电磁场分布

SiC最重要的优势之一是开关速度快,这也意味着SiC功率模块封装需要更低的开关损耗。同时,寄生参数对开关特性有显着影响,尤其是在高开关速度下。所提出的功率模块单元的电流环路如图5所示,电流在两层中的蓝色路径中流动,可以有效降低寄生电感。通过Ansys Q3D提取寄生电感,结果表明,所提出的电源模块单元的寄生电感为4.74 nH。相比之下,如图6所示,类似额定功率的传统布局模块的寄生电感为18.84 nH。

图5 模块的电气连接路径

图6 传统布局单元 Q3D 模型

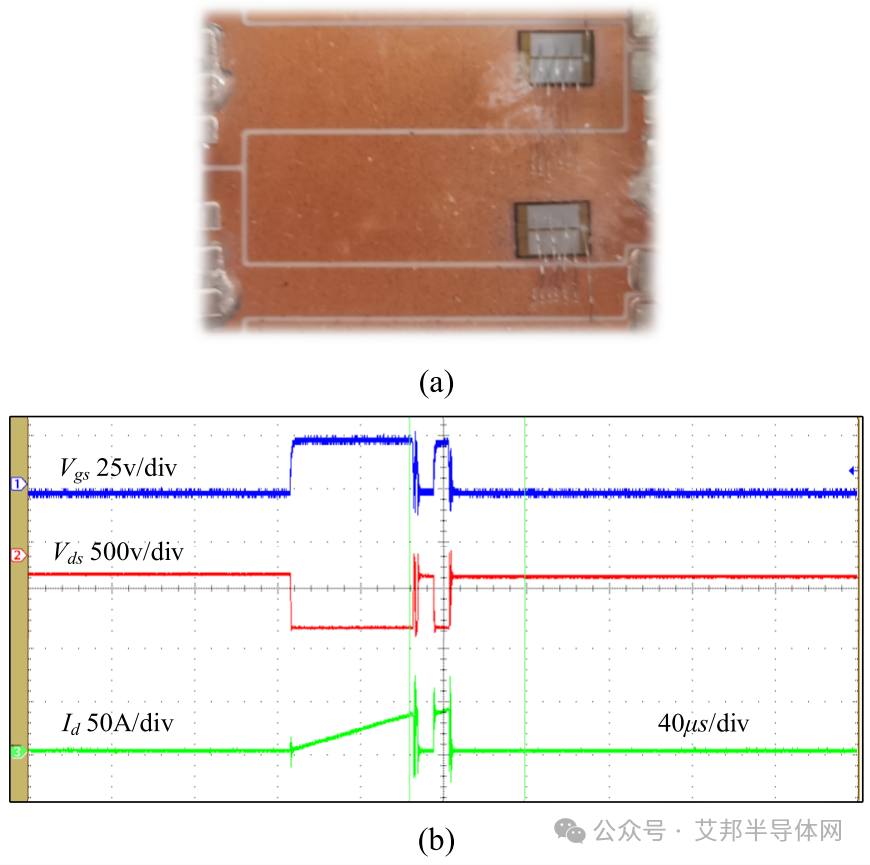

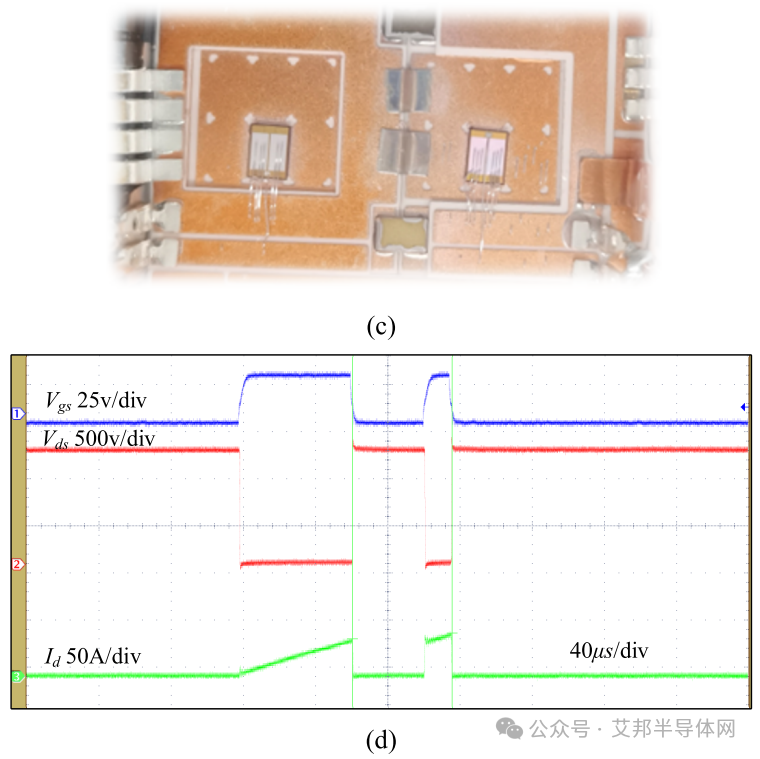

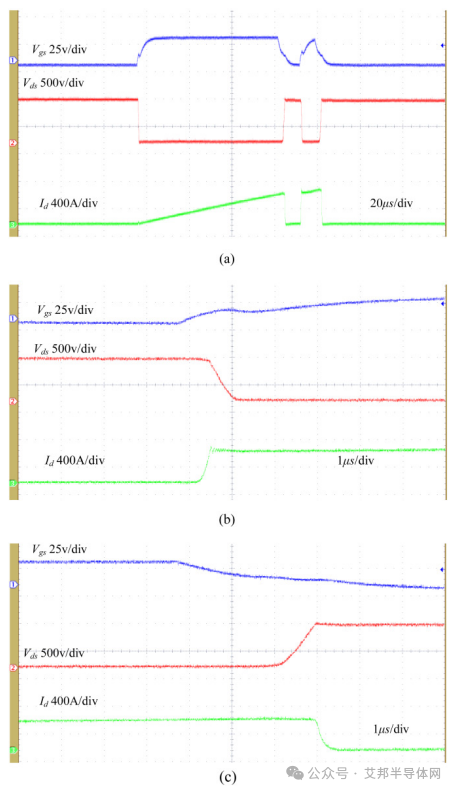

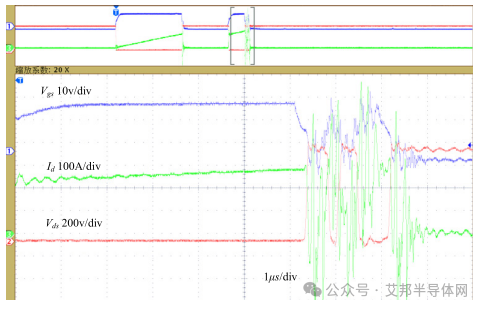

为了验证所提出的封装的可行性,如图7所示,在仅将一个芯片焊接到开关的布局上进行了双脉冲测试(DPT)实验。图7(a)是传统布局电源模块,图7(b)是传统模块DPT波形,图7(c)是建议布局电源模块,图7(b)是建议模块DPT波形。经过对比测试,传统封装功率模块勉强通过了600V DPT。然而,由于寄生电感较大,栅极开始振荡。相反,所提出的封装通过了800V双脉冲测试并且具有良好的波形。

图7 测试结果对比 (a) 传统布局功率模块 (b) 传统模块DPT波形 (c) 模拟功率模块布局 (b) 模拟模块DPT波形。

三、高密度SiC功率模块设计制造

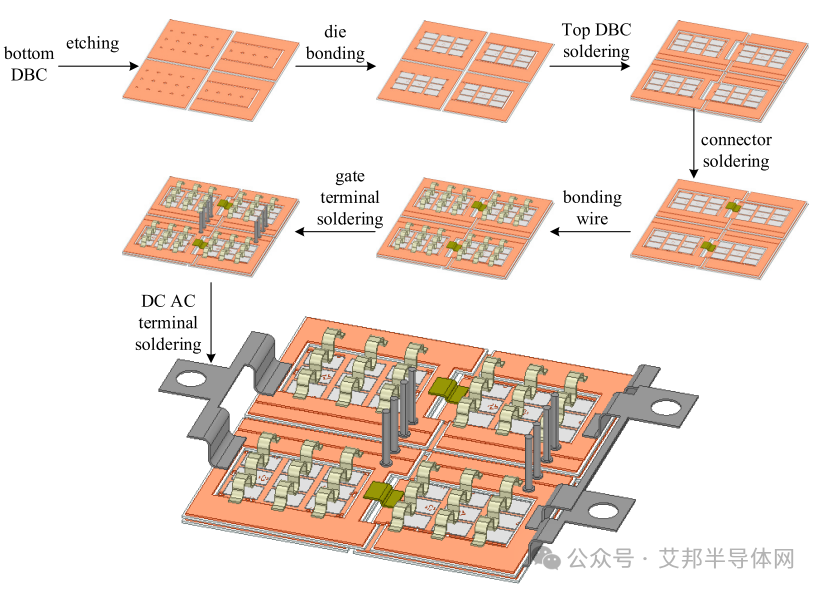

图8显示了所提出的电源模块的制造过程。首先根据电路连接要求和芯片所需的定位,刻蚀4个底部DBC。然后,对芯片进行引线键合和真空回流焊接。接下来,将顶层DBC焊接到底层DBC上形成堆叠,并将连接器焊接到需要连接的DBC上。然后,使用超声波焊接将芯片栅极和源极焊接至顶层DBC引线。最后,将端子一一焊接。

图8 所提出的电源模块的制造过程

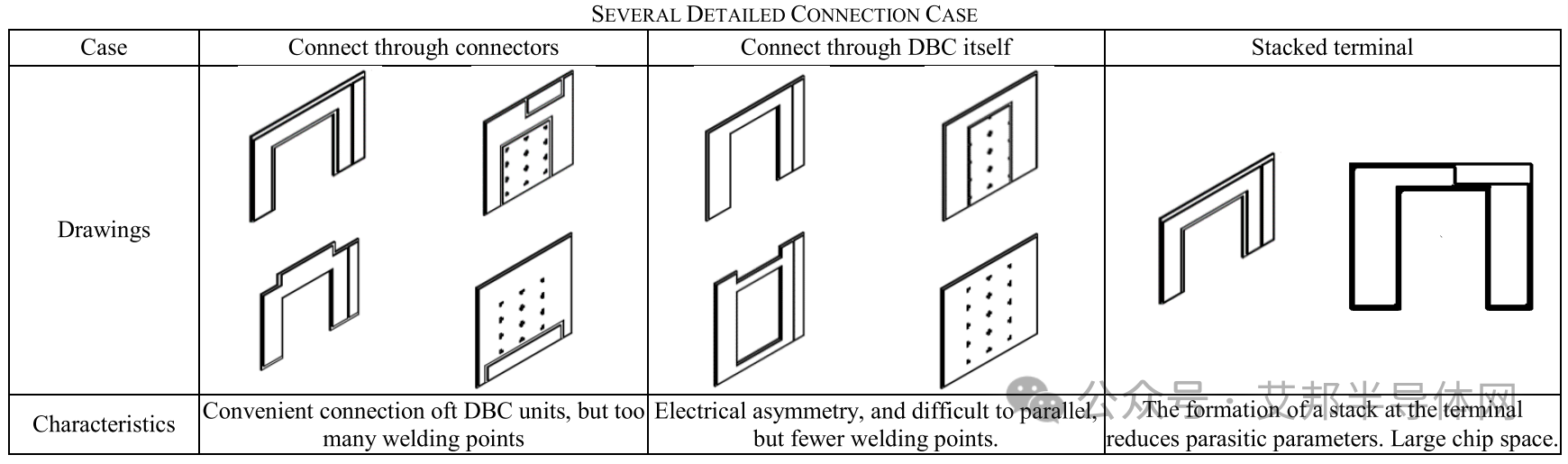

表Ⅰ提供了不同DBC单元之间连接的几个详细图纸和特性,以及终端连接问题。表Ⅰ第一列提供了不同堆叠DBC之间的两个间隙通过连接器进行焊接的解决方案,如图9(a)所示,在不同的DBC单元之间实现连接,焊接点过多且端子不匹配。表Ⅰ第二栏提供了利用DBC底部铜片之间连接的低焊点设计,这在之前的设计中也提到过,但没有考虑对称性问题,导致不同DBC单元并联困难,如图9(b)所示。表Ⅰ中的第三列利用三维空间,将端子设置在DBC下方的间隙处,在端子处形成堆叠,以减少寄生电感,这也可以节省更多的芯片空间并并行多个芯片,如图9(c)。

表Ⅰ 几种详细连接情况

图9 连接的不同情况 (a) 通过连接器连接 (b) 通过 DBC 本身进行连接 (c) 堆叠式终端

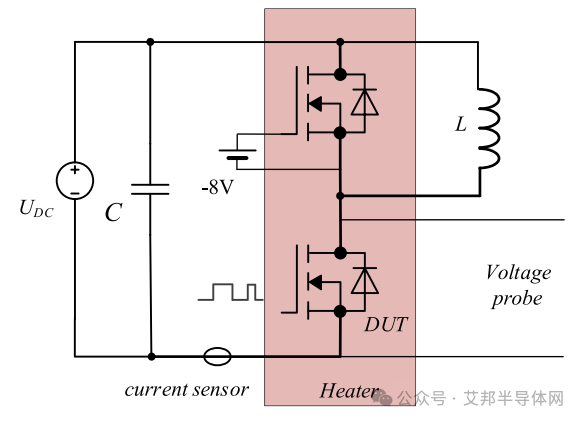

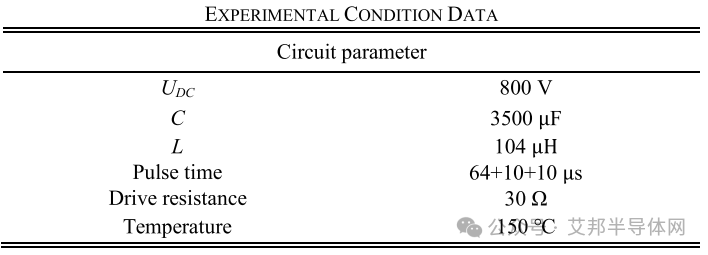

为了验证所提出的多DBC堆叠单元封装的可行性,如图10所示,制作了18个并联芯片的功率模块单元。该开关器件的动态性能,如电压振荡、电压过冲和开关损耗等,可以通过图11所示的DPT电路获得,实验电路参数如表Ⅱ所示。该电路基于半桥电路,下部开关作为被测器件。使用高压隔离差分探头测量漏源电压Vds,使用Rogowski线圈电流探头测量漏极电流Id。使用常规探针测量栅源电压Vgs。上开关管的栅极受到负电压,因此上开关管关断,只有续流工作。

图10 模拟功率模块单元

图11 双脉冲测试电路

表Ⅱ 实验参数

双脉冲结果波形如图12(a)所示,第一个脉冲的导通过程如图12(b)所示,第二个脉冲的关断过程如图12(c)所示。蓝色波形是栅极驱动信号Vgs,红色信号是测量的开关漏源电压Vds ,绿色波形是漏极电流Id。可以看出,模块已通过800V/500A的DPT。

图12 波形结果 (a) 双脉冲测试波形,(b) 第一个脉冲开启过程,(c) 第二个脉冲关闭过程

图13 传统布局模块波形

针对传统2D布局功率模块的缺点,本文提出了一种SiC功率模块采用多个DBC堆叠单元的封装方法。详细介绍了建议的DBC单元和电源模块,以及提供了不同DBC之间的多种连接情况。实验和仿真结果表明,所提出的封装模块具有以下优点:

1)创新的多DBC单元封装设计,可有效降低寄生电感,并具有良好的电气性能。 2)载流能力增加,相同电流下,可减少模块的平面面积,允许更多芯片并联。

3)与平面封装相比,所提出的模块工艺简单,成本降低。而且单元设计还可以提高生产率。

转载:艾邦半导体网

-

一文详解多芯片封装技术2025-05-14 2545

-

功率模块铜线键合工艺参数优化设计方案2024-01-03 2850

-

如何实现高功率密度三相全桥SiC功率模块设计与开发呢?2024-03-13 4446

-

从微米到纳米,铜-铜混合键合重塑3D封装技术格局2025-06-29 1870

-

硅-直接键合技术的应用2018-11-23 3488

-

芯片堆叠的主要形式2020-11-27 4781

-

大功率IGBT模块封装中的超声引线键合技术2011-10-26 1928

-

功率模块引线键合界面温度循环下的寿命预测2018-03-08 1367

-

晶圆直接键合及室温键合技术研究进展2023-06-14 4055

-

什么是Cu clip封装?碳化硅功率模块键合方式2023-10-24 6160

-

IGBT模块银烧结工艺引线键合工艺研究2023-12-20 4166

-

电子封装 | Die Bonding 芯片键合的主要方法和工艺2024-09-20 3203

-

三维堆叠封装新突破:混合键合技术揭秘!2024-11-13 4109

-

德州仪器:铜键合线在半导体封装中的应用变革2026-01-18 1327

全部0条评论

快来发表一下你的评论吧 !