一文理解2.5D和3D封装技术

描述

随着半导体行业的快速发展,先进封装技术成为了提升芯片性能和功能密度的关键。近年来,作为2.5D和3D封装技术之间的一种结合方案,3.5D封装技术逐渐走向前台。

什么是3.5D封装技术

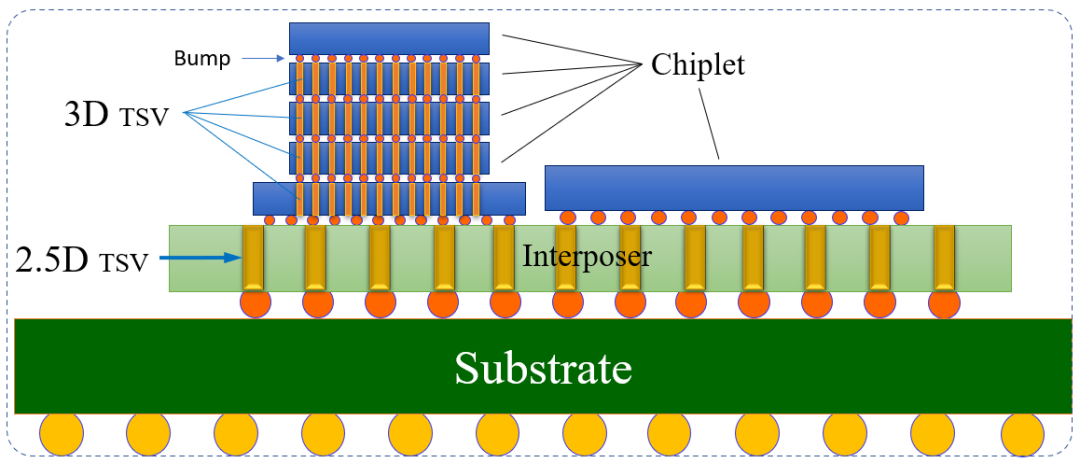

3.5D封装技术最简单的理解就是3D+2.5D,通过将逻辑芯片堆叠并将它们分别粘合到其他组件共享的基板上,创造了一种新的架构。能够缩短信号传输的距离,大幅提升处理速度,这对于人工智能和大数据应用尤为重要。

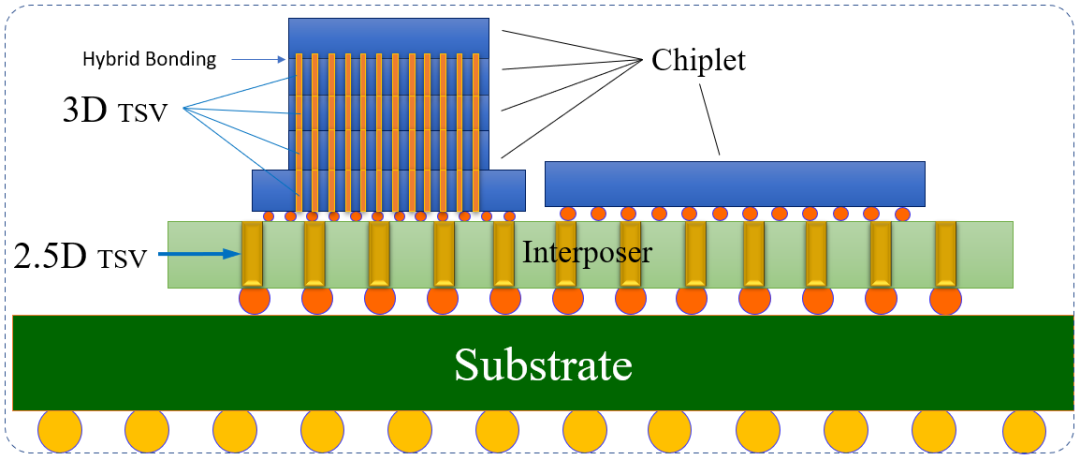

不过,既然有了全新的名称,必然要带有新的技术加持 —— 混合键和技术(Hybrid Bonding)。混合键合技术的应用为3.5D封装带来了新的可能性,是一种在相互堆叠的芯片之间获得更密集互连的方法。

混合键合技术加持的3D TSV的直接互连

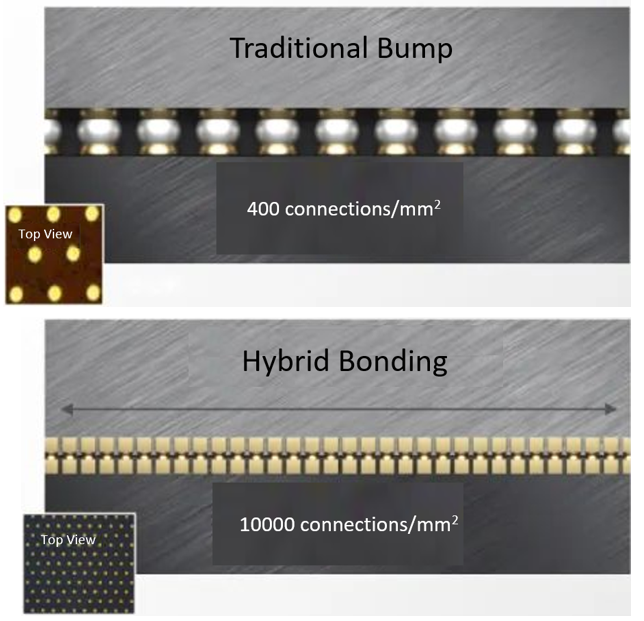

通过混合键合,可以在更小的空间内实现更多的连接,从而提高封装的密度和性能。下图是传统凸点和混合键合技术的结构比较:传统凸点间距是50微米,每平方毫米有大约400个连接;混合键和大约10微米的间距,可达到每平方毫米10000个连接。

传统凸点和混合键合技术的结构比较

混合键合解决了另一个棘手的问题,即数千个微凸块之间的共面性,而制造传统键合产品很难以合理的产量满足这一要求。混合键合技术应用于3D TSV的直接互连,省却了凸点,其界面互连间距可小于10um甚至1um,其互连密度则可达到每平方毫米10000~1000000个点。这是传统的凸点互连远远无法达到的,因此,在高密度的3D互连中,凸点最终会消失。

另外,SRAM作为处理器缓存的首选,通过3.5D封装技术可以在不增加物理面积的情况下实现更多内存的集成。SRAM不一定必须与处理器的先进节点处于同一节点,这也有助于提高产量和可靠性。

在最近的三星代工活动中,该公司代工业务开发副总裁Taejoong Song展示了3.5D配置的路线图,将使用2nm芯片堆叠在4nm芯片上,2027年将使用1.4nm芯片堆叠在2nm芯片上。

英特尔代工厂的方法在很多方面都很相似。英特尔高级副总裁兼代工服务总经理Kevin O'Buckley表示:“我们的3.5D技术是在带有硅桥的基板上实现的。这不是成本极高、产量低、多掩模版形状的硅,甚至不是RDL。我们以更具成本效益的方式使用薄硅片,通过硅桥实现芯片到芯片的连接,甚至是堆叠芯片到芯片的连接。因此,您可以获得相同的硅密度优势,以及该硅桥的相同SI(信号完整性)性能,而无需在整个硅桥下方放置巨大的单片中介层,这既成本高昂又限制了容量。它正在发挥作用。它正在实验室中运行。”

3.5D封装技术的挑战

虽然当前的技术已经能够实现较为稳定的3.5D封装,但在大规模生产和应用中,仍需要进一步降低成本和提高良率,工艺的复杂性和制造成本是制约其大规模应用的主要因素。其次,3.5D封装的可靠性和长期稳定性也需要进一步验证,特别是在高温和高压环境下的应用场景中。

除此之外,散热可能是最难解决的问题:工作负载可能会有很大差异,从而产生动态热梯度并将热量困在意想不到的地方,从而缩短芯片的使用寿命和可靠性。

理解2.5D和3D封装技术

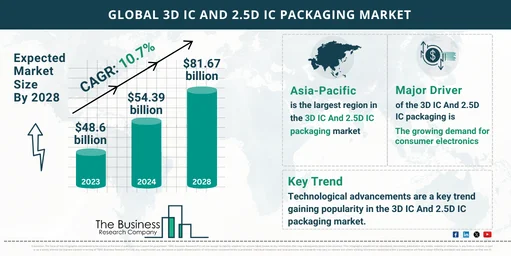

一直以来,提升芯片性能主要依靠先进制程的突破。但现在,人工智能对算力的需求,将芯片封装技术的重要性提升至前所未有的高度。为了提升AI芯片的集成度和性能,高级封装技术如2.5D/3D封装和Chiplet等得到了广泛应用。

根据研究机构的调研,到2028年,2.5D及3D封装将成为仅次于晶圆级封装的第二大先进封装形式。这一技术不仅能够提高芯片的性能和集成度,还能有效降低功耗,为AI和高性能计算等领域提供强有力的支持。

· 2.5D封装技术

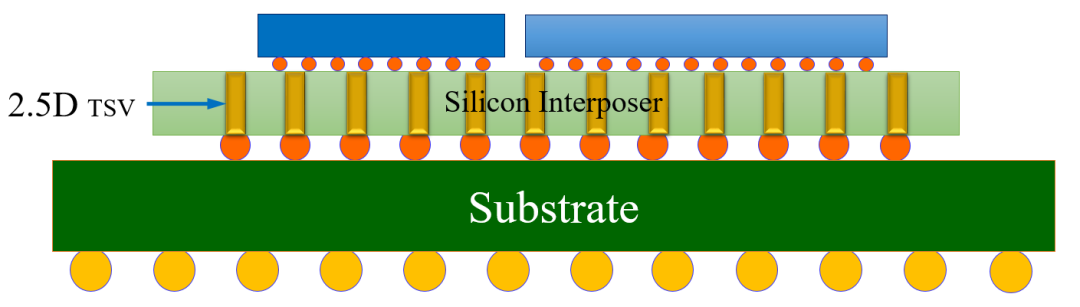

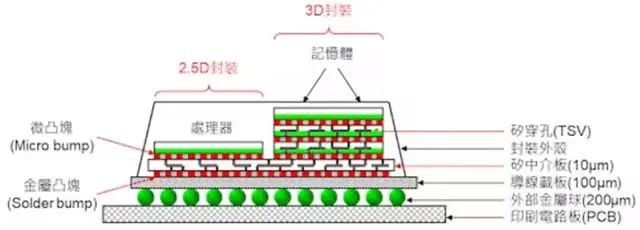

2008年,赛灵思将其大型FPGA划分为四个良率更高的较小芯片,并将这些芯片连接到硅中介层,2.5D封装由此诞生。2.5D封装技术是一种介于传统2D封装和3D封装之间的过渡技术,通过在硅中介层(Silicon Interposer)上集成多个裸芯片(Bare Die),实现了芯片之间的高速互连和短距离通信。硅中介层通常采用硅通孔(Through-Silicon Via,TSV)技术实现垂直互连,具有高密度、高性能的互连特性,可以大大提高系统的整体性能。

2.5D封装的整体结构

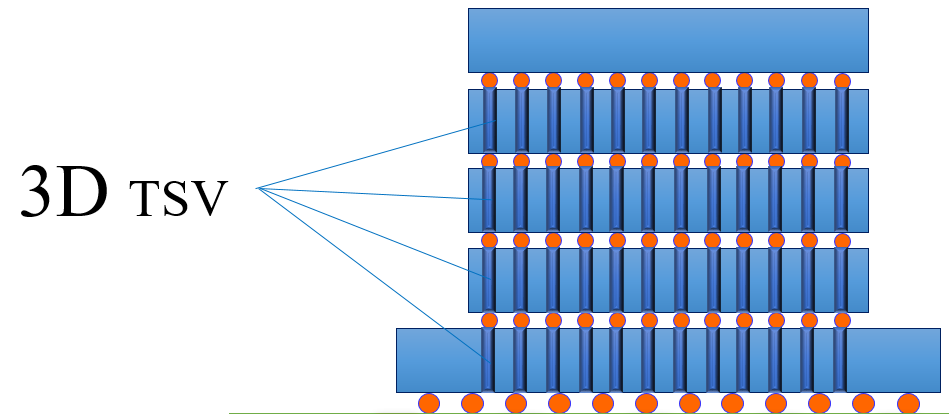

· 3D封装技术

3D封装是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。但是要注意的是,3D封装不一定要用到TSV技术,通过引线键合(Wire Bonding)的方式连接且在空间上进行芯片堆叠并封装都能成为3D封装。

3D封装的整体结构

The Business Research Company近日发布了3D IC和2.5D IC封装市场研究报告,预计未来几年,3D IC和2.5D IC封装市场规模将快速增长:将从2023年的486亿美元增长到2024年的543.9亿美元,复合年增长率(CAGR)为 11.9%,到2028年,市场规模将达到816.7亿美元,CAGR为10.7%。预测期内的增长可归因于可穿戴和便携式设备的出现、能效需求的增长、高性能计算需求的上升、向片上系统设计的转变、半导体器件复杂性的增加以及物联网的普及。

另外,据市场分析机构Global Market Insights Inc.数据,2023年3D半导体封装市场价值94亿美元,预计2024年至2032年期间的CAGR将超过18%。

2.5D和3D封装技术的区别

2.5D可以看两块积木在二维尺度是无法拼接在一起的,需要一个中介放在两块积木之下,且可以同时对两块积木进行连接;3D就直接积木与积木垂直(其实也不一定)的堆叠在一起,而积木就是一个个芯片。2.5D封装是利用导电凸块或TSV将组件堆栈在中介层上,3D IC封装则将多层硅晶圆与采用TSV的组件连接在一起。

3D封装中逻辑裸晶堆栈在一起或与储存裸晶堆栈在一起,无需建构大型的系统单芯片。3D封装技术在垂直方向上实现了更高的集成度,而2.5D封装技术则通过硅中介层实现了水平方向上的高密度互连。

先进封装中的关键技术

引线键合(Wire Bonding):采用直接穿过有源电路的多层互连结构,同时通过采用3D架构,可以将芯片折叠到它自己的上面,减小了互连线长度。这样不仅会极大地提高电路性能,还会极大地降低电路的功耗。

硅通孔技术(Through Silicon Via,TSV):通过在硅片上打孔并填充导电材料实现了芯片之间的垂直电气连接,可以完成连通上下层晶圆或芯片的功能,在更小的面积上大幅提升芯片性能并增加芯片功能。这种连接方式具有低电阻、低电容和低电感的特点,可以显著提高信号传输的速度和稳定性。TSV用途大致分为三种:背面连接(应用于CIS等)、2.5D封装(TSV在硅中介层)、3D封装(TSV位于有源晶粒中,用于实现芯片堆叠)。

中介层(Interposers):中介层是封装中多芯片裸晶或电路板传递电信号的管道,是插口或接头之间的电接口,可以将信号传播更远,也可以连接到板子上的其他插口。中介层可以由硅和有机材料制成,充当多颗裸晶和电路板之间的桥梁。硅中介层是一种经过验证的技术,具有较高的细间距I/O密度和TSV形成能力,在2.5D和3D IC芯片封装中扮演着关键角色。

2D封装加上Interposer后就变成了2.5D,那么3D封装加上Interposer自然就变成了3.5D,既合情合理,又符合了通用的命名法则。

重分布层:重分布层包含铜连接线或走线,用于实现封装各个部分之间的电气连接。它是金属或高分子介电材料层,裸晶可以堆栈在封装中,从而缩小大芯片组的I/O间距。重分布层已成为2.5D和3D封装解决方案中不可或缺的一部分,使其上的芯片可以利用中介层相互进行通讯。

高带宽内存(High Bandwidth Memory,HBM):是一种用于3D堆叠同步动态随机存取内存的高速计算机内存接口,最初由三星、AMD和SK Hynix开发,是将很多个DDR芯片堆叠在一起后和GPU封装在一起,实现大容量。在堆叠内,芯片通过TSV和微凸块垂直互连。

-

新型2.5D和3D封装技术的挑战2020-06-16 8796

-

异构集成基础:基于工业的2.5D/3D寻径和协同设计方法2021-07-05 1191

-

2.5D/3D芯片-封装-系统协同仿真技术研究2022-05-06 1447

-

分享一下小芯片集成的2.5D/3D IC封装技术2022-08-24 5879

-

3D封装与2.5D封装比较2023-04-03 5773

-

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍2023-08-01 5574

-

智原推出2.5D/3D先进封装服务, 无缝整合小芯片2023-11-20 1415

-

2.5D和3D封装的差异和应用2024-01-07 5338

-

探秘2.5D与3D封装技术:未来电子系统的新篇章!2024-02-01 5706

-

2.5D与3D封装技术:未来电子系统的新篇章2024-04-18 1975

-

2.5D/3D封装技术升级,拉高AI芯片性能天花板2024-07-11 9872

-

探秘2.5D与3D封装技术:未来电子系统的新篇章2024-07-30 2078

-

技术资讯 | 2.5D 与 3D 封装2024-12-07 3309

-

2.5D和3D封装技术介绍2025-01-14 3678

-

2D、2.5D与3D封装技术的区别与应用解析2026-01-15 1271

全部0条评论

快来发表一下你的评论吧 !