西门子EDA助力Chipletz将系统级封装概念推向未来

EDA/IC设计

描述

Chipletz是由来自Advanced Micro Devices, Inc. (AMD) 和其他主要系统提供商的行业资深人士出资成立的一家初创公司。他们的愿景是开发一种先进封装技术来彻底改变半导体封装内功能,以填补摩尔定律放缓与对计算性能不断增长的需求之间的鸿沟。Chipletz的Smart Substrate产品可帮助以异构方式将多个IC集成在一个封装中,以支持关键AI工作负载、沉浸式消费者体验和高性能计算。

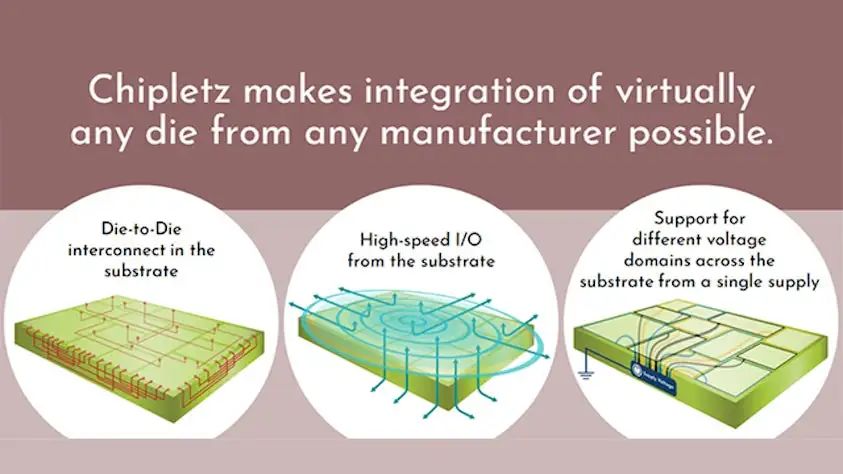

Chipletz技能娴熟的工程师团队具有数十年的半导体设计、制造和封装经验来满足这一需求。Chipletz正将系统级封装概念推向未来,为未来数年的性能提升开辟一条前进之路,同时重新设定半导体集成的经济模式。通过其基于Smart Substrate的独特平台,Chipletz让几乎任何制造商的任何芯片都有可能集成在一起。

Smart Substrate提供裸片到裸片互连和高速I/O,并支持来自单个电源的不同电压域,优于当前的多芯片模块和系统级封装方案。

Michael Su

Chipletz首席技术官

基于我们的Smart Substrate进行设计对设计人员及其设计工具提出了许多具有挑战性的要求。当我们评估EDA供应商及其技术时,这些要求是关键的评估因素。

Chipletz采用的主要选择标准可总结如下

支持高带宽存储器 (HBM) 通道设计

具有超大连接结构的超大型设计上的交互性能

先进的基底脱气设计功能

通过复用创建复杂的电源和接地结构

设计工具和设计流程的自动化与定制

能够开发Smart Substrate专用的定制设计规则检查 (DRC)

供应商的领域专业知识和技术资源可用性与可信度

为了评估西门子Xpedition半导体封装技术,Chipletz使用了一种由超大型SoC组成的设计,SoC两侧是四个HBM堆叠,去耦电容器集成到Smart Substrate中。该器件的尺寸约为50 mm x 65 mm,总共8000多个网络使用约120万个过孔连接裸片,包含2800个焊球的BGA上总计有超过18万个器件管脚。该设计采用了其Smart Substrate技术,使用了150多个复用电路,金属层减少到仅9层,而之前使用硅中介层的版本需要16个金属层。

Chipletz Smart Substrate

Chipletz通过许多使用场景对西门子技术及其技术专家进行了广泛的评估,以验证该解决方案是否适合其未来的多芯片异构设计。作为此次评估的结果,Chipletz选择了西门子半导体封装技术来设计其基于Smart Substrate的独特先进封装。

Bryan Black

Chipletz首席执行官

作为一家无晶圆厂基底供应商和小芯片集成商,我们开发先进封装技术来填补摩尔定律放缓与对计算性能不断增长的需求之间的鸿沟。我们选择西门子的原因是,他们展示了优秀的技术能力,并且在先进异构半导体封装设计方面拥有丰富的专业知识。

自从选择西门子以来,该团队已经完成了他们的首个设计计划,并对他们在合作伙伴、供应商和技术方面做出的正确选择继续感到满意。

Chipletz预计其下一个重点领域将围绕热和热致机械应力,西门子在这两个方面拥有成熟的技术。

-

西门子收购Mentor会对EDA工具用户带来哪些改变?2016-12-08 1528

-

加速创“芯” 西门子EDA技术峰会在沪举办2023-08-27 584

-

系统级芯片设计趋势之下,西门子EDA的前瞻部署2022-07-29 5193

-

西门子收购Solido强势进军EDA领域2018-01-03 2160

-

Chipletz选择西门子EDA半导体封装技术来设计智能基板产品2023-01-17 693

-

Chipletz采用西门子EDA解决方案,攻克Smart Substrate IC封装技术2023-04-14 1180

-

EDA助力良率提升:紫光展锐与西门子的成功合作2024-01-26 1573

-

nepes采用西门子EDA先进设计流程,扩展3D封装能力2024-03-11 3214

-

是德科技与西门子EDA深化合作,共促无线与国防通信系统设计2024-10-30 1468

-

是德科技携手西门子EDA加速无线和国防通信系统设计2024-10-31 1280

-

西门子EDA将参加2025玄铁RISC-V生态大会2025-01-17 2251

-

西门子EDA新一代平台版本升级2025-02-27 1021

-

西门子EDA工具如何助力行业克服技术挑战2025-03-20 2048

-

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商2025-05-20 1331

-

2025西门子EDA技术峰会圆满落幕2025-09-05 3985

全部0条评论

快来发表一下你的评论吧 !