浅谈PLL锁定的检测方法和模拟检测的用意

模拟技术

2518人已加入

描述

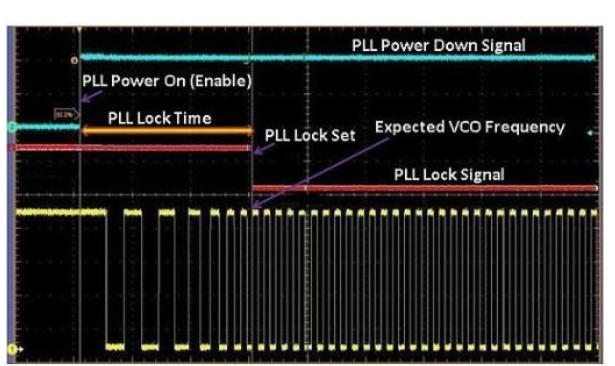

1.PLL锁定有哪些检测方法,它们特点是什么?

一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。

另一种方式是模拟锁定检测,也称为N沟道漏级开路检测,它的实现原则是通过对于PFD输出的超前和滞后脉冲做XOR操作,直接将得出的结果输出。由于XOR的结果有是一串高低的脉冲,所以需要外部电路作滤波处理才能得到一个电平值,而且由于是漏级开路逻辑,所以需要在输出上接上拉电阻。这种检测方式设计起来比较麻烦,需要仔细的计算滤波电容,以及上拉和串接电容,但是这种检测方式有很多独特的特点,是数字检测所代替不了的。

2.既然数字检测比较简单,为什么还用模拟检测?

数字检测在一些非常常规应用中,应用比较好。但是当遇到,参考丢失,驱动精准的VCXO,高鉴相频率等情况时,往往失去了它的简单优势,使得检测变得十分的不可靠。

由于数字检测是采用输入的参考时钟,对于鉴相结果进行处理,得出判决结果的,一旦参考丢失,将无法判决鉴相的结果,从而出现参考丢失任然不报失锁的情况。

当驱动的比较精准的VCXO时,由于VCXO的分频后的频率值与参考分频后频率值非常的接近,所以鉴相结果误差太小,有些锁相环判决的精度没有那么高,造成即使不锁定,仍然报失锁的情况。

当鉴相的频率很高时,鉴相的窄脉冲,无法被检测时钟正确检测,造成虚报锁定。而模拟检测克服上述问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何手动选择频段以缩短PLL锁定时间2018-08-04 2992

-

请问手动选择频段如何缩短PLL锁定时间和PLL锁定过程流程是什么2018-10-31 3060

-

PLL锁定时间从4.5ms缩短到360μs的手动方法2018-11-01 2028

-

测量PLL锁定时间的方法有哪几种?2021-05-10 2526

-

2.5GHz PLL锁定检测电路分析实现2010-10-29 609

-

浅谈电解电容检测及选用2009-11-10 1069

-

模拟PLL,模拟PLL是什么意思2010-03-23 2849

-

模拟电路中常用检测仪器及测试方法的研究2011-07-24 1375

-

ADF4xxx系列PLL频率合成器的锁定检测2011-11-29 923

-

详解PLL锁定时间精确测量2018-03-14 8209

-

PLL锁定过程的两个步骤2018-05-11 12518

-

基于电荷泵锁相环技术的电路锁定检测的基本原理和设计实现2020-08-24 4587

-

AN-873: ADF4xxx系列PLL频率合成器的锁定检测2021-03-21 789

-

浅谈CAN总线入侵检测的精度2023-07-12 711

-

pll锁定时间按照频率精度多少来计算2023-09-02 3188

全部0条评论

快来发表一下你的评论吧 !