一文详解提高芯片级封装集成电路热性能的方法

电子说

描述

在便携式电子市场,电源管理集成电路(PMIC)正在越来越多地采用球栅阵列(BGA)封装和芯片级封装(CSP),以便降低材料成本,改进器件的电性能(无焊线阻抗),并且实现更小的外形尺寸。但是这些优势的取得并不是没有其他方面的妥协。芯片级封装的硅片不再直接与用于导电和导热的较大散热板(E-PADs)接触,由于IC基板不再与E-PAD接触,从IC基板到散热印刷电路板(PCB)铜面之间没有高导热性的直接连接,这是性能受到影响的主要原因。本文将讨论在PCB级使用的降低CSP器件工作温度的方法,并通过降低在设计中使用的CSP集成电路热阻来探寻将热量从热源传输到周围环境的方法。通常有多种方式可以提高性能,同时降低工作温度,这可以通过采用新的印刷电路板或者更改现有电路板来实现 。

便携式电子设计中由于尺寸和重量的限制,要求设计人员必须减少电子元器件的尺寸和用于PCB连接其他电子设备的区域大小,为了满足这些需求,采用CSP封装来减小所需要的PCB面积是在设计中所常见的变化。由于总PCB面积减小,可用于扩散热量和部设高功率PCB走线的选项随之减少。而且,QFN封装与一个同等CSP封装进行比较,其散热性能也不匹配。因此,当务之急是要对PCB设计进行优化以使热量从CSP传输至PCB,再由PCB扩散到空气中。测量热传导率的参数是结到周围环境的热阻指标Theta-JA (θJA (℃/W))。

作为参考,在使一个典型的QFN封装E-PAD(3x3mm2)与一个具有0.4mm间距的CSP器件连接时,为了匹配传热所用的面积大小,需要连接将近30个CSP引脚以便维持同等的由E-PAD面积决定的散热能力。对于一个精心设计的PCB,在同一电气负载条件下把相同的硅器件焊接到类似的印刷电路板时,θJA数据大小可从CSP封装的45℃/W到等效QFN封装的25℃/W(来源于IDT P9023无线充电接收器的参考数据),比同等QFN相比,这样的差异意味着CSP将会工作在更高的温度下。一个采用CSP封装的IC在与具有相同功耗的QFN相比时,其散热性能通常仅有后者的一半。因此,对于一个精心计划的PCB设计,如果没有进行合适的补偿,CSP封装的热性能可以很容易地比同等QFN坏两倍。

对于一个封装好的IC,其工作温度通常由三个因素决定:对流、传导和实现一定性能所消耗的功率。在采用热阻参数对于CSP IC进行热分析计算时,应该注意到计算是基于对IC到PCB之间散热通孔(via)数量的估计,每个连接都可形成用于把热量从IC半导体结导出的散热路径。这些估算假定IC安装到由JEDEC标准51所限定的3“×4.5”的固体铜4层印刷电路板上,而在实际应用中,PCB设计所占面积通常比较小,具有切口部和其他不规则形状因素,并且有许多组件、多个路径和电连接,这与JEDEC标准相比会使PCB热性能下降。

设计者面临的一个常见的困境是如何把在IC上产生的热量通过PCB传输到空气中,在散热路径上具有最小的温度下降。

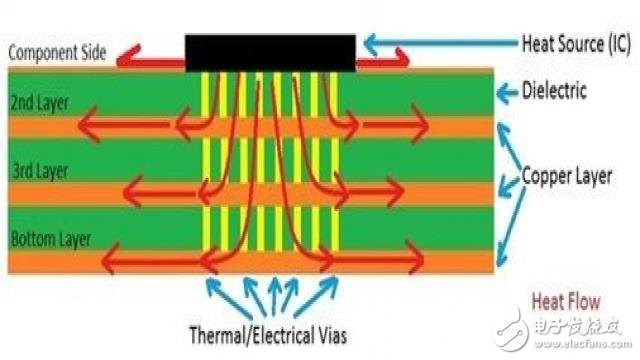

图1:展示热传输的贴装CSP封装器件PCB剖面图

在图1中,每个连接到元器件测端的焊盘以及每个盘上散热孔道(via-in-pad)都可以把芯片产生的热量传输到PCB铜面上。盘上散热通孔的设计以及数量,以及散热通孔直接接触的铜板面积都会影响散热路径的效率。所开发的IC引脚间距会影响孔的大小,而且与可用来经过散热通孔(即铜平面或布线)把热传输到铜表面的铜体积成正比(可把散热通孔认为是中空的传热铜圆柱体)。此外,盘上散热通孔在电镀(electro-plating)完成后,在均匀地处理表面以便放置CSP器件之前需要填充一些非导电或导电材料。通孔填充材料被“注入”入孔,其填充比例常常是制造者根据孔径而优化。用作后端填充(back-fill)通孔的导电填充材料通常具有比铜高的电和热阻性能,由于盘上散热通孔中的铜具有较低的热阻和电阻,所以填充材料对热性能只有很小的影响。另外,大多数的导电材料具有比铜高的热膨胀系数,可能导致通孔壁破裂。由于这些原因,在大批量生产阶段一般只用非导电材料填充,但随着产业技术的进一步发展,导电材料的性能可能开始大幅超越非导电材料,而不会出现良率降低的风险。

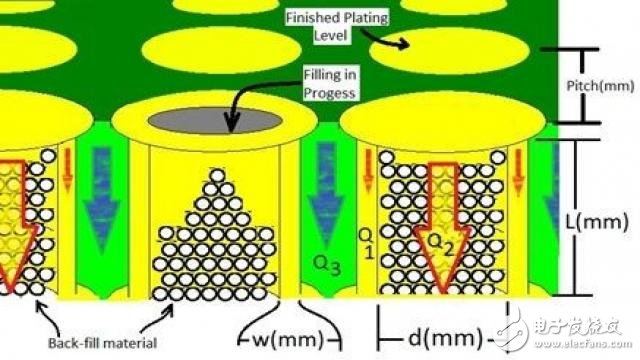

图2:从CSP器件引脚到PCB和盘上通孔的热量传输路径

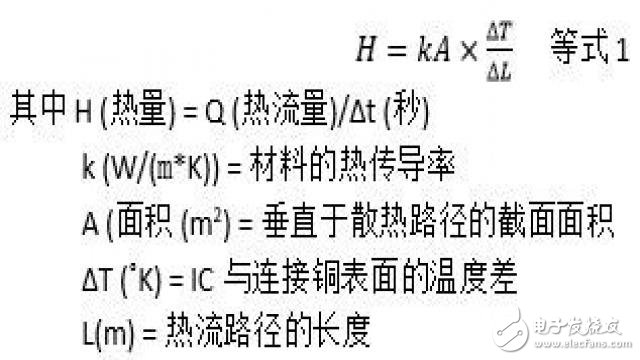

根据一阶热流和热传导原理,影响热流从热源传输到一定体积材料的主要因素是与源之间的距离、横截面(铜连接)以及热源和体积之间的温度差1:

虽然这种简单的近似可能不会解决目前的问题,但它表明,为了传输更多的热量,截面面积应该尽可能大,而热流经过的路径长度则尽可能小。要保持最大限度的热流,重要的是横截面积与到表面(如铜面)的铜连接长度的比值。

通过考察图2可以发现,垂直方向的传能传输受三个平行的热阻影响,Q1为通孔壁的铜,并且是最有效的热传输。Q2为盘上通孔填充材料,Q3则为通过FR-4材料的热流。几种用来优化热流动的方法包括:使通孔直径(d)尽可能大,以便最大限度地增大构成通孔壁的铜的体积(求解圆柱体的体积);在尽可能多的盘上通孔内层上附着尽可能多的铜,并且使这些通孔与平行层连接,以增加铜连接体积(每增加一个通孔连接的内层可以增大可用来散热的体积)。

一旦焊盘上通孔到达被用来完成电连接的PCB层,尽量端接层上的铜布线,使产生的热量有足够多的铜去传导和扩散。在CSP封装下,硅片基底的热阻应比焊盘上通孔的热阻低得多,焊盘上通孔会把热量从PCB上元件侧端传导到任何其它层,CSP封装在整个体积内将近似为等温(isothermal)(上下几度范围)。因此,即使某个引脚的信号只有较小的电流或在IC内部物理位置上没有靠近发热源,每个CSP引脚应当被认为同等地连接到热源,并且能够从IC传输同等的热量。有了这个概念,如果每个CSP引脚连接到同样大小的铜,它们则能够传输相同的热量,连接到CSP的每个连接都应该使用最大面积铜平面或者尽可能厚的铜布线(例如2盎司铜重量而不是1盎司),以便最大限度地提高PCB的散热能力。

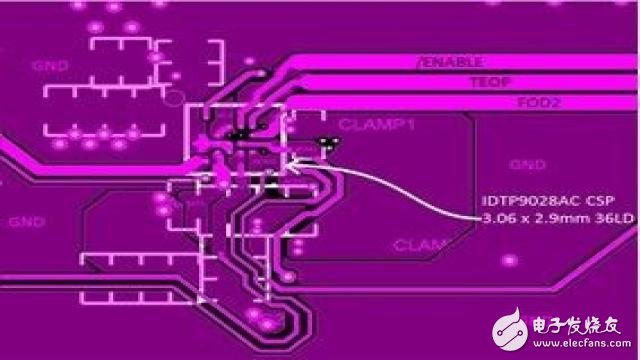

图3:部设在一个4层PCB上的IDT P9028 CSP器件,所示为第3层(中间第2层)

上面图中所示为PCB上从元器件侧开始的第三层,不论布线传导的电流大小,每个盘上通孔的铜表面区域都有连接并且最大化。布线中被保持“薄细”的地方是那些不与盘上通孔直接接触并连接到IC中的部分。这些可以通过较大直径的孔(灰色圆圈)相对于位于CSP封装下方较小直径(较小直径是由于0.4 mm的IC引脚对引脚间距)的盘上通孔来区分,只允许0.254mm(10mil )焊盘和0.127mm(5mil)直径(d,见图2)。在本例的PCB布局中,针对/ENABLE、TS、FOD2的信号每个最多将只有不到1mA的电流,但布线可以故意加宽,以便利用盘上通孔连接所具有的导热能力,盘上通孔还连接到CSP封装。

这里重新考虑一下等式1,热量的流动受热源到散热面或散热层距离(L)的影响。简单地检查一下铜和FR-4的热导率值可以证明,铜(热导率406 (W/(m‘K)) )在传递热量方面比FR-4(热导率为0.1 到 1 (W/(m’K)))优越。然而,当距离(L或电介质的厚度)相对于面积很小时对于一个最佳的PCB设计,顶层PCB的整个表面应该具有近乎均匀的温度,而底层温度将尽可能接近于顶层,这是使热量从PCB电路上传输到空气中(或PCB所处的其它介质)的最佳设计点(最小温度下降),此时PCB两侧都可以作为传热表面。

此外,在使用宽厚的铜平面时,因为铜平面具有高导热性,热量会水平地传输,并且均匀地加热铜平面,使整个区域的温度提高,这有助于在每个平面使热量均匀地分布。一旦实现热量均匀地分布,减小电介质厚度并通过改善PCB层到层之间的传热,层到层之间的表面温度会彼此接近。因此,就CSP芯片的整体工作温度而言,如果所有其他变量保持不变,具有更薄电介质厚度的PCB将胜过具有较厚电介质的PCB。

降低CSP器件工作温度的最终和最有效的方法来是使在PCB元件侧与IC接触的铜的用量最大化。PCB的元件侧由于接近周围环境,是电路板上能够最有效地将热量从PCB散开的一层。任何内层的热量必须经过PCB表面才可以得到扩散。因此必须升高表面的温度以便热流从PCB散开。可以用另一种方法来分析表面铜能够最有效传递热量的事实,即对靠近热源的铜面积与热路径长度的比值进行比较。确定最有意义热路径的关键是找出那些具有最大比值的路径,这些路径是累积性的,可以计算出这些路径的数量并累加,这是计算个体潜在的热阻以及累积传热能力的简单比较值的一种方式。以一个6x6阵列的36引脚CSP器件为例,假设IC有8个GND引脚,而且每个都直接连接到GND面。考虑到较薄的通孔壁以及相对较长的到下一层的距离,在与一个连接到PCB元件侧铜表面的0.254mm长布线进行比较时,通孔的面积长度比(A/L (m2/m)较大。例如,一个0.152mm直径的通孔形成了一个长度为0.47mm的圆柱体,每个无限薄圆筒环将是大约13.9nm(假设通孔壁厚镀层为25μm厚),这将有29μ的热传递比值(A/L)。现在计算一个具有较短侧端布线元件与一个散热平面的热传递比值,长度为0.254mm,含有1盎司铜,宽度为0.254mm,所得到的热传递比值为35μ(A/L)。短的铜布线具有更高的热传递比值,因此比通孔能够传递更多的热量。现在考虑8个 GND通孔,如果CSP器件21个四周引脚中的10个能够连接到宽的铜表面,总的焊盘上通孔热比值将是280μ相对于350μ。因此,与可用于直接连接到铜平面的可用焊盘上通孔数量相比,PCB元件侧的连接有较大的热路径比值,并且通常具有更多可连接到可用散热面的连接。

工作温度是环境温度与传输和扩散所产生的热量而导致温度上升的叠加结果。通过优化PCB设计, CSP器件产生的热量经过传导能够尽可能均匀地扩散到尽可能宽广的区域,致使IC封装的温度、PCB表面的温度、以及环境温度之间具有最小的温度差,可以实现对流效率的最大化,从而实现最佳的热性能。由于CSP封装功率器件没有直接的基板到PCB连接(如QFN封装的E-PAD),热量的流动必须一个引脚到一个引脚地考虑。对于CSP器件,考虑到硅片具有几乎相同的温度(1-2摄氏度以内温差),从每个引脚到基板的热路径几乎是相同的。因此,每个引脚连接都应该仔细检查,并加强铜的连接,以便优化从集成电路到正在开发或者修改的PCB的散热性能。由于外围引脚没有较薄的通孔,而且具有大量的四周引脚,印刷电路板的元件侧是实现热传递的最有效途径。不论节点上的电流大小,所有的四周引脚应该连接有空间所能允许的宽铜布线,也不可忽视电流承载要求。最后,焊盘上通孔可用来把每个内引脚连接到较宽的空间所允许的铜表面或布线,多层设计降低了工作温度也实现了更薄的PCB。

-

集成电路封装资料 PPT下载2009-10-21 0

-

集成电路封装技术专题 通知2016-03-21 0

-

集成电路芯片封装技术的形式与特点2018-08-28 0

-

PCB提高中高功耗应用的散热性能2018-09-12 0

-

一文解读集成电路的组成及封装形式2019-04-13 0

-

集成电路芯片封装技术知识详解2008-05-12 2439

-

集成电路的封装形式及引脚识别2021-03-14 11622

-

了解集成电路的热性能2022-07-28 1559

-

集成电路封装类型有哪些2022-10-09 3981

-

半导体集成电路芯片封装功能介绍及注意事项分析!2022-12-13 2540

-

容泰半导体集成电路芯片级封装项目竣工投产2024-05-31 680

-

实现芯片级封装的最佳热性能2024-10-15 119

-

瑞沃微:一文详解CSP(Chip Scale Package)芯片级封装工艺2024-11-06 1585

-

集成电路封装的发展历程2025-01-03 511

全部0条评论

快来发表一下你的评论吧 !