从平面晶体管到FinFET的演变

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍从平面晶体管到FinFET的演变

在90纳米制程之前,每一代集成电路技术节点的缩放不仅带来了更高的器件密度,还提升了器件性能。然而,当CMOS IC从90纳米发展到65纳米节点时,缩放并未改善器件性能:它只增加了器件密度。这一变化的主要原因是栅氧化层的厚度无法再继续减薄,因为隧道效应引起的泄漏电流成为了一个不可忽视的问题。

平面晶体管的局限性

MOSFET(金属氧化物场效应晶体管)的一个重要性能参数是驱动电流 Id,其与公式 Id∝μ(K/Tox)(W/L) 成正比。其中:μ 是沟道材料的载流子迁移率(对于NMOS为电子迁移率,对于PMOS为孔穴迁移率)。K 是栅极介质的介电常数。Tox 是栅氧化层的厚度。W 是沟道宽度。L 是沟道长度。

如果仅缩小平面MOSFET的特征尺寸,则 W 和 L 会以相同的比例减小,除非 Tox 同样减小,否则驱动电流不会得到改善。为了降低漏电和功耗,供电电压和阈值电压也会偶尔随栅氧化层厚度一起减小。当 Tox 变得非常薄并接近泄漏和击穿极限时,人们不得不寻找其他方法来提高 Id。

高k/金属栅极(HKMG)技术

为了解决栅氧化层厚度限制的问题,人们引入了高介电常数栅介质和金属栅技术(HKMG)。使用高k材料(如HfSiOxNy)替代传统的SiO2栅介质,可以显著增加栅介质的介电常数K,从而形成更薄的有效氧化物厚度(EOT),进一步提高驱动电流。例如,HfSiOxNy的介电常数 K 可以达到20左右,远高于SiO2的3.9。

在45纳米以下技术中引入了HKMG,这有助于减少EOT并进一步提升器件性能。尽管HKMG技术在一定程度上解决了栅氧化层厚度的问题,但随着技术节点的进一步缩小,平面MOSFET的性能提升遇到了瓶颈。因此,业界开始探索新的晶体管结构,FinFET应运而生。

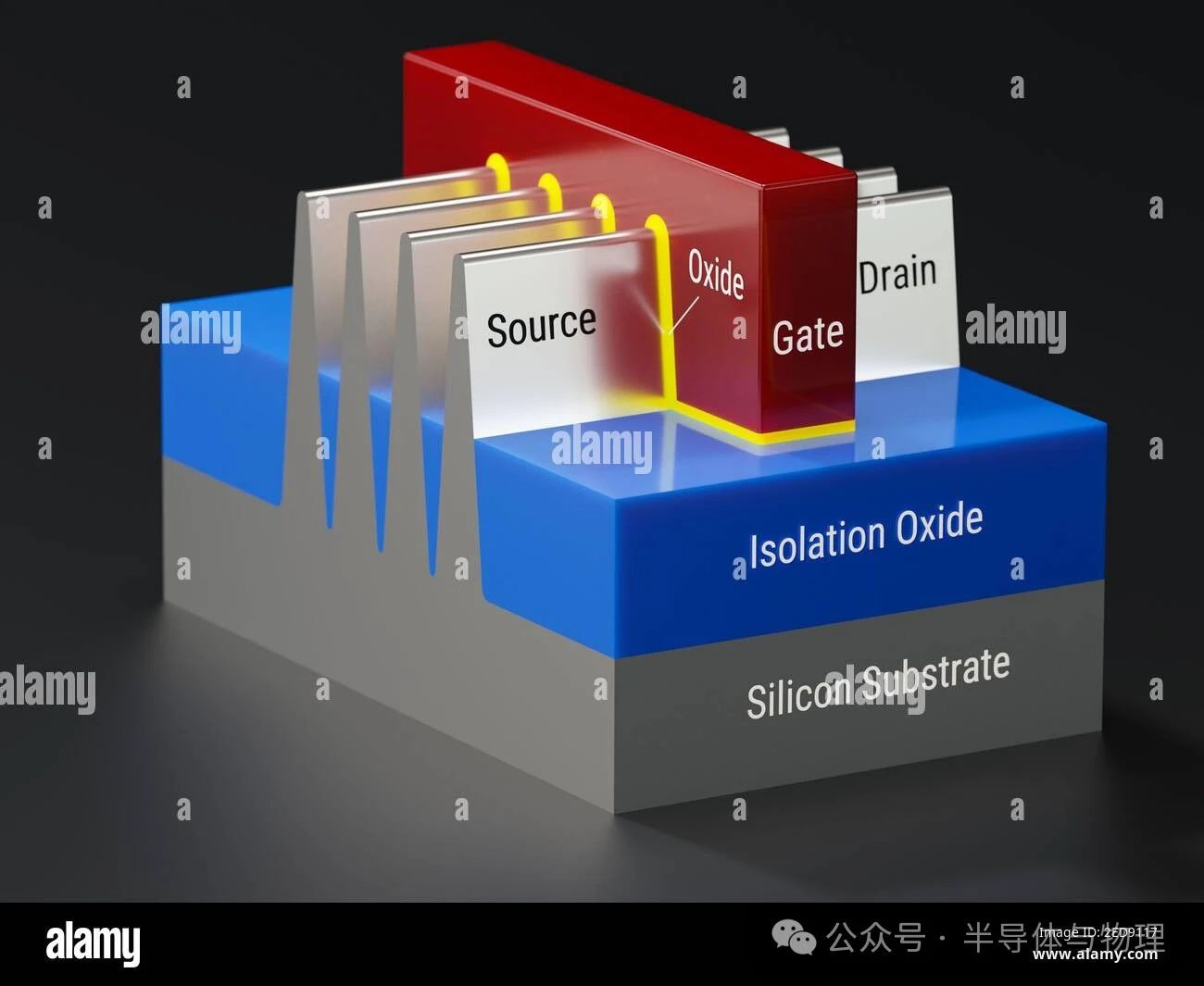

FinFET的结构

平面MOSFET:平面MOSFET的沟道位于一个平面上。

FinFET:FinFET的沟道呈鳍状,沟道被栅极从三个方向包围。

FinFET的优势

增加沟道宽度:FinFET可以在较小的硅表面面积上实现相同的沟道宽度。通过增加鳍的高度,沟道宽度可以进一步增加,因此可以在不缩小器件特征尺寸的情况下进一步提升器件性能。

减少短沟道效应:FinFET的三维结构有助于更好地控制沟道区,减少短沟道效应,提高晶体管的可靠性和性能。

提高驱动电流:FinFET的三面栅结构可以更有效地控制沟道区,减少漏电,提高驱动电流 Id。

FinFET的制造挑战

蚀刻和清洗:如果鳍太高且纵横比过高,蚀刻和清洗鳍而不引起其坍塌将变得非常困难。

STI填充:填充鳍之间的STI(浅沟槽隔离)的无空洞介电薄膜也将变得非常困难。

-

晶体管架构的演变过程2025-07-08 2572

-

FinFET技术在晶圆制造中的优势2025-04-14 1867

-

鳍式场效应晶体管制造工艺流程2025-02-17 3611

-

互补场效应晶体管的结构和作用2025-01-24 5085

-

晶体管是怎么做得越来越小的?2023-12-19 1619

-

探讨晶体管尺寸缩小的原理2023-12-02 2650

-

MOSFET和鳍式场效应晶体管的不同器件配置及其演变2023-02-24 13737

-

全包围栅极结构将取代FinFET2022-08-01 2126

-

FinFET的效用已趋于极限 浅谈晶体管缩放的难题2021-01-25 4066

-

基于FinFET IP的数据转换器设计2019-07-17 2113

-

Finfet技术(3D晶体管)详解2012-08-19 2927

-

晶体管到晶体管逻辑(TTL)、振荡器和滤波器电路2010-03-29 1142

-

TIP41C低频大功率平面晶体管芯片设计2009-12-24 12523

全部0条评论

快来发表一下你的评论吧 !