先进封装中的TSV/硅通孔技术介绍

描述

Hello,大家好,今天我们来分享下什么是先进封装中的TSV/硅通孔技术。

TSV:Through Silicon Via, 硅通孔技术。指的是在晶圆的硅部分形成一个垂直的通道,利用这个垂直的通道注入导电物质,将相同类别芯片或不同类别的芯片进行互连,达到芯片级集成的先进封装技术。

TSV技术中的这个通道中主要是通过铜等导电物质的填充完成硅通孔的垂直电气互连,减小信号延迟,降低电容、电感,实现芯片的低功耗、高速通信,增加带宽和实现器件集成的小型化需求。

在TSV技术之前,芯片之间的连接方式基本都是水平的,TSV的技术让多个芯片可以进行垂直连接,又叫堆叠。Wire bonding(引线键合)和Flip-Chip(倒装焊)的Bumping(凸点)提供了芯片对外部的电互连,通过TSV和RDL(再布线)则提供了芯片内部的垂直和水平方向的电互连。

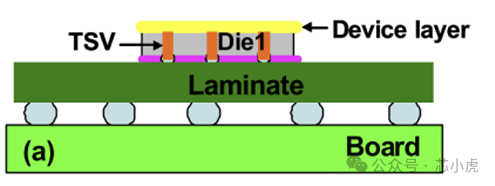

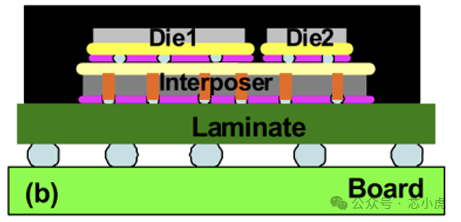

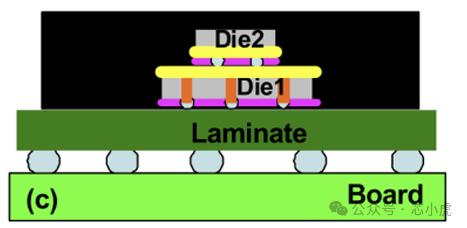

TSV根据应用的构造 ,大致可分为3种:

(a) 垂直的背面连接,无芯片堆叠。TSV位于有源晶粒(active die)中,用于连接至晶圆背面的焊盘(bond pad);

主要特点:技术难度低,适合大规模投入生产应用,例如应用TSV的CMOS图像传感器(CIS)、SiGe功率放大器等。

应用TSV的CMOS图像传感器的好处是

1)使用TSV代替引线键合可以减小图像传感器的尺寸。

2)简化了图像传感器的晶圆级封装(WLP)。WLP工艺的第一步是将玻璃晶圆附着到图像传感器的正面,防止光刻胶(抗蚀剂)微透镜在组装过程中受到损坏和污染,然而安装好玻璃晶圆后会使从晶圆正面到焊盘的连接途径受阻,TSV通过简化晶圆级封装,对此问题提供了简易的解决方法。

(b) 2.5D 封装。晶粒(die)连接至硅中介层(interposer),TSV在中介层中;

主要特点:技术难度中,与垂直的背面连接相比,2.5D 先进封装的硅中介层需要更小的 TSV 间距(≤50 μm),因此需要更先进的TSV工艺。

现场可编程门阵列(Field Programmable Gate Array,FPGA)器件是最早使用硅中介层的产品之一:硅中间层可以使芯片间密切连接,整合后的结构看起来像单个大尺寸的FPGA芯片,解决了早期直接构建单个大尺寸FPGA芯片的技术难题。

(c) 3D 封装。TSV位于有源晶粒中,用于实现芯片堆叠。

主要特点:技术难度高,存储器堆叠是首批应用3D堆叠TSV结构的产品之一,和2.5D封装中硅中阶层对TSV间距的需求相似,但实际应用中难度更高,例如对DRAM设备的宽I/O要求。 使用宽 I/O的DRAM 和芯片堆叠的优势包括封装高度降低40%,功耗降低50%,带宽增加6倍。

-

硅通孔封装工艺流程与技术2023-05-08 5916

-

先进封装关键技术之TSV框架研究2023-08-07 3564

-

简单介绍硅通孔(TSV)封装工艺2023-11-08 7424

-

一文详解硅通孔技术(TSV)2024-01-09 23785

-

硅通孔电镀材料在先进封装中的应用2025-10-14 7091

-

硅通孔(TSV)电镀2021-01-09 3840

-

3D封装与硅通孔(TSV)工艺技术2011-12-07 2903

-

中微推出用于3D芯片及封装的硅通孔刻蚀设备Primo TSV200E(TM)2012-03-15 1846

-

详解TSV(硅通孔技术)封装技术2016-10-12 18434

-

什么是TSV封装?TSV封装有哪些应用领域?2018-08-14 93031

-

技术资讯 I 3D-IC 中 硅通孔TSV 的设计与制造2022-11-17 2501

-

硅通孔TSV-Through-Silicon Via2023-07-03 5727

-

先进封装中硅通孔(TSV)铜互连电镀研究进展2023-09-06 2689

-

3D-IC 中 硅通孔TSV 的设计与制造2023-11-30 2611

-

芯片先进封装硅通孔(TSV)技术说明2025-01-27 4467

全部0条评论

快来发表一下你的评论吧 !