TSV三维堆叠芯片的可靠性问题

描述

TSV 三维封装技术特点鲜明、性能好、前景广阔, 是未来发展方向,但是 TSV 堆叠芯片这种结构和工 艺复杂性的提高,为三维封装的可靠性控制带来了 挑战。主要体现在以下 4 个方面 :(1) TSV 孔质量和 信赖性保证难度大 ;(2) 多层芯片堆叠结构的机械稳 定性控制难度大 ;(3) 芯片间热管理和散热解决方案 复杂 ;(4) 芯片测试和故障隔离、定位困难。

2.1 TSV 孔的质量和可靠性问题

作为三维集成电路中的垂直互连通道,TSV 孔 的质量和可靠性对系统性能至关重要。随着集成度 的不断提升,TSV 孔的关键尺寸正在向着超高纵横 比 ( 深宽比大于 20:1) 和微米级甚至亚微米级孔径 ( 小 于 10μm) 发展。这给 TSV 孔的制造工艺带来了巨 大挑战。当前 TSV 孔存在的主要质量与可靠性问题 集中在以下 4 个方面。

(1)TSV 孔的形状和侧壁角度难以精确控制 ;

(2) 绝缘层与阻挡层的保形性与界面粘附力难以保证 ;

(3)TSV 孔内部难以实现无空洞的充填 ;

(4)TSV 周边多余的填充材料难以清除。

TSV 孔存在的上述工艺缺陷会导致其在后续操 作和使用中出现两大类可靠性问题 :

(1)TSV 的绝缘层不连续或有缺陷,会使 TSV导体与芯片的体硅之间发生漏电,或者 TSV 和地之间的短路可能会导致功能异常。

(2)TSV 通孔中或连接通孔导电材料存在空洞, 空洞可以随着时间推移而增长,从而导致开路。

这两类故障机制削弱了 TSV 的导电可靠性 , 是 影响三维集成电路可靠性的主要因素,也是当前研 究的重点难题。

2.2 三维堆叠过程中的质量问题

TSV 堆叠芯片在进行三维封装制造过程中,一 般包括多个物理平面间互连堆叠起来工艺,这一堆 叠的过程可以由晶圆—晶圆 (Wafer to Wafer,W2W)、 芯片—晶圆 (Die to Wafer,D2W) 或芯片—芯片 (Die to Die,D2D) 等方式实现,制造过程比传统 2D 封装 的集成电路复杂,也更容易产生缺陷和失效。当前 的质量问题主要有以下 5 个方面。

(1) 电应力问题 :TSV 实质是穿过硅衬底的金属 线 ( 一般采用 Cu),其周围需要采用隔离介质 ( 一般 采用 SiO2) 防止 Cu 离子向硅芯片扩散。但这就形成 了金属—氧化物—半导体 (MOS) 结构。这个 MOS 结构电容会导致 :TSV 信号通过耦合的形式干扰周围器件,产生信号失真 ;MOS 电容通道中的漏电流 增加,提高了芯片的静态功耗。

(2) 热应力问题 :在 TSV 制作过程中,首先需 要在硅晶圆上刻蚀窄而深的孔,然后填充上隔离材 料,最后电镀 Cu。TSV 和硅片经多次热循环,最 后的退火和冷却过程会给整个结构带来巨大的温差 (250 ℃ )。由于金属材料尤其是铜 (Cu) 和硅片热膨 胀系数 (CTE) 的不匹配,会在 TSV 周围的硅衬底内 引入很大的热应力,从而影响热载流子迁移率、器 件性能以及长期可靠性。

(3) 机械应力问题 :TSV 是使芯片叠层连接到其 他叠层和单元。所有这些界面可能来自不同的芯片, 在键合过程中,机械应力的存在使芯片间界面开裂 或 TSV 垂直互连处键合材料的失效,封装结构的机 械稳定性降低,从而导致 TSV 堆叠芯片的短路或开 路失效。

(4) 热管理问题 :TSV 三维集成电路通过垂直堆 叠,极大地提高了单位面积的芯片密度,这导致相 比二维集成电路,三维集成电路中的热密度急剧增 加。叠加使用的垂直键合材料本身热导率低 , 难以进 行有效的热传递,尤其是距离散热器最远的顶层芯 片存在严重的热累积问题,热密度过高会导致芯片 性能衰减、加速老化以及潜在的永久失效。

(5) 电性能测试问题 :在 TSV 三维堆叠封装结 构中 , 多个芯片被垂直堆叠和互连,这使得确保每个 芯片的电性能符合规范,以及测试最终堆叠后芯片 的整体电性能变得非常具有挑战。主要的测试难点 包括 :堆叠前各个裸片的测试重复性与可靠性较差 ;堆叠芯片后信号无法直接进行探针测试 ;故障的定 位与隔离难度大。

目前国际上有 JEDEC 于 2009 年发布的 JEP 158— 2009 “3D chip stack with through-silicon vias(TSVS) :Identitying,evaluating and understanding reliability interactions ”(《硅通孔 3D 堆叠芯片 可靠性的相互 作用的识别、评估和理解》),专门针对 TSV 三维封 装的可靠性评估与保障。

该标准提出根据 TSV 三维堆叠芯片产品、工艺 的实际情况,由 TSV 三维堆叠芯片生产商编制试验 方案,确定采用的试验方法、试验条件、抽样数、 失效判据以及需关注的特定失效模式。

对 TSV 三维封装进行可靠性验证试验时,可以 采用专门设计的试验结构或直接使用产品级 TSV 堆 叠芯片。与产品级芯片相比,精心设计的试验结构 在进行失效检测和分析时具有明显的优势 :试验结 构通过精确控制敏感区域,可以有效放大某一失效 机制的特征 ;试验结构针对特定缺陷设计相应的传 感与监测机制,可以实现目标的实时检测 ;试验失 败后,可以通过预埋的分析单元让失效部位得以快 速准确地定位和分类。

相比之下,在产品级芯片的电参数测试中检测 出异常情况,要准确定位与识别 TSV 相关的故障机 制几乎是不可能的。因此,合理设计的 TSV 专用试 验结构,将大大提高工艺流程中缺陷检测效率与质 量提升速度,是开发与验证 TSV 制程的重要手段。

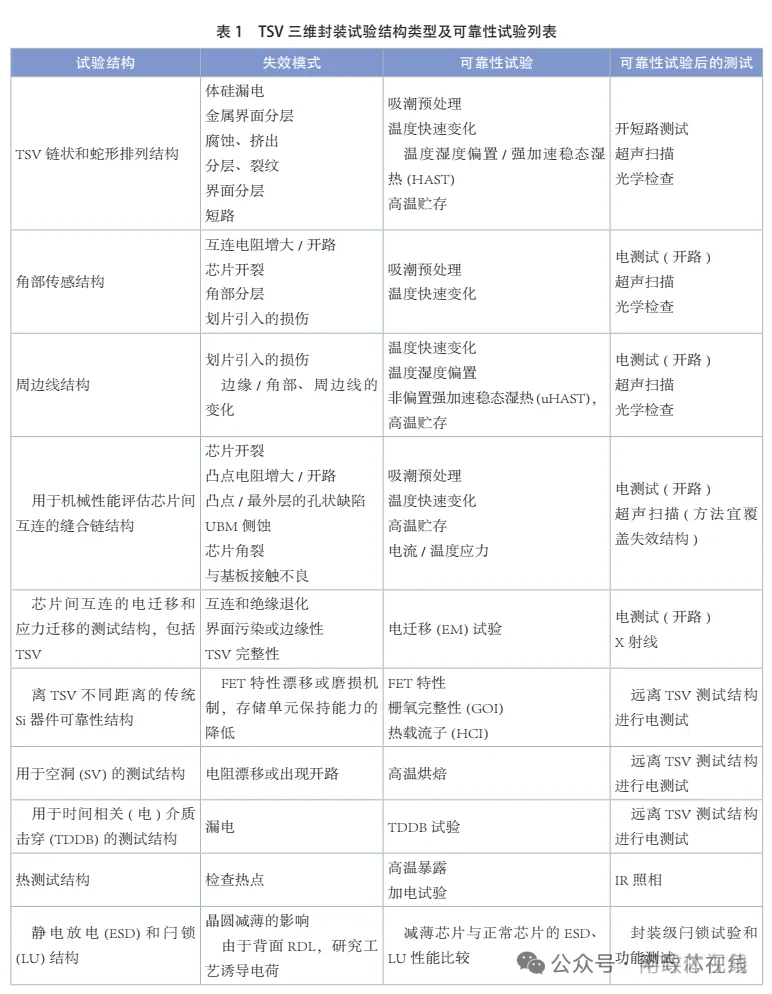

根据 TSV 堆叠芯片工艺中失效模式,JEP 158— 2009 给出了可靠性应力以及推荐的检测方法,见下表。

为了有针对性地检测 TSV 三维封装的故障模 式 , 可以设计特定的试验结构 ( 见表 1) 进行可靠性验证试验。这些试验结构通过精心布局,可以放大 某一故障机制的特征。例如,链状或蛇形的 TSV 结 构,可以用于检测“体硅漏电”“金属界面分层”等 电迁移故障。对专门设计的试验结构进行吸潮预处 理、温度快速变化、温度湿度偏置 / 强加速稳态湿热 (HAST)、高温贮存等试验,完成后再进行开短路测试、 超声扫描、光学检查,检查导电性能的损伤,结构 内部的空洞缺陷以及界面的分层或裂纹。通过电学 测试与物理分析的结合,可以明确对应特定可靠性 试验后,TSV 结构中的缺陷类型、位置、失效机制等, 从而对工艺过程进行优化。

通过这种针对性的可靠性验证方案,让企业充 分考量并验证 TSV 三维封装产品中的潜在故障机制、 故障模式,是保证产品质量的有效手段。JEP 158— 2009 标准的制定可以帮助制造商和用户更好地了解 TSV 技术的可靠性和相互作用,改善 TSV 技术的可 靠性和稳定性,推动了三维封装技术的工业化进程 与风险控制,该标准对于 TSV 三维堆叠芯片的制造 和应用具有重要的指导意义。

但是 JEP 158—2009 也有局限性,如 :没有给出 明确的可靠性试验类型选取参考 ;缺乏针对不同故 障机制的标准化试验条件推荐 ;未规定明确的判定 试验结构失效的量化标准。

这些内容的缺失会导致不同 TSV 堆叠芯片生产 企业,在确立可靠性验证方案时存在明显差异 :采用 的试验类型及严苛条件可能不同 ;判定试验结构失 效的界限不一致。因此,这将导致不同厂商的 TSV 产品可靠性水平与工艺成熟度难以在行业内实现 统一。

-

世界级专家为你解读:晶圆级三维系统集成技术2011-12-02 10429

-

三维设计应用案例2019-07-03 2592

-

Handyscan三维扫描仪机械零部件三维扫描抄数服务2020-07-21 1319

-

芯片堆叠的主要形式2020-11-27 4791

-

智能芯片的三维内存解析2020-12-24 2672

-

半导体封装篇:采用TSV的三维封装技术2011-12-23 5494

-

高通和英特尔介绍用在移动SOC的TSV三维封装技术2013-01-22 1921

-

三维芯片的垂直互连2017-11-22 1149

-

基于三维集成技术的红外探测器2022-04-25 3585

-

华为公布两项关于芯片堆叠技术专利2022-05-10 5325

-

基于弹性互连的三维射频前端模组的设计2022-11-21 1671

-

三维堆叠封装新突破:混合键合技术揭秘!2024-11-13 4183

-

基于TSV的三维集成电路制造技术2025-07-08 2410

-

基于TSV的减薄技术解析2025-07-29 2083

-

三维集成电路的TSV布局设计2025-08-25 2889

全部0条评论

快来发表一下你的评论吧 !