既然MOSFET栅-源阻抗非常大,为什么设计驱动MOS电路的栅极电流还要大?1200字说清楚

既然MOSFET栅-源阻抗非常大,为什么设计驱动MOS电路的栅极电流还要大?1200字说清楚

描述

Part 01

前言

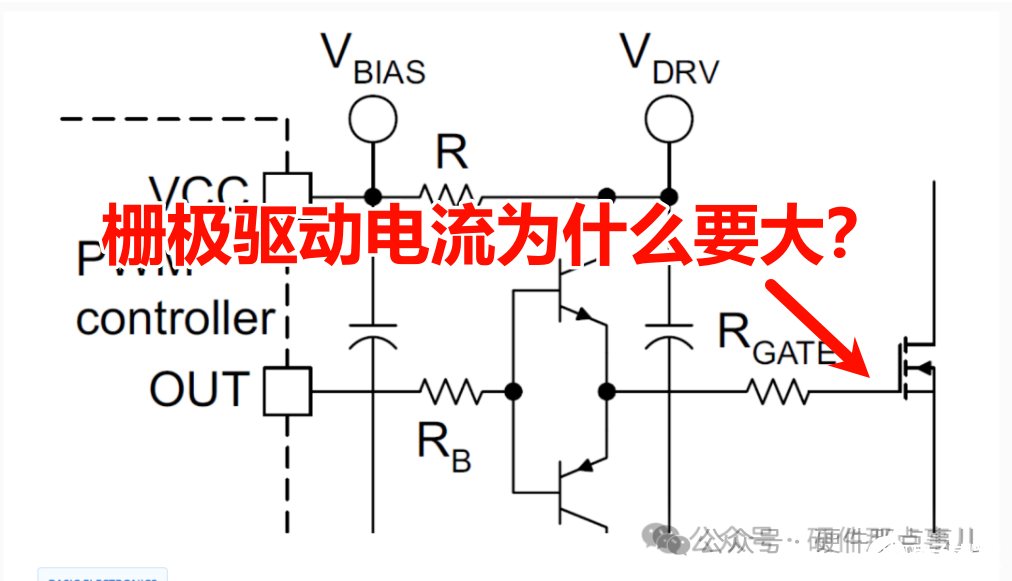

三极管是流控型器件,通过电流控制三极管的工作区,而MOSFET与之相对是压控型器件,栅-源阻抗非常大,我们一般认为MOSFET栅-源工作电流可以忽略,那既然MOSFET是压控型器件,为什么设计MOFET驱动电路时,栅极驱动电流要大呢? 要想回答上面的问题,就不得不聊聊MOSFET中的米勒平台电压,也就是Miller Plateau Voltage,它是指在MOSFET开关过程中,由于MOSFET寄生电容的米勒效应,MOSFET的栅极-源极电压 (VGS) 会保持在一个固定电压水平的现象。这一现象与MOSFET的寄生电容、以及驱动电路密切相关。

Part 02

米勒效应的基本原理

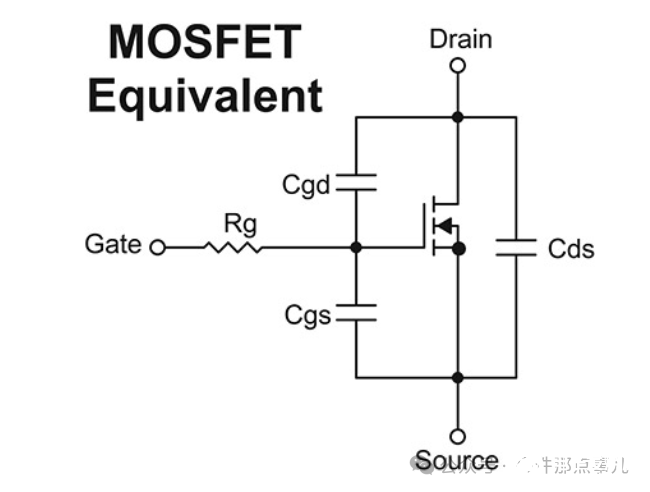

MOSFET的寄生电容包括栅极-漏极电容 (Cgd) 和栅极-源极电容 (Cgs)。虽然栅源电容很重要,但栅漏电容实际上更重要。并且更难以处理,因为它是一个随电压变化的非线性电容。其中,Cgd是导致米勒效应的主要因素。当MOSFET开关状态发生变化时,漏极电压 (VDV) 会发生大幅度的变化,Cgd的存在导致栅极需要提供更多的电荷或移除更多的电荷来应对这种变化。

1.开通过程:

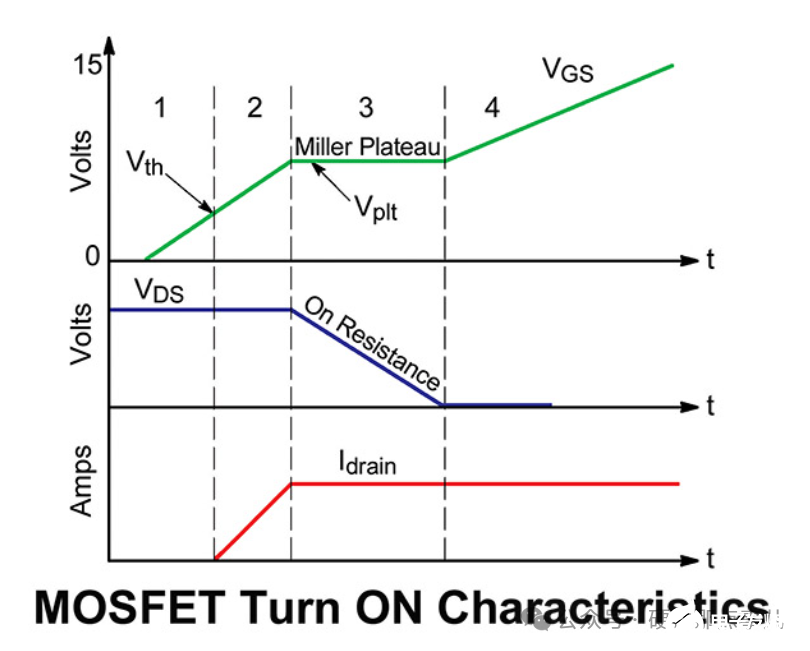

t1:gs电容开始充电,gs电压开始抬升,电压达到Vth之前,没有电流流过D。栅极驱动电压 (VGS) 逐渐上升并达到阈值电压 (Vth) 。

t2:当栅极驱动电压 (VGS) 超过MOSFET的阈值电压 (Vth) 后,Cgs继续充电,Vgs继续抬升,Ids电流成比例增大,在此阶段由于Rds较大,所以虽然Cgd也能通过G->D->S进行充电,但是电流较小,可以忽略.

t3:之后drain电流达到Id,Vd电压不再和VDD保持一致,并开始下降,Id不再发生变化,此时Vg电压也不再变化,此时Ig电流基本都用于给Cdg充电。在此过程中,漏极电压 (VDV) 开始下降,导致Cgd两端的电压变化,从而引发米勒效应。由于栅极电流 (IG) 的一部分用于驱动Cgd,VGS会暂时停止增加,形成“米勒平台”。

t4:Vd电压降低为:Id*Rds(on),MOS开始进入饱和区,此时Vd不再受传输特性限制(与Id有关),并开始自由增加。到达t4时间点,Vg电压达到gate电流源电压。在此阶段,Vgs正比于Q=I*t(I恒定,由恒流源提供),t3之后的充电不是用于MOS开关的充电,简单来说就是过充,是由驱动电路导致的,这是由于Vgate的驱动电压一般会高于完成MOS由关到开的切换所需最小电压。

2.关断过程:

在关断时,漏极电压 (VDV) 开始从低电位上升到高电位,同样引发米勒效应。

栅极电压 (VGS) 在米勒平台电压附近保持稳定,直到漏极电压变化完成。

Part 03

总结

通过上面的分析,我们发现米勒平台的持续时间有很多影响,米勒平台形成的根本原因是MOSFET的寄生电容导致的,而电容的电荷Q=I*t,在Q一定的情况下,I越大,t就越小,这个I就是MOSFET的栅极驱动电流。 所以米勒平台的持续时间取决于栅极驱动电流和寄生电容的值。驱动电流越大,平台持续时间越短。所以我们可以通过选择合适的栅极驱动器,提供足够的电流以快速跨越米勒平台,米勒平台期间的开关损耗是总损耗的重要组成部分,特别是在高频开关应用中减少米勒平台持续时间,来减小MOSFET的开关损耗。这也是为什么MOSFET明明是压控型器件,倒是我们还是设计MOSFET驱动电路时还是要追求栅极驱动电路要大的原因。

并且米勒效应引起的漏极电压变化可能导致电磁干扰(EMI)问题。在设计中可以通过缓冲电路或栅极电阻优化开关波形,所以如果你发现你的MOSFET栅极波形有振荡,就需要考虑了。

审核编辑 黄宇

-

开关电源常用的MOSFET驱动电路2017-01-09 8196

-

电源设计经验之MOS管驱动电路篇2018-10-22 1917

-

MOS管驱动电路设计经验分享2018-10-23 3212

-

浅析功率型MOS管电路设计的详细应用2018-12-10 2696

-

分享几个模块电源中常见的MOSFET驱动电路2019-02-21 3456

-

选定电源IC与MOS管之后,如何选择合适的驱动电路?2019-09-25 4020

-

MOS管的基础知识/主要参数/应用电路2021-01-20 6608

-

MOS管的开关电路中栅极电阻和栅源极级间电阻是怎么计算的?2021-04-19 9786

-

测量SiC MOSFET栅-源电压时的注意事项2022-09-20 20040

-

低栅极关断阻抗的驱动电路2018-01-10 850

-

不好理解的「继电器线圈电压」,本文都说清楚了2019-07-02 19862

-

MOSFET栅极驱动电流计算和栅极驱动功率计算2022-11-11 1757

-

MOSFET栅极电路电压对电流的影响?MOSFET栅极电路电阻的作用?2023-10-22 4130

-

MOSFET的栅源振荡究竟是怎么来的?栅源振荡的危害什么?如何抑制2024-03-27 3623

-

mos驱动芯片失调电压的产生原因2024-07-14 2122

全部0条评论

快来发表一下你的评论吧 !