可编程晶振的锁相环原理

描述

锁相环(Phase-Locked Loop,PLL)是一个能够比较输出与输)入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号。而锁相环(Phase-Locked Loop,PLL)技术在可编程晶振中扮演着关键角色,以下是对可编程晶振中锁相环技术的详细讲解:

一、锁相环技术的基本原理

1、锁相环是一种利用相位同步产生的电压去调谐压控振荡器(Voltage Controlled Oscillator,VCO)以产生目标频率的负反馈控制系统。它根据自动控制原理,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪。

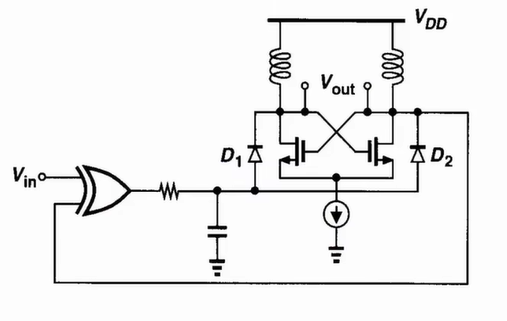

2、锁相环通常由鉴相器(Phase Detector,PD)、滤波器(Loop Filter,LF)和压控振荡器三部分组成前向通路,由分频器组成频率相位的反馈通路。锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路把振荡器输出信号的频率、相位反馈到鉴相器。

3、在锁相环工作过程中,当输出信号的频率成比例地反映输入信号的频率时,输出电压与输入电压保持固定的相位差值,这样输出电压与输入电压的相位就被锁住了。

二、锁相环技术在可编程晶振中的应用

1.实现频率合成与转换

锁相环技术能将晶振产生的原始固定频率信号,通过倍频、分频等操作,合成各种不同的目标频率信号。它利用一个参考时钟信号与压控振荡器(VCO)输出信号的相位差来调整 VCO 的频率,当相位差为零时,VCO 的输出频率就锁定在参考时钟信号频率的整数倍或分数倍上。使得可编程晶振能根据不同设备和系统的需求,提供多种频率选择,大大增强了晶振的通用性和灵活性。

2.频率精度和稳定性

锁相环通过不断监测和调整 VCO 的输出频率,使其与参考时钟信号保持精确的相位和频率同步。即使受到外界因素(如温度、电源电压波动等)的干扰,导致 VCO 频率发生偏移,锁相环也能迅速检测到并进行调整,将频率偏差控制在极小范围内。确保了可编程晶振输出频率的高精度和高稳定性。

3.实现低抖动时钟输出

时钟信号在周期上的短期不稳定性,锁相环技术通过其反馈控制机制,对 VCO 输出信号的相位噪声进行抑制和滤波。它能够将输入参考信号的低抖动特性传递到输出信号上,同时对 VCO 自身产生的抖动进行有效衰减。

4、可调频率

通过调整锁相环的控制输入,可以实现对可编程晶振输出频率的精确控制,使其适应不同的工作模式或通信标准。

5、相位同步

在通信系统中,锁相环用于确保发送和接收端的时钟信号是相位同步的,从而确保数据传输的准确性。这对于可编程晶振在通信领域的应用尤为重要。

6、抑制噪声

锁相环通过反馈机制有助于抑制可编程晶振的相位噪声和频率噪声,提高系统的整体性能。

-

基于可编程逻辑芯片和CPU实现数字锁相环频率合成器的设计2020-07-23 2236

-

可编程晶振都有什么频率的呢?分享3个挑选可编程晶振的技巧2024-07-18 2332

-

可编程有源晶振是由什么制造的呢?是怎样的存在?2016-06-06 3420

-

可编程晶振怎么调整频率?2016-11-20 6844

-

PVA0865AF-LF锁相环2021-04-03 1071

-

LabVIEW锁相环(PLL)2022-05-31 8100

-

可编程硅荡器SITIME2011-06-08 2039

-

TMS320C6474 DSP 软件可编程锁相环(PLL)控制器2018-04-16 1269

-

EE-153:ADSP-2191可编程锁相环2021-05-21 822

-

分享 | 可编程晶振芯片几个知识点2024-01-09 2063

-

SG-8201CG可编程晶振在平板电脑中的应用2024-07-12 953

-

可编程晶振的优点和缺点2024-09-30 1735

-

TMS320C6000 DSP软件可编程锁相环控制器指南2024-12-24 431

-

可编程晶振的关键技术——锁相环原理讲解2024-12-30 1346

-

爱普生(EPSON) 常规可编程晶振2025-01-13 1391

全部0条评论

快来发表一下你的评论吧 !