Verilog中signed和$signed()的用法

描述

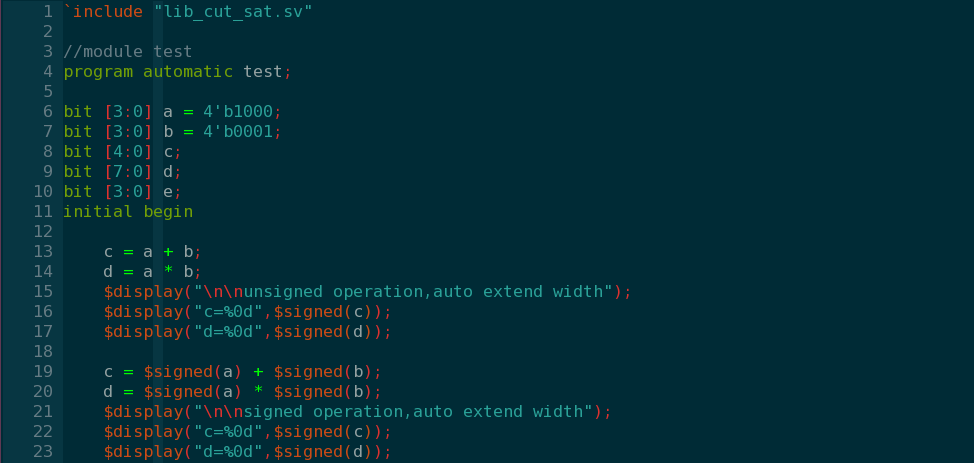

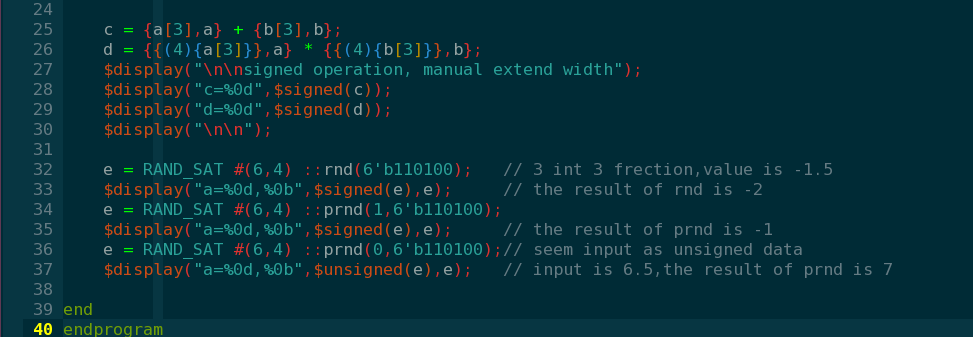

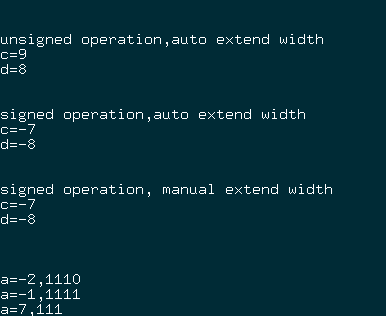

1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()任务来强制转换数据,那么signed的修饰是为什么呢,是为了区分有符号数和无符号数的加法和乘法吗?其实不是的,因为有符号数和无符号数据的加法强结果和乘法器结构是一样的,signed的真正作用是决定如何对操作数扩位的问题。

2、verilog中的加法和乘法操作前,会先对操作数据扩位成结果相同的位宽,然后进行加法或者乘法处理。比如a/b都为4位数据,c为5位数据,c = a + b,这个运算的时候会先把a和b扩位成5位,然后按照无符号加法进行相加。a/b没有被signed修饰的时候会按照无符号数的扩位方式进行扩位,即高位补0,加法的结果当然也是a、b为无符号数相加的结果。

3、如果想把a、b作为有符号数来相加,那么就得在a/b数据定义的时候用signed修改,或者在计算的时候用$signed()来修饰,这样在c = a + b,这个运算开始的扩位就会按照有符号数的方式进行扩位,在高位补符号位,加法得出的结果就是a、b视为有符号数的结果。当然c要视为有符号数据。

$signed()函数

返回有符号的值,值得注意的是verilog中的负数其实是{1’b1,pos_num},而并非高级语言中的补码。使用中最好通过增加$signed{1’b符号,正数}来实现转换以避免错误。

此外在对signed wire 或signed reg 赋值时,右侧的所有变量最好全部加上$signed函数转换,以防止遗漏,造成数据错误

signed变量移位操作时最好使用<<<和>>>,防止对符号位进行操作,导致数据出错

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- Verilog

-

typedef volatile signed short什么意思2013-07-18 7358

-

verilog 问题2014-02-26 3360

-

使用HEW程序链接时提示“16-bits signed value is out of range -32768 32767”是什么原因?2020-05-19 3029

-

verilog中generate语句的用法分享2020-12-23 3307

-

ieee.std_logic_signed.all和ieee.std_logic_unsigned.all同时用出现报错怎么解决?2021-06-23 4296

-

资料下载:HDL中的unsigned与signed2021-07-02 1280

-

HDL语言中的unsigned与signed的主要区别是什么2021-09-24 2097

-

HarmonyOS下载至真机报错App Launch: No signed HAP detected的解决方法2022-05-11 2015

-

浅析System Verilog中的整数数据类型2022-10-11 4093

-

verilog的signed类型有哪些?2020-01-30 6522

-

verilog中的initial语句说明2021-05-31 1024

-

为什么signed_vector的-128结果中间有很多空格?2023-09-02 996

-

verilog function函数的用法2024-02-22 8370

-

verilog inout用法与仿真2024-02-23 4852

全部0条评论

快来发表一下你的评论吧 !