资料下载

×

高精度多相时钟发生电路设计

消耗积分:0 |

格式:rar |

大小:0.28 MB |

2018-03-15

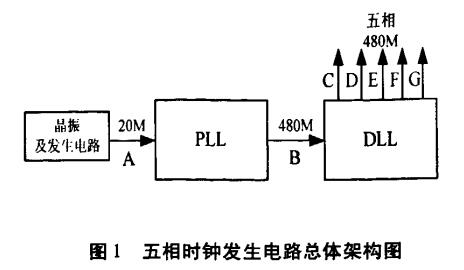

本文设计了一种新颖的单片集成、适用于高速串行通信接口接收端和数据恢复电路的等间距高精度五相时钟发生电路.基于负反馈动态调整原理和数字化的模拟电路设计技术,电路采用TSMC( Taiwan Semiconduc-tor Manufactunnl; Company Ltd)的CMOSO.25um工艺设计和后仿真,实验结果表明:时钟发生电路可正确输出五相时钟,周期均为2.08 m(频率480 Mbpe);相互间隔0.416us,抖动为35 ps,锁定时间为1.8us,满足高速串行通信接口接收端和数据恢复电路对五相时钟的要求.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章