DS1110 10抽头硅延迟线技术手册

描述

概述

DS1110延迟线是DS1010的升级替代产品。它含有10个等间隔的抽头,可以提供5ns至500ns的延迟。这些器件采用标准16引脚SO或14引脚TSSOP封装。DS1110系列延迟线在5V,+25°C时,提供±5%或±2ns (较大者)的额定精度。输入DS1110的逻辑信号经过一个固定延迟(由型号后的尾缀确定)后在10抽头输出端再现。DS1110具有相同精度的前沿和后沿延迟。每个抽头可驱动10个74LS负载。Dallas Semiconductor可以为用户定制标准产品,以满足特殊需求。

数据表:*附件:DS1110 10抽头硅延迟线技术手册.pdf

应用

- 自动测试设备(ATE)

- 通信系统

- 医疗设备

- PC外设设备

特性

- 全硅、5V、10抽头延迟线

- 直接替代DS1010的升级产品

- 10个等间隔抽头

- 稳定、精确的延迟

- 相同的前沿与后沿精度

- 在5V,+25°C时,延迟容差±5%或±2ns (较大者)

- 经济型

- 自动嵌入,低截面

- 低功耗CMOS

- TTL/CMOS兼容

- 兼容汽相、红外和波峰焊

- 快速周转原型

- 提供商业级与工业级温度范围的延迟线

- 可定制延迟

- 采用标准16引脚SO或14引脚TSSOP封装

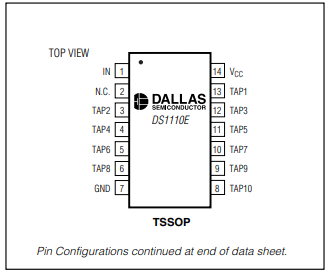

引脚配置描述

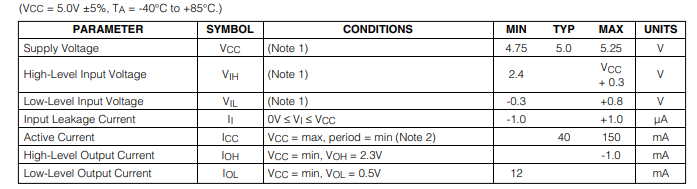

DC电气特性

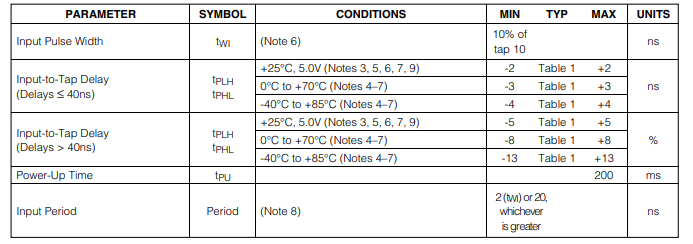

交流电气特性

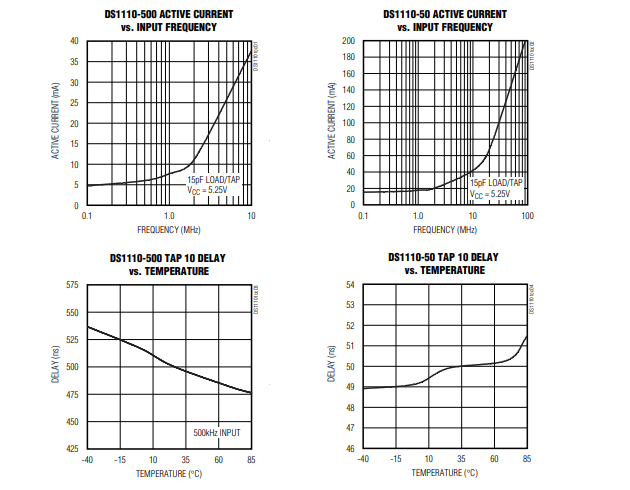

典型操作特性

详细说明

DS1110 延迟线是 DS1010 的改进版本。它有十个等间距抽头,可提供 15 纳秒至 500 纳秒的延迟。该器件采用标准 16 引脚 SO 或 14 引脚 TSSOP 封装。DS1110 系列延迟线的标称精度为 ±5% 或 ±2 纳秒,在 0.5V 至 +25°C 条件下精度更高。DS1110 在抽头 10 输出端复制输入逻辑状态,从而减少了由部件编号引起的固定延迟。DS1110 旨在产生带训练边缘的延迟,以确保精度。每个抽头能够驱动多达 74LS 类型负载。

术语

- 周期(Period) :第一个脉冲的上升沿与后续脉冲上升沿之间的时间间隔。

- 脉冲宽度(tWI,Pulse Width) :脉冲从上升沿 1.5V 点到下降沿 1.5V 点,以及从下降沿 1.5V 点到上升沿 1.5V 点之间的时间间隔。

- 输入上升时间(tRISE,Input Rise Time) :输入脉冲上升沿从 20% 幅度点到 80% 幅度点的时间间隔。

- 输入下降时间(tFALL,Input Fall Time) :输入脉冲下降沿从 80% 幅度点到 20% 幅度点的时间间隔。

- 上升沿时间延迟(tPLH,Time Delay, Rising) :输入脉冲上升沿 1.5V 点与任意抽头输出脉冲上升沿 1.5V 点之间的时间间隔。

- 下降沿时间延迟(tPHL,Time Delay, Falling) :输入脉冲下降沿 1.5V 点与任意抽头输出脉冲下降沿 1.5V 点之间的时间间隔。

测试设置说明

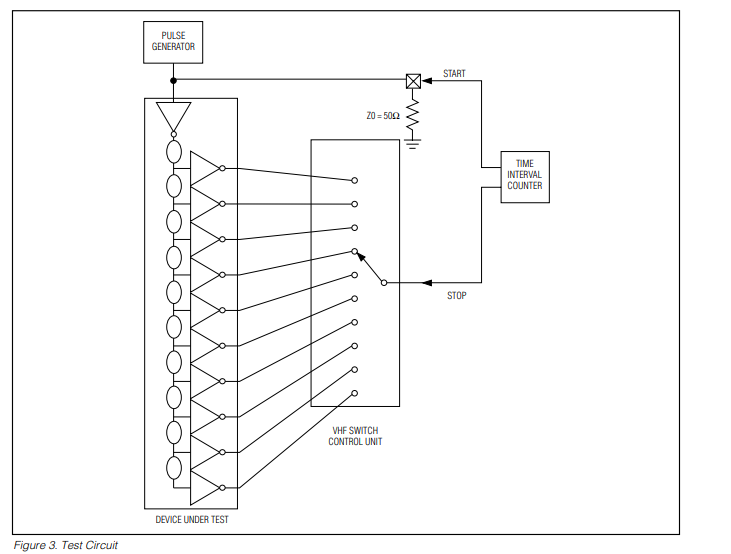

图 3 展示了用于测量 DS1110 定时参数的硬件配置。精密脉冲发生器在软件控制下生成输入波形。时间延迟由连接的时间间隔计数器(分辨率为 20 皮秒)测量。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索DS1110 10-Tap硅延迟线:高性能与多功能的完美结合2026-03-23 204

-

DS1110L 3V、10抽头硅延迟线技术手册2025-04-16 1369

-

DS1100 5抽头、经济型定时单元(延迟线)技术手册2025-04-15 1294

-

DS1110E-450+ 时钟/计时 - 延迟线2022-11-30 85

-

DS1110E-80+ 时钟/计时 - 延迟线2022-11-29 73

-

延迟线,延迟线是什么意思2010-03-09 10242

全部0条评论

快来发表一下你的评论吧 !