板级封装产业技术及市场趋势报告

制造/封装

描述

麦姆斯咨询:OSAT一直在推动半导体产业开发创新解决方案,一种方案便是通过从晶圆和条带级向更大尺寸的面板级转换,充分利用规模经济和效率的优势。而且板级制造可以利用晶圆级封装(WLP)和PCB 平板显示 光伏产业的专业知识和基础设施。

板级封装厂商已经为规模量产做好准备。

产业为何青睐板级封装

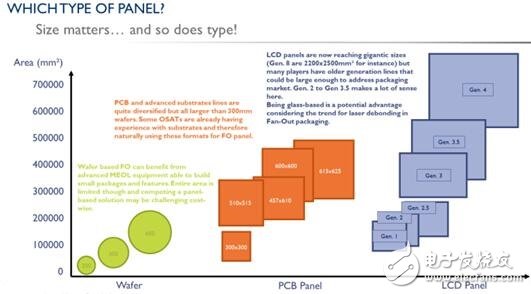

对更低成本和更高性能的需求,外加OSAT(外包半导体封测厂商)/组装厂终端客户不断要求更低的价格,一直在推动半导体产业开发创新解决方案。一种方案便是通过从晶圆和条带级向更大尺寸的面板级转换,充分利用规模经济和效率的优势。从晶圆级向板级(例如从12英寸晶圆向18 x 24英寸面板)的转换,成本最高可降低50%(如果技术已经完备),良率超过90%。而且,板级制造可以利用晶圆级封装(WLP)和PCB/平板显示/光伏产业的专业知识和基础设施。

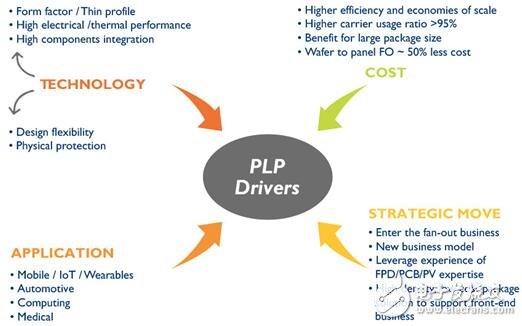

据麦姆斯咨询介绍,很多因素正在驱动板级封装(PLP)的发展,推动供应链各个位置的众多厂商投入板级基础设施。一方面,领先的无晶圆厂商希望OSAT厂商降低高密度扇出型晶圆级封装(FOWLP)的成本,而采用大尺寸面板似乎是显著降低封装价格的关键。事实上,所有大型OSAT厂商的发展路线图上都有扇出型板级封装(FOPLP)。另一方面,是那些战略投资、开发PLP产能并积极推动其应用的厂商,这些厂商主要受FOWLP业务的成功和宣传推动,同时也包括:

- 错过FOWLP(eWLP)早期热潮的厂商(例如PTI力成科技,ASE日月光);

- 在基板业务中遭受损失,希望开拓一种能够利用其基板制造经验的新业务(例如SEMCO三星电机,Unimicron欣兴电子);

- 已经具备面板级工艺经验(例如LCD封装),并相信它们能够将这些经验应用于PLP(例如NEPES纳沛斯);

- 希望开发高密度、低成本封装,以支持其前端芯片业务(例如Samsung Electronics三星电子,Intel英特尔)。

板级封装平台的市场驱动因素

供应链现状

许多封装平台都可以被认为是基于面板的封装,但是,本报告仅将两类封装技术划为PLP,亦即采用RDL互联制造,并在面板级(面板尺寸>300 mm x 300 mm)完成进一步组装的:FOPLP和嵌入式芯片。其中,FOPLP吸引了许多厂商(包括设备厂商和供应商)更高的关注,因此本报告重点聚焦FOPLP,对FOPLP进行了更深入的研究和分析。

PLP设备供应商概览

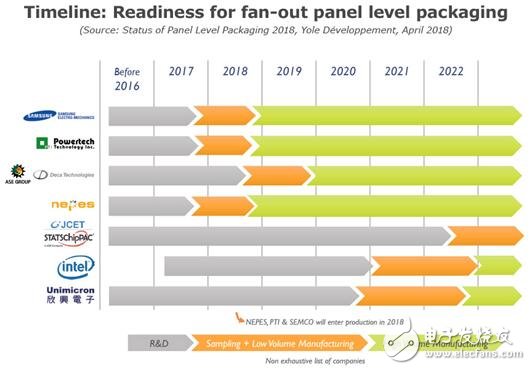

很多厂商都已经开发了自己的FOPLP技术,但是经过多年的开发/验证/出样,仅有三家厂商将在2018年最终进入量产,它们分别是:Powertech Technologies(PTI)、NEPES和SEMCO。NEPES已经自2017年开始了小规模量产。和Deca Technologies 合作的ASE,也已经处于先进的发展阶段,并将在2019年或2020年实现商业量产。各厂商都有自己的业务策略,开发自己的FOPLP技术(不同的面板尺寸、采用不同的基础设施等)。

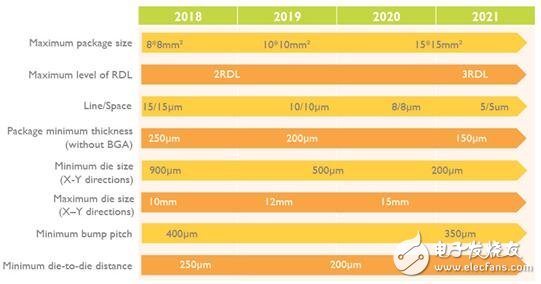

例如,NEPES主要专注于粗放设计(>10/10 L/S),目标应用包括汽车、传感器和物联网等,很可能不会开拓高密度设计。另一方面,PTI和SEMCO的长期目标则剑指要求8/8或以下L/S的中高端应用。同时,Unimicron正在开发一种业务模式,自己制造高密度RDL,进一步的组装则交由OSAT合作伙伴或客户完成。此外,Amkor(安靠)和JCET/STATS ChipPAC(长电/星科金朋)等主要OSAT厂商目前正处于“静观其变”的阶段,评估多种选择,它们预计在2022年以前都不会进入量产。

主要厂商对扇出型板级封装的准备情况时间轴

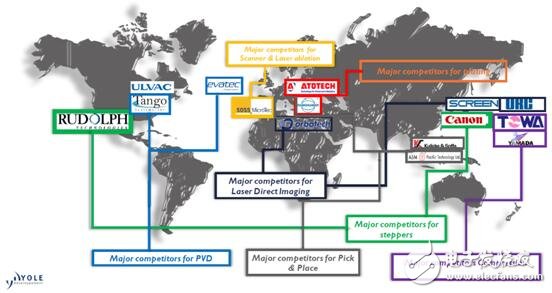

对于PLP,设备已不再是瓶颈。市场上也有机台能够支持板级封装中的各种工艺。不过,某些支持高密度板级封装的机台则比较特殊且昂贵。因此,瓶颈在于机台成本以及能不能买到。对于某些面板制造工艺(电镀、物理气相沉积PVD、模塑、芯片贴装和划片等),已有机台可用,并可以采用来自PCB、平板显示或LCD产业的机台。不过,对于其它先进封装(例如光刻等)固有的关键工艺步骤,需要开发新型、升级的机台加工能力以支持这些工艺,如面板上的精细L/S图案化、厚胶光刻、面板处理能力、曝光场尺寸和焦深等。过去几年来,设备供应商一直致力于研发这些机台。

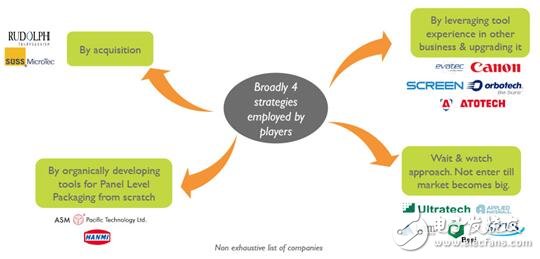

设备供应商正采用各异的策略进军PLP业务:并购(例如,Rudolph Technologies基于对AZORES平板显示面板打印设备的收购所获得的技术,开发了针对PLP的机台);利用来自其它业务的机台经验并进行升级(例如Evatech、Atotech、SCREEN);从0开始有机地开发PLP机台(ASM)。此外,某些在FOWLP市场具有强大市场地位的机台供应商,仍对PLP业务持怀疑态度,因此还在观望之中(例如 Ultratech、Applied Materials、Lam Research)。

机台供应商进入板级封装业务的策略

板级封装的技术挑战及规模制造路线图

FOPLP的广泛应用需要逐步满足某些标准并克服一些挑战。这些标准/挑战意味着大量的资本投入、标准化、多源可用性以及最重要的市场可用性,以确保面板产线的持续运行。在大尺寸面板上也存在技术挑战,例如翘曲控制、芯片贴装精度以及10/10um线宽以下的制造等。

FOPLP规模应用所面临的技术挑战

面板尺寸和组装工艺的标准化是FOPLP应用的最大障碍。各厂商都在使用不同的面板尺寸和基础设施(PCB / LCD / WLP / PV / Mix)来开发自己的工艺,以满足特定应用和客户的需求。在此背景下,终端用户很难实现多源采购。此外,设备供应商需要根据不同客户的要求来设计和制造设备也较难获利。

鉴于这些技术挑战对良率的不利影响,进入大规模量产的FOPLP将支持相对简单的设计:>10/10 umL/S,15 x 15mm2封装尺寸,以及多芯片SiP集成。

扇出型板级封装量产路线图

报告涉及的部分公司:AMS, Amicra Microtechnologies, Amkor, Analog Devices, Apple, Applied Materials, Asahi Kasei, ASE, ASM Pacific, AT&S, Atotech, AVX, Besi, Bosch, Canon, CEA-LETI, Continental, Dai Nippon, Daimler, DNP, DYCONEX AG, Dow Electronic Materials, Evatech, EVG Group, Ford, Fujikura, GaN Systems, General Electric, Hanmi, HD Micro/DuPont, Heidelberg Instruments, HighTec EDV System,Huawei, Ibiden, Infineon, Intel, IPDiA, IME A*Star, IMEC, ITRI, IZM Fraunhofer, J-Devices, JSR Micro, Kulicke & Soffa (K&S), Kyocera, Maxim, Merck/AZ EM, Mitsui Kinzoku,Murata Electronics, Nagase, Nanium, NCAP China, Nikon, Nitto Denko, ON Semiconductor, Orbotech, ORC, Panasonic, Powertech Technologies, Qorvo, Qualcomm, Rohm Semiconductor, Rudolph, Sarda Technologies, Schweizer, SCREEN, Shinko, Shin Etsu, STMicroelectronics, SUSS MicroTec, Taiyo Yuden, Tazmo, TCL, TDK-EPCOS, TEL, Texas Instruments (TI), Thales, Towa, TransSiP, Tokyo Ohka Kogyo Co., LTD. (TOK), TSMC, Shin-Etsu MicroSi, Samsung Electro Mechanics (SEMCO), STATS ChipPAC, Ultratech, Unimicron, USHIO,UTAC, Valeo, Vishay, Yamada…

- 相关推荐

- 封装

-

电子采购供应市场趋势展望峰会,获供应商管理调查报告2011-02-11 0

-

2015年智能照明市场及相关产业链发展趋势报告2015-01-15 0

-

2017全球电子书阅读器市场发展现状及未来趋势概述2017-11-09 0

-

PCI Express的市场趋势及相关应用2019-05-08 0

-

汽车电子市场趋势2019-07-16 0

-

2019年中国IT市场趋势热点介绍2020-07-13 0

-

华秋分享:全球及中国电源管理芯片市场趋势2023-03-03 0

-

2011~2015年欧洲LED照明市场趋势与分析报告2012-05-15 2830

-

中国闪存市场发展趋势报告2012-06-18 2987

-

2016汽车照明最新技术、产业及市场趋势2016-09-26 1483

-

2015年十大安防市场趋势2016-12-19 780

-

英特尔投资和未来大数据市场趋势2018-11-09 2144

-

汽车电子产品市场趋势2021-03-21 813

-

BMS芯片市场趋势和主要技术壁垒是什么2022-07-29 4988

-

芯片封装技术的基本概念、分类、技术发展和市场趋势2023-09-12 1676

全部0条评论

快来发表一下你的评论吧 !