集成电路封装可靠性测试:推拉力测试技术详解与应用指南

电子说

描述

近期,小编收到不少半导体行业客户的咨询,大多都是咨询集成电路芯片的封装与测试。随着半导体技术的飞速发展,集成电路芯片正朝着更高集成度、更小尺寸和更复杂封装结构的方向演进。在这一背景下,封装可靠性测试作为确保芯片性能稳定性和使用寿命的关键环节,其重要性日益凸显。

推拉力测试作为评估芯片封装机械性能的核心手段,能够有效检测焊点、键合线等关键连接部位的强度特性。本文科准测控小编将围绕Beta S100推拉力测试机在集成电路芯片封装测试中的应用,系统介绍其测试原理、检测仪器及标准操作流程,为相关领域的技术人员提供实用参考。

一、推拉力测试原理

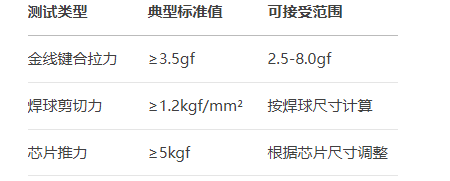

(一)推拉力测试是评估集成电路封装可靠性的重要力学测试方法,主要通过施加精确控制的推力或拉力来测量芯片封装中各连接部位的机械强度:

a、焊球剪切测试原理:通过水平推刀以恒定速度对BGA/CSP封装焊球施加推力,测量焊球与焊盘分离时的最大剪切力,评估焊球焊接可靠性

b、键合拉力测试原理:使用微型钩针垂直向上拉动键合线,测量键合线与芯片焊盘或引线框架分离时的拉力值,评估键合强度

c、芯片推力测试原理:对裸芯片表面施加垂直推力,测量芯片与基板分离时的推力值,评估贴片粘接强度

(二)测试过程中,设备实时记录力-位移曲线,通过分析曲线特征点可获取以下关键参数:

a、最大破坏力(Fmax)

b、断裂能量(Area under curve)

c、破坏模式(界面断裂、焊球断裂等)

二、测试标准体系

1、国际通用标准

JESD22-B117:半导体器件键合拉力测试标准方法

IPC/JEDEC-9704:印制板组件焊球剪切测试标准

MIL-STD-883H 方法2024:微电子器件键合强度测试方法

2、行业应用标准

GB/T 4937-2012:半导体器件机械和气候试验方法

GJB 548B-2005:微电子器件试验方法和程序

三、检测仪器

1、Beta S100推拉力测试机

2、试验条件

a、键合测试模块:配备1gf-500gf微型力传感器,适用于25-50μm细线测试

b、焊球测试模块:专用剪切工具组,支持50μm-1mm焊球测试

c、芯片测试模块:大面积平推头,最大支持20×20mm芯片测试

四、标准测试流程

步骤一、样品准备

确认封装类型(如BGA、QFN等)及测试点位置;

清洁样品表面,避免污染影响测试精度。

步骤二、设备设置

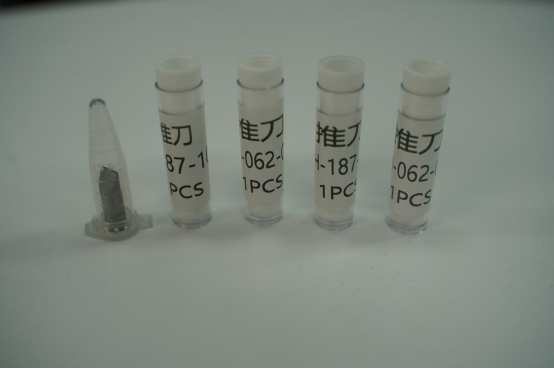

安装对应夹具(剪切刀/钩针/平推头);

选择力值传感器(如1gf~50kgf范围);

设置测试参数(速度、剪切高度、触发阈值等)。

步骤三、定位与校准

使用高清摄像头定位测试点(精度±2μm);

执行零点校准,消除机械间隙误差。

步骤四、执行测试

自动接触样品并施加推力/拉力;

实时记录力-位移曲线,捕捉断裂峰值;

自动判定破坏模式(界面断裂、焊球断裂等)。

步骤五、数据分析

导出最大力值(Fmax)、位移等关键数据;

生成统计报告(CPK、均值、标准差等)。

步骤六、结果验证

对比行业标准(如JESD22-B117);

异常数据复测,确保结果可靠性。

五、典型应用案例分析

QFN封装键合拉力测试优化:

某功率器件生产企业使用Beta S100对QFN-48封装进行金线键合测试时发现:

初始CPK仅1.12(低于1.33要求)

破坏模式分析显示60%为界面断裂

通过测试数据反推工艺参数:

调整键合温度从160℃→175℃

优化超声功率(从60mW→72mW)

实施后CPK提升至1.58,界面断裂降至15%以下

以上就是小编介绍的有关集成电路芯片的封装与测试相关内容了,希望可以给大家带来帮助!如果您还想了解更多关于集成电路芯片的封装与测试方法、论文和实验报告,推拉力测试机怎么使用,工作原理、杠杆如何校准和使用方法视频,推拉力测试仪操作规范、使用方法和测试视频,焊接强度测试仪使用方法和键合拉力测试仪等问题,欢迎您关注我们,也可以给我们私信和留言,【科准测控】小编将持续为大家分享推拉力测试机在锂电池电阻、晶圆、硅晶片、IC半导体、BGA元件焊点、ALMP封装、微电子封装、LED封装、TO封装等领域应用中可能遇到的问题及解决方案。

审核编辑 黄宇

-

芯片IC可靠性测试、ESD测试、FA失效分析2020-05-17 8871

-

GaNPower集成电路的可靠性测试及鉴定2023-06-19 1295

-

集成电路封装测试与可靠性2021-04-09 2276

-

全自动推拉力测试机金丝键合推拉力测试机2023-05-12 1539

-

金丝键合推拉力测试机的应用2023-05-23 1487

-

集成电路封装可靠性设计2023-06-15 1789

-

LED封装晶片便携式推拉力测试机2023-05-31 1401

-

半导体封装推拉力测试机选择指南:测试流程和技术参数详解!2023-06-26 2020

-

为什么要做推拉力测试?焊接强度推拉力测试仪2024-01-03 1474

-

涨知识:元器件失效之推拉力测试,附推拉力测试机的应用!2024-05-23 1797

-

多功能推拉力测试机:原理及应用2024-12-26 1292

-

你不知道的COB封装测试方法,快来看看推拉力测试机的应用!2025-04-03 1326

-

BGA封装焊球推力测试解析:评估焊点可靠性的原理与实操指南2025-04-18 1578

-

提升QFN封装可靠性的关键:附推拉力测试机检测方案2025-05-08 949

-

基于推拉力测试机的PCBA电路板元器件焊点可靠性评估与失效机理探讨2025-10-24 449

全部0条评论

快来发表一下你的评论吧 !