量子阱场效应晶体管介绍

描述

来源:半导体鱼塘

1.10 量子阱场效应晶体管

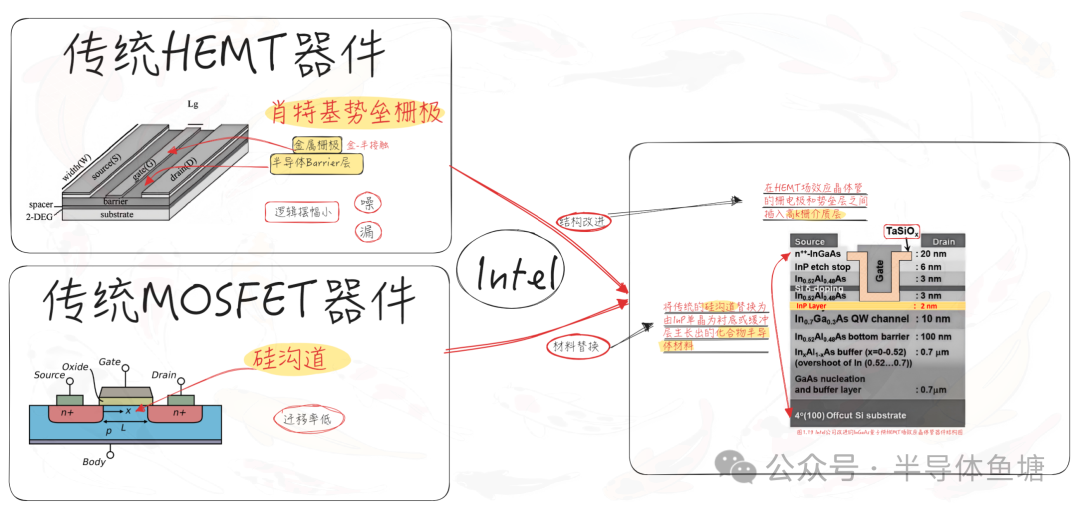

前面的1.8节介绍了HEMT器件,但传统的HEMT器件虽然具有高迁移率、高频率等诸多优点,但其命门在于结构中的肖特基势垒栅极,这种结构的器件很难改善栅极漏电严重的问题,存在着逻辑摆幅较小、抗噪声能力差等问题。

对于传统的MOSFET器件,虽然因为栅极绝缘层的采用大大抑制了栅极漏流,但是硅沟道较低的电子迁移率也限制了其在超高频、超高速等领域的应用。

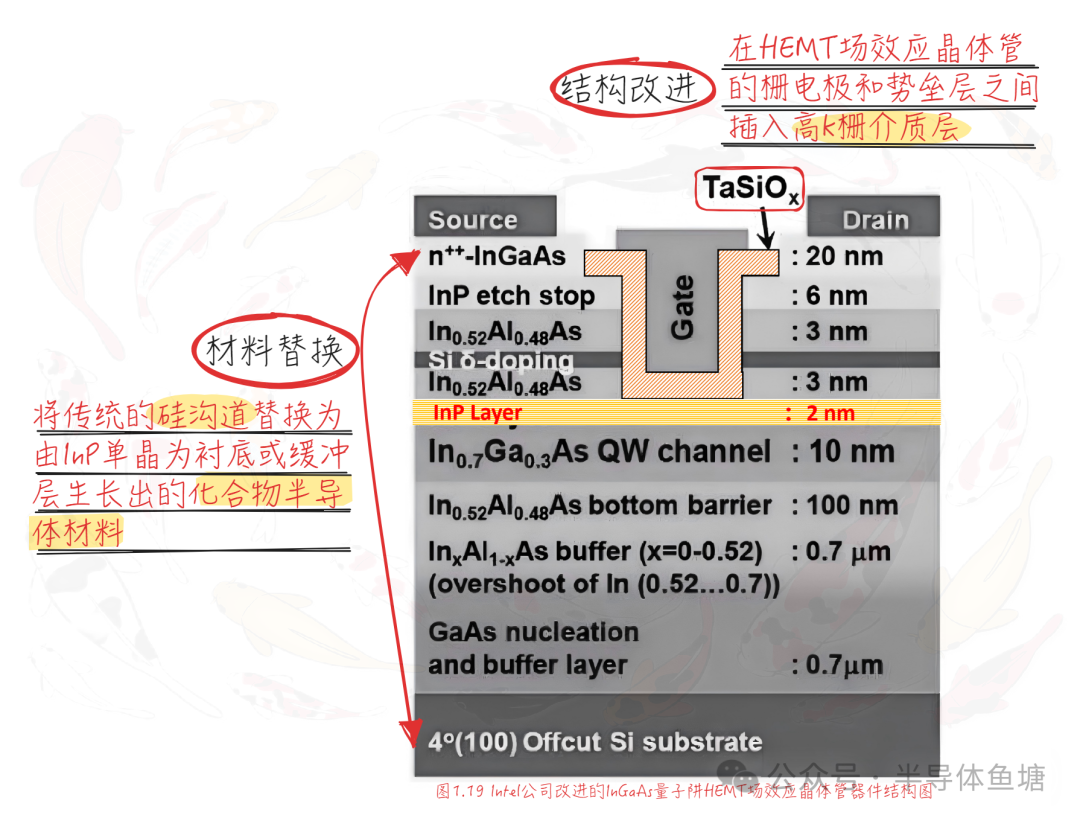

2009年Intel公司在砷化铟镓(InGaAs)HEMT场效应晶体管的栅电极和势垒层之间插入了一个高k栅介质层,并给其取名为量子阱场效应晶体管(Quantum Well FET,QW FET)。

如下图所示,这种量子阱场效应晶体管主要的特点是采用了InP基半导体和具有高k的栅介质层。这里可以看出,Intel采用的衬底还是硅晶圆,然后在上面外延生长不同的化合物材料。

InP基半导体材料是以InP单晶为衬底或缓冲层而生长出的化合物半导体材料, 包括InGaAs、InAlAs、InGaAsP以及GaAsSb等材料。

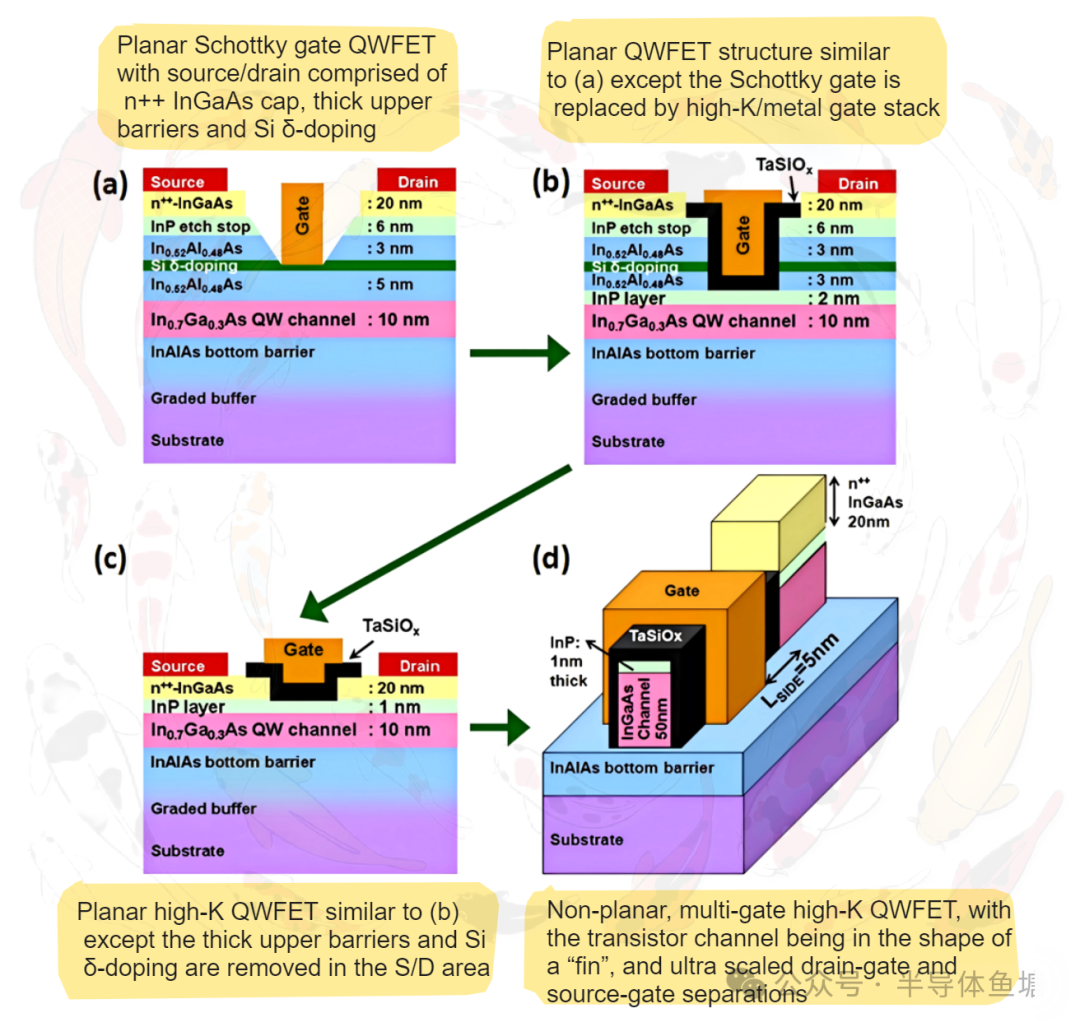

如下为Intel公司研究量子阱场效应晶体管的技术演进图。[Non-Planar, Multi-Gate InGaAs Quantum Well Field Effect Transistors with High-K Gate Dielectric and Ultra-Scaled Gate-to-Drain/Gate-to-Source Separation for Low Power Logic Applications]

从上图可以看出InGaAs量子阱场效应晶体管(QWFET)从平面到非平面多栅极架构的演变:

(a) 平面肖特基栅QWFET,其源/漏区由n++型InGaAs cap层构成,采用厚上势垒层和硅δ掺杂;

(b) 平面QWFET结构(与a类似),但将肖特基栅替换为high-K/金属栅叠层结构;

(c) 平面high-K QWFET(与b类似),但在源/漏区移除了厚上势垒层和硅δ掺杂;

(d) 非平面多栅极高K QWFET,其沟道呈“鳍”形,并采用超缩小的漏极-栅极和源极-栅极间距。

通过消除(c)和(d)中的厚上势垒层及硅δ掺杂,同时利用n++型InGaAs cap层作为载流子供给层,实现了源/漏接触面积的缩放并保持低电阻特性。

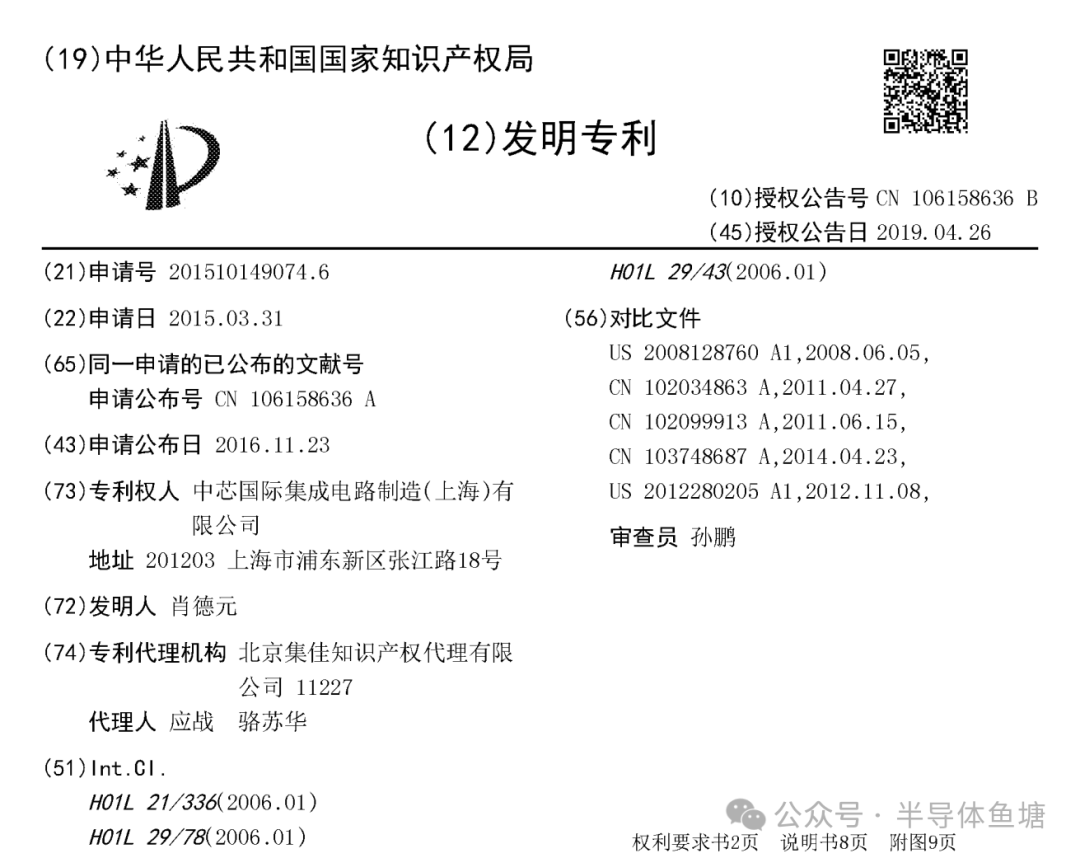

为进一步提高量子阱场效应晶体管的性能,相比于Fin结构的三面栅压控制,科学家和工程师们再一次将眼光放在全包围栅结构晶体管上。如下面的专利所描述,肖德元老师提出了一种圆柱体全包围栅量子阱场效应晶体管,通过其全包围栅结构来加强器件栅控能力、增强驱动电流以及提高器件集成密度。

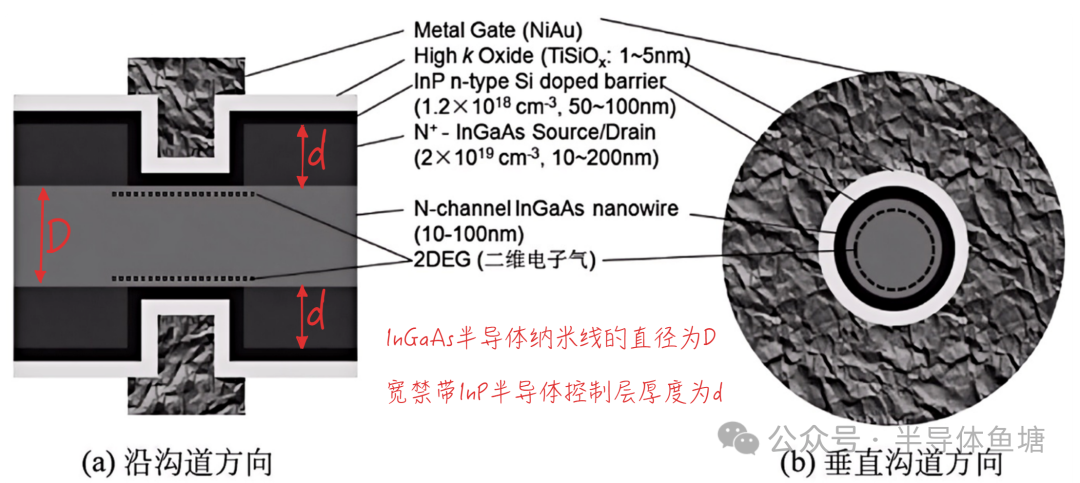

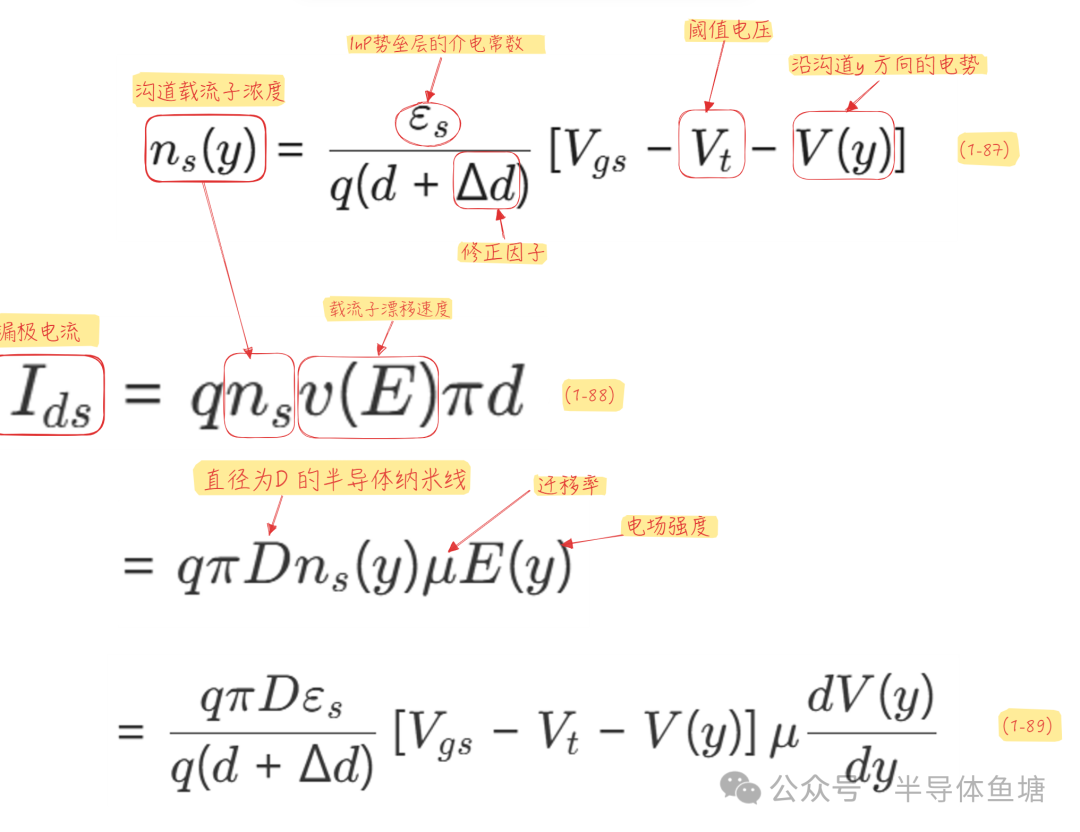

这种圆柱体全包围栅量子阱场效应晶体管的结构如下图所示。这里假设InGaAs半导体纳米线的直径为D,宽禁带InP半导体控制层厚度为d,可以通过电荷控制模型以及逐级沟道近似得到圆柱体全包围栅量子阱场效应晶体管的I-V关系。

首先求得沟道载流子浓度与Vgs的表达式,然后可以得到漏极电流的表达式。

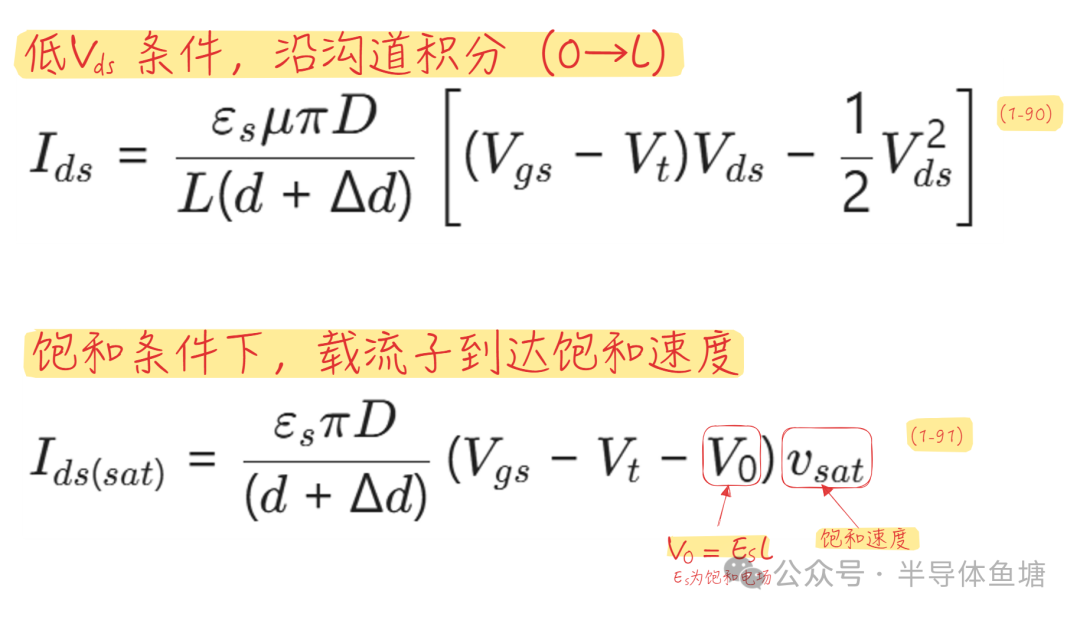

假定载流子迁移率为常数,在低Vds条件下,沟道电流未达到饱和,通过沿沟道方向对电压积分可以得到圆柱体全包围栅量子阱场效应晶体管的I-V 特性。

当Vds值增加,载流子达到饱和速度Vsat,I-V特性可以写作1-91式。

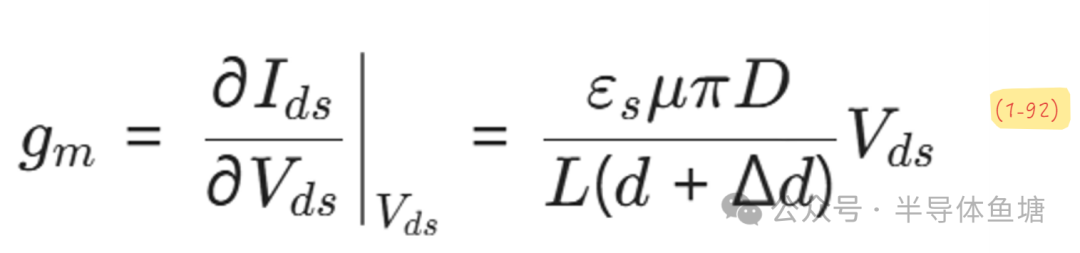

跨导为描述输入电压变化对输出电流的控制能力的参数,根据其定义可以直接得到跨导的表达式。

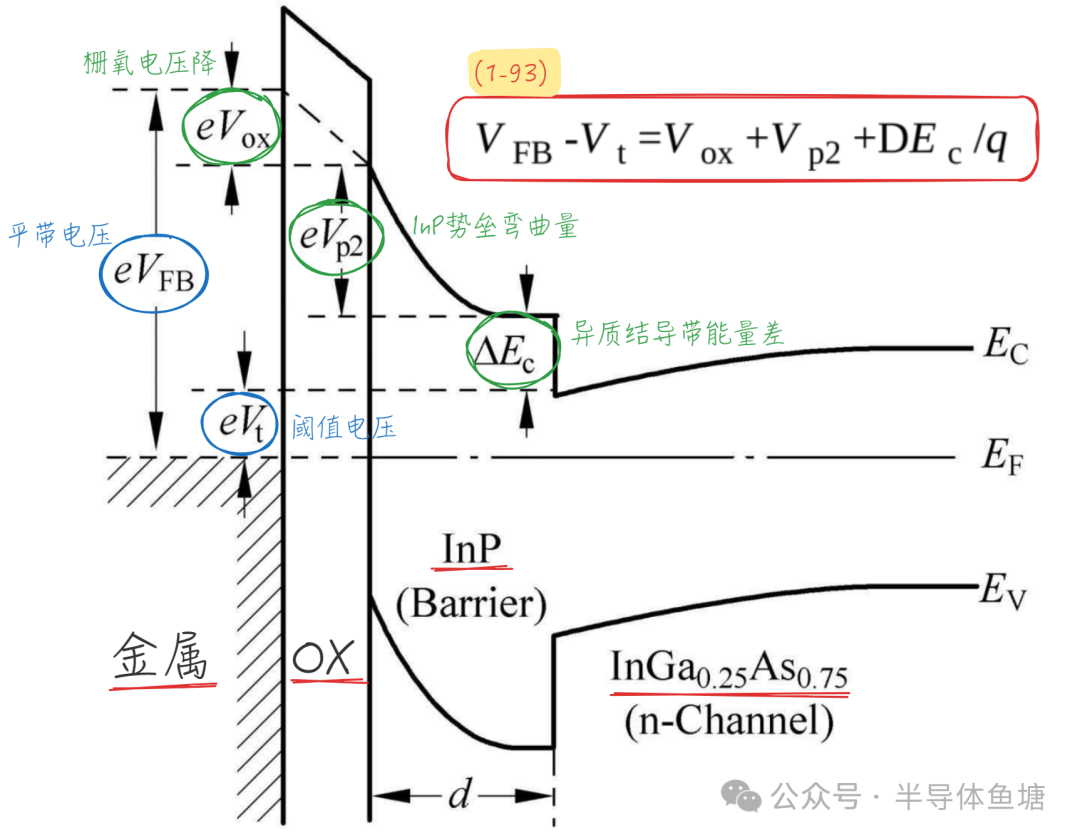

参照插入了一个高k栅介质层的量子阱HEMT器件能带图,可以得到1-93的表达式。

栅氧电压可以通过1-94、1-95和1-96来表示,InP宽禁带半导体控制层势垒弯曲量Vp2可以通过1-97式得到,这里的过程比较简明,不详细说明。

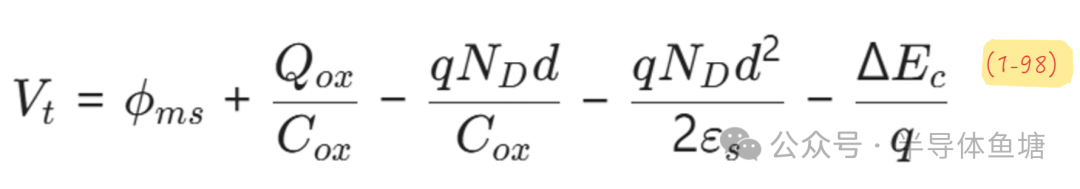

最后可以得到阈值电压的表达式1-98,其中Qox为栅氧化层中的固定电荷面密度,φms为金属栅电极与InP宽禁带半导体控制层之间的功函数差。

1.11 小结

无结场效应晶体管(JFET)通过消除源漏PN结、抑制短沟道效应及提升载流子迁移率,展现出优于传统MOSFET的潜力,结合高迁移率III-V族材料(如InGaAs)与三维FinFET/GAA结构创新,为突破硅基CMOS性能极限、实现高频低功耗芯片提供了关键技术路径,推动微电子器件向异质集成与后摩尔时代演进。

-

功率场效应晶体管(MOSFET)原理2012-08-20 5203

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 3749

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 3196

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 3376

-

场效应晶体管的分类及作用2019-05-08 4084

-

场效应晶体管的选用经验分享2021-05-13 1803

-

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?2023-02-24 14564

-

场效应晶体管的分类及使用2010-01-13 887

-

什么是场效应晶体管2009-05-24 7497

-

场效应晶体管介绍2016-08-22 1032

-

有机场效应晶体管是什么_有机场效应晶体管介绍2018-01-03 30059

-

功率场效应晶体管的工作特性2019-10-11 12883

-

如何进行场效应晶体管的分类和使用2020-07-02 1918

-

场效应晶体管的分类说明2020-09-18 10072

-

场效应晶体管的作用2023-05-16 3338

全部0条评论

快来发表一下你的评论吧 !