UCC27284-Q1 具有 5V UVLO 的汽车类 3A、120V 半桥栅极驱动器数据手册

描述

UCC27284 -Q1 是一款稳健的 N 沟道 MOSFET 驱动器,最大开关节点 (HS) 额定电压为 100 V。它允许在基于半桥或同步降压配置的拓扑中控制两个 N 沟道 MOSFET。其 3A 峰值拉电流和灌电流以及低上拉和下拉电阻使 UCC27284 -Q1 能够在 MOSFET 米勒平台过渡期间以最小的开关损耗驱动大功率 MOSFET。由于输入与电源电压无关,因此 UCC27284 -Q1 可以与模拟和数字控制器结合使用。如果需要,两个输入和输出可以重叠,用于次级侧全桥同步整流等应用。

*附件:ucc27284-q1.pdf

输入引脚和 HS 引脚能够承受显著的负电压,从而提高系统稳健性。5 V UVLO 允许系统在较低的偏置电压下工作,这在许多高频应用中是必需的,并且可以提高某些工作模式下的系统效率。小传播延迟和延迟匹配规格最大限度地减少了死区时间要求,从而进一步提高了效率。

高侧和低侧驱动器级均提供欠压锁定 (UVLO),如果 VDD 电压低于指定阈值,则强制输出为低电平。集成的自举二极管在许多应用中无需外部分立二极管,从而节省了电路板空间并降低了系统成本。UCC27284-Q1 采用 SOIC 封装,适用于恶劣的系统环境。

特性

- 符合 AEC-Q100 标准,结果如下

- 温度等级 1 (T

j= –40°C 至 150°C) - 器件 HBM ESD 分类等级 1B

- 器件 CDM ESD 分类等级 C3

- 温度等级 1 (T

- 在高侧低侧配置中驱动两个 N 沟道 MOSFET

- 5V 典型欠压锁定

- 16ns 典型传播延迟

- 12ns 上升时间,10ns 下降时间(1.8nF 负载)

- 1ns 典型延迟匹配

- 输入上的 5V 负电压处理

- HS 上的 14V 负电压处理

- ±3A 峰值输出电流

- 绝对最大启动电压 120 V

- 集成自举二极管

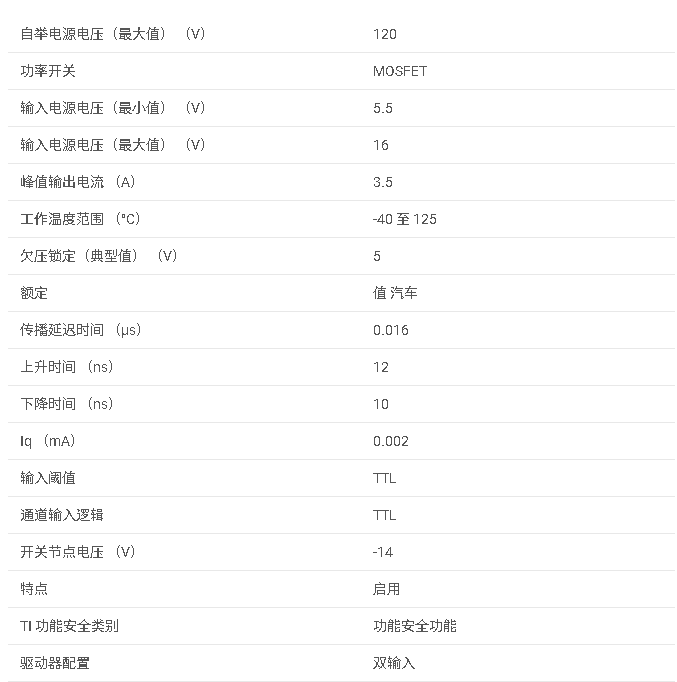

参数

方框图

一、产品概述

UCC4-Q是一款针对汽车应用设计的-A、-V半桥驱动器,具有负电压处理能力和低开关损耗。该驱动器通过了AEC-Q0认证,适用于DC/DC转换器、电动助力转向、车载充电器(OBC)、集成式起动机发电机(iBSG)以及汽车HVAC压缩机模块等应用。

二、主要特性

- AEC-Q认证:适用于汽车级应用。

- 双N沟道MOSFET驱动:支持高侧和低侧配置。

- 负电压处理能力:输入端和HS端可承受显著负电压,提高系统鲁棒性。

- 低开关损耗:具有低上升和下降时间,减少开关过程中的能量损耗。

- 集成自举二极管:消除了对外部离散二极管的需求,节省板级空间并降低成本。

- 5-V UVLO:低电压锁定功能,确保系统在低偏置电压下的可靠运行。

- 紧凑封装:采用SOIC封装,适用于严苛的系统环境。

三、应用领域

- 汽车DC/DC转换器

- 电动助力转向系统

- 车载充电器(OBC)

- 集成式起动机发电机(iBSG)

- 汽车HVAC压缩机模块

四、功能描述

1. 输入与输出

- 独立输入:两个输入(HI和LI)可独立控制,支持输入信号重叠,适用于全桥同步整流等应用。

- 分裂输出:高侧(HO)和低侧(LO)输出,分别连接至高侧和低侧MOSFET的栅极。

2. 电气特性

- 低传播延迟:典型传播延迟为6 ns,延迟匹配为1 ns,有助于减少死区时间,提高效率。

- 高电流驱动能力:±-A峰值输出电流,低上拉和下拉电阻,适用于驱动大功率MOSFET。

- 宽电压范围:支持5.5 V至6 V的VDD供电电压,以及- V至 V的输入电压范围。

3. 保护功能

- UVLO保护:对高侧和低侧驱动级提供UVLO保护,防止在供电电压不足时误驱动MOSFET。

- 负电压瞬态处理:输入端和输出端可承受负电压瞬态,提高系统可靠性。

五、典型应用

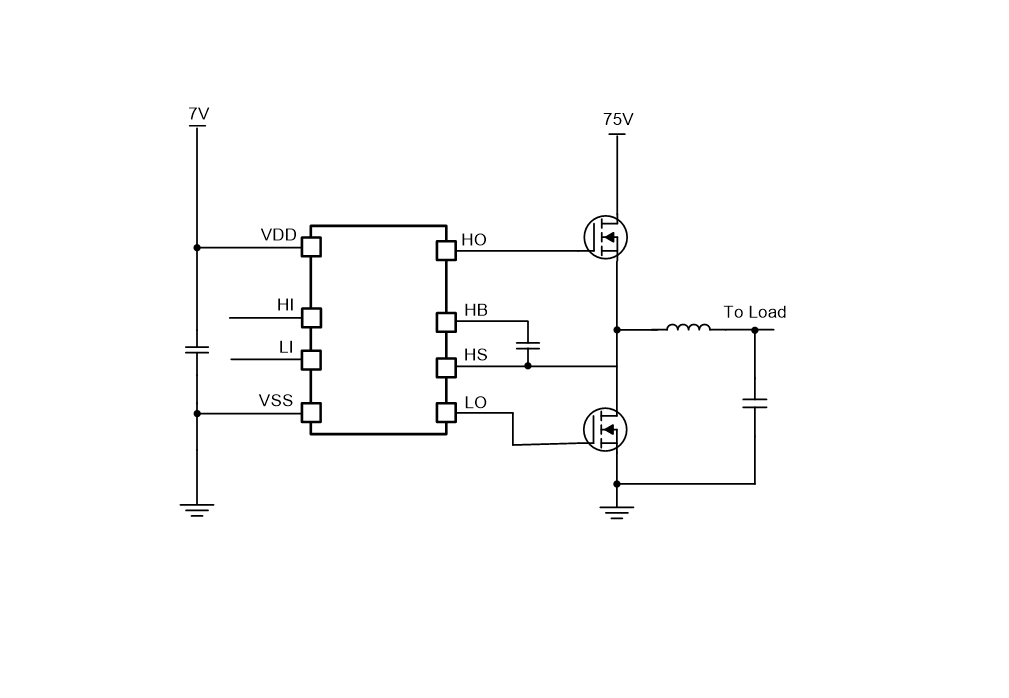

文档提供了一个典型应用电路,展示了UCC-Q1如何驱动两个N沟道MOSFET构成半桥电路。同时,还提供了详细的设计步骤,包括选择自举电容和VDD电容、估算驱动功率损耗、选择外部栅极电阻等。

六、电源推荐

- VDD电源:推荐使用. V至 V的电源,并连接1 µF的旁路电容以减小电压波动。

- 自举电容:根据应用需求选择合适的自举电容值,通常推荐值为. µF。

七、布局指南

- 电容放置:低ESR/ESL电容应尽可能靠近VDD和HB引脚放置,以减小高频噪声和电压波动。

- 热管理:热焊盘应连接到大的热质量迹线(通常为IC接地平面)以改善热性能。

- 接地设计:高电流路径应尽可能短且直接连接到地平面,以减小环路电感和噪声。

-

UCC27284-Q1汽车级半桥驱动器:设计与应用全解析2026-01-08 293

-

Texas Instruments UCC27301A/UCC27301A-Q1半桥驱动器数据手册2025-07-25 864

-

UCC27200-Q1 具有 8V UVLO 和 CMOS 输入的汽车类 3A、120V 半桥栅极驱动器数据手册2025-05-21 819

-

UCC27200A 具有 8V UVLO、负电压处理和 CMOS 输入的 3A、120V 半桥栅极驱动器数据手册2025-05-20 804

-

UCC27212A-Q1 具有 5V UVLO 的汽车级 4A、120V 半桥栅极驱动器数据手册2025-05-19 791

-

UCC27282-Q1 具有 5V UVLO、互锁和使能功能的汽车类 3A、120V 半桥驱动器数据手册2025-05-17 895

-

UCC27284 具有 5V UVLO 和使能的 3A、120V 半桥栅极驱动器数据手册2025-05-16 924

-

UCC27311A-Q1 具有 8V UVLO 和 enable 的汽车级 120V 4A 半桥栅极驱动器数据手册2025-05-15 845

-

具有跨导保护和低开关损耗的汽车类3A 120V半桥驱动器UCC27282-Q1数据表2024-04-02 407

-

具有8V UVLO、跨导保护和使能端的汽车类120V、3.7A/4.5A 半桥驱动器UCC27301A-Q1数据表2024-03-28 455

-

具有跨导保护和低开关损耗的3A 120V半桥驱动器UCC27282数据表2024-03-26 410

全部0条评论

快来发表一下你的评论吧 !