UCC27531 具有 8V UVLO、35V VDD 和分离输出的 2.5A/5A 单通道栅极驱动器数据手册

描述

UCC2753x 单通道高速栅极驱动器可有效驱动 MOSFET 和 IGBT 电源开关。UCC2753x 器件采用的设计允许通过非对称驱动(分离输出)提供高达 2.5A 的电流和 5A 的灌电流,并且能够支持负关断偏置、轨到轨驱动能力、极小的传播延迟(典型值为 17ns),是 MOSFET 和 IGBT 电源开关的理想解决方案。UCC2753x 系列器件还支持使能、双输入以及反相和非反相输入功能。分离输出和强大的不对称驱动增强了器件对寄生米勒导通效应的免疫力,有助于减少接地去抖动。

*附件:ucc27531.pdf

保持 input pin 开路将使驱动器输出保持低电平。驱动器的 logic 行为显示在 application diagram、timing diagram 以及 input and output logic truth table 中。

VDD 引脚上的内部电路提供欠压锁定功能,将输出保持为低电平,直到 VDD 电源电压处于工作范围内。

特性

- 低成本栅极驱动器(为驱动 FET 和 IGBT 提供最佳解决方案)

- 分立晶体管对驱动的绝佳替代品(提供与控制器的轻松接口)

- TTL 和 CMOS 兼容输入逻辑阈值(与电源电压无关)

- 分离输出选项允许调谐导通和关断电流

- 反相和同相输入配置

- 使用固定的 TTL 兼容阈值启用

- 在 18V VDD 时,具有 2.5A 的高拉电流和 2.5A 或 5A 灌电流峰值驱动电流

- 10 V 至 35 V 的宽 VDD 范围

- 输入和使能引脚能够承受高达地电位以下 –5V DC 的电压

- 当输入悬空或在 VDD UVLO 期间,输出保持低电平

- 快速传播延迟(典型值为 17ns)

- 快速上升和下降时间

(1800pF 负载时,典型值为 15ns 和 7ns) - 欠压锁定 (UVLO)

- 用作高侧或低侧驱动器(如果设计具有适当的偏置和信号隔离)

- 低成本、节省空间的 5 引脚或 6 引脚 DBV (SOT-23) 封装选项

- UCC27536 和 UCC27537 引脚对引脚兼容 TPS2828 和 TPS2829

- 工作温度范围为 –40°C 至 140°C

参数

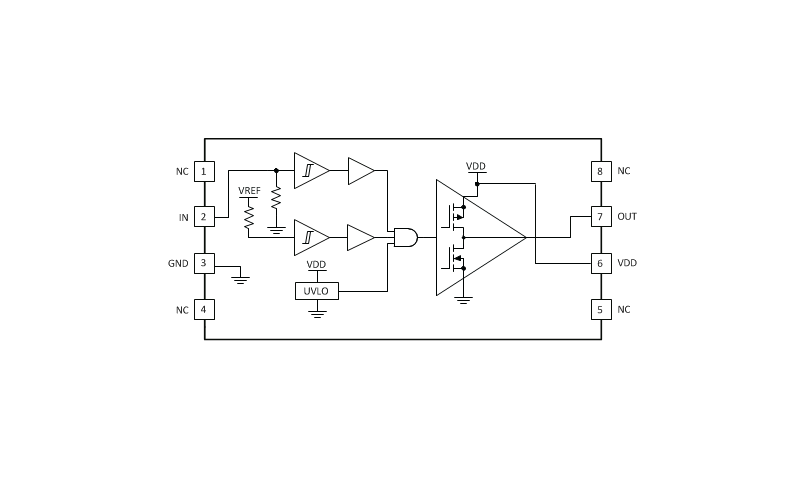

方框图

一、产品概述

- 型号:UCC

- 类型:单通道高速栅极驱动器

- 特点:

- 低成本解决方案,适用于驱动MOSFET和IGBT

- TTL和CMOS兼容输入逻辑阈值,独立于供电电压

- 分裂输出选项,可调开通和关断电流

- 反相和非反相输入配置

- 启用功能,具有固定的TTL兼容阈值

- 高达2.5A的源电流和2.5A或A的漏电流峰值(VDD=V)

- 宽广的VDD范围:V至V

- 输入和启用引脚能承受高达-.V的负电压

- 输入浮空或VDD欠压锁定(UVLO)时输出保持低电平

- 极快的传播延迟(典型值7ns)

- 快速的上升和下降时间(典型值分别为ns和7ns)

- 可作为高侧或低侧驱动器(需适当偏置和信号隔离)

- 低成本、节省空间的引脚或6引脚DBV(SOT-)封装选项

二、引脚配置与功能

- EN:启用引脚(将EN拉至GND禁用输出,拉高或悬空启用输出)

- IN:非反相输入(UCC1)

- IN+ 、 IN- :非反相和反相输入(UCC3)

- VDD:偏置供电输入

- GND:接地

- OUTL:漏电流输出(高达A)

- OUTH:源电流输出(高达.A)

- OUT:单输出(结合OUTH和OUTL功能,UCC1、UCC6、UCC7)

三、电气特性

- VDD范围:V至V(推荐操作条件)

- UVLO阈值:

- VON:.V(典型值)

- VOFF:.V至9.1V

- 滞回电压:.V

- 输入阈值:

- VIN_H(高阈值):V(典型值)

- VIN_L(低阈值):V(典型值)

- 输入滞回:1V

- 启用阈值:

- VEN_H(高阈值):.V至2.1V

- VEN_L(低阈值):.V至1.2V

- 启用滞回:.V

- 输出特性:

- 峰值源电流(OUTH):-.A

- 峰值漏电流(OUTL):-A

- VOH:高电平输出电压(IOUTH = -0mA时,接近VDD)

- VOL:低电平输出电压(IOUTL = mA时,典型值.V至0.V)

- ROH:输出上拉电阻(典型值Ω至Ω)

- ROL:输出下拉电阻(典型值0.Ω至1.7Ω)

四、开关特性

- 传播延迟:

- 开通传播延迟(tD):典型值7ns

- 关断传播延迟(tD):典型值7ns

- 上升时间:典型值ns

- 下降时间:典型值7ns

五、应用

- 适用领域:

- 开关电源

- DC-DC转换器

- 太阳能逆变器、电机控制、UPS

- HEV和EV充电器

- 家用电器

- 可再生能源电力转换

- SiC FET转换器

六、布局与热考虑

- 布局指南:

- 将驱动器尽可能靠近功率器件放置,以最小化高电流迹线的长度。

- 在VDD和GND之间放置旁路电容器,并尽可能缩短迹线长度以改善噪声滤波。

- 最小化开通和关断电流环路路径的杂散电感。

- 使用星型接地减少噪声耦合。

- 使用接地平面提供噪声屏蔽和辅助散热。

- 热考虑:

- 封装提供不同的热阻特性,影响散热效果。

- 确保适当的散热设计,以避免超过最大结温。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SiLM27531H车规级低边单通道门极驱动器,为高效电源管理赋能2026-02-28 106

-

UCC2753x系列单通道高速栅极驱动器:特性、应用与设计要点2026-01-09 790

-

SiLM27531HAC-AQ 30V, 5A/5A单通道高欠压保护阈值的高速低边门极驱动器2025-11-04 881

-

UCC27532-Q1 具有 8V UVLO、35V VDD 和 CMOS 输入的汽车类 2.5A/5A 单通道栅极驱动器数据手册2025-05-20 790

-

ISO5852S-Q1 汽车5.7kVrms 2.5A/5A单通道隔离栅极驱动器数据手册2025-05-19 790

-

UCC23113 具有功能隔离 (1.2kVRMS) 的 4A/5A 单通道光兼容隔离式栅极驱动器数据手册2025-05-16 904

-

UCC23525 具有12V UVLO的 5A/5A、5.7kVRMS、增强型单通道光兼容隔离式栅极驱动器数据手册2025-05-15 1122

-

具有UVLO的5A、5A光耦兼容单通道功能隔离式栅极驱动器UCC23113数据表2024-03-22 581

-

UCC27531 2.5A、5A、40VMAX VDD FET 和 IGBT 单门驱动器2018-10-16 1149

全部0条评论

快来发表一下你的评论吧 !