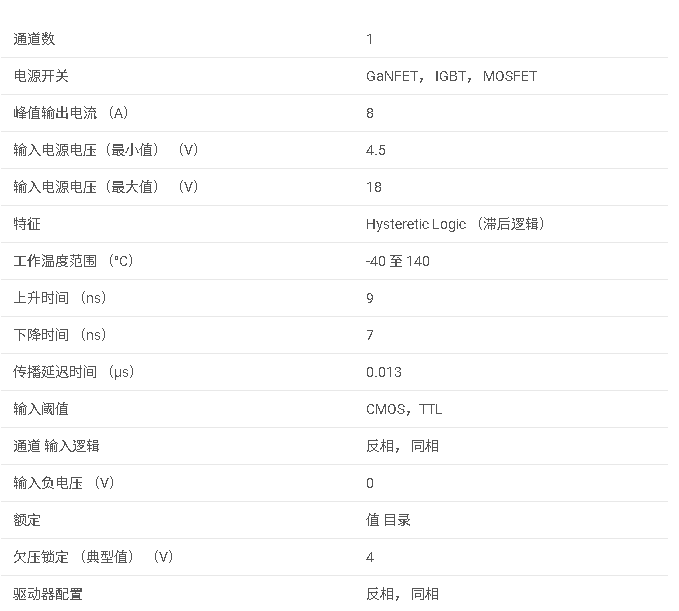

UCC27512 采用 SON 封装的具有 5V UVLO 和分离输出的 4A/8A 单通道栅极驱动器数据手册

描述

UCC27511 和 UCC27512 单通道、高速、低侧栅极驱动器器件可以 有效驱动 MOSFET 和 IGBT 功率开关。使用本质上最小化 击穿电流、UCC27511 和 UCC27512 能够拉出和吸收高峰值电流 脉冲进入电容性负载,提供轨到轨驱动能力和极小的传播 延迟,通常为 13 ns。

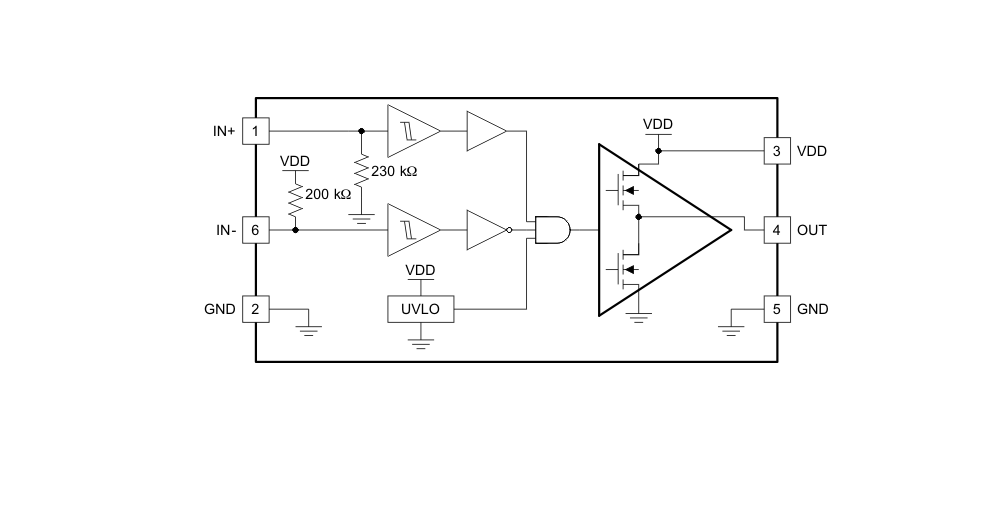

UCC27511 采用双输入设计,可灵活地实现两者 反相 (IN– pin) 和同相 (IN+ pin) 配置。IN+ 或 IN– 引脚可用于控制驱动器输出的状态。未使用的输入引脚可用于 启用和禁用功能。为安全起见,内部上拉和下拉电阻器 input pins 确保在 input pins 处于浮动状态时,output 保持为低电平。因此, 未使用的输入引脚不会悬空,必须适当偏置以确保驱动器输出 in enabled for normal operation(启用正常作)。

*附件:ucc27512.pdf

UCC27511 器件的输入引脚阈值基于 TTL 和 CMOS 兼容 低压逻辑是固定的,独立于 VDD 系列电源电压。 高阈值和低阈值之间的宽滞后提供了出色的抗噪性。

UCC27511 和 UCC27512 提供 4A 拉电流、8A 灌电流(非对称驱动)峰值驱动 电流能力。非对称驱动中的强大灌电流能力增强了对寄生、 Miller turnon 效应。UCC27511 器件还具有独特的分离输出配置,其中 栅极驱动电流通过 OUTH 引脚提供,并通过 OUTL 引脚吸收。这个独特的别针 配置允许用户对 OUTH 和 OUTL 施加独立的导通和关断电阻器 引脚,并轻松控制开关转换速率。

UCC27511 和 UCC27512 设计用于在较宽的 V 电压下工作DD 系列范围为 4.5 至 18 V,温度范围为 –40°C 至 140°C。 内部欠压锁定 V 上的 (UVLO) 电路DD 系列pin 将输出保持在 Out Outside 为低电平 VDD 系列作范围。能够在低电压水平下运行,例如 低于 5 V 的电压,以及一流的开关特性,特别适合驾驶 新兴的宽带隙功率开关器件,例如 GaN 功率半导体器件。

特性

- 低成本栅极驱动器器件,可出色

地替代 NPN 和 PNP 分立解决方案 - 4A 峰值拉电流和 8A 峰值灌电流非对称

驱动器 - 强大的灌电流提供了更

强的抗米勒转向能力 - UCC27511中的分离输出配置(允许轻松

独立地调整导通和关

断速度)可节省 1 个二极管 - 快速传播延迟(典型值为 13ns)

- 快速上升和下降时间(典型值为 9ns 和 7ns)

- 4.5V 至 18V 单电源范围

- 在 VDD UVLO 期间,输出保持低电平(确保在

上电和

断电时无毛刺运行) - TTL 和 CMOS 兼容输入逻辑阈值

(与电源电压无关) - 具有高抗噪

能力的迟滞逻辑阈值 - 双输入设计(可选择反相(IN– 引脚) 或同相 (IN+ 引脚)驱动器配置)

- 未使用的 Input Pin 可用于启用或

禁用功能

- 未使用的 Input Pin 可用于启用或

- 当 Input 引脚悬空时,输出保持低电平

- 输入引脚绝对最大电压电平不受

VDD 引脚偏置电源电压限制 - 工作温度范围为 –40°C

至 140°C - 6 引脚 DBV (SOT-23) 和 6 引脚 DRS(3mm ×

3mm WSON,带外露散热焊盘)封装

选项

参数

方框图

一、产品概述

- 型号:UCC

- 类型:单通道、高速、低侧栅极驱动器

- 特点:

- A峰值源电流和A峰值沉电流(非对称驱动)

- 引脚DBV(SOT-)和引脚DRS(mm x mm WSON,带裸露热垫)封装选项

- TTL和CMOS兼容输入逻辑阈值(独立于电源电压)

- 快速传播延迟(典型值ns)

- 快速上升和下降时间(典型值ns和ns)

- .V至V单电源供电范围

- 输出在VDD欠压锁定(UVLO)期间保持低电平

二、应用领域

- 开关模式电源

- DC-DC转换器

- 太阳能电源、电机控制、不间断电源(UPS)

- 新兴宽带隙功率器件(如GaN)的栅极驱动器

三、引脚配置与功能

- VDD:偏置电源输入

- GND:地

- IN+ :非反相输入

- IN- :反相输入

- OUTH:源电流输出(仅DBV封装)

- OUTL:沉电流输出(仅DBV封装)

- OUT:源/沉电流输出(DRS封装)

四、电气特性

- 供电电压范围:.V至V

- 输入阈值:

- 高电平阈值(VIN_H):.V至.V

- 低电平阈值(VIN_L):.V至.V

- 输入迟滞:.V

- 输出特性:

- 峰值源电流:A

- 峰值沉电流:A

- 高电平输出电压(VOH):接近VDD

- 低电平输出电压(VOL):mV至.V

- 输出上拉电阻(ROH):.Ω至.Ω

- 输出下拉电阻(ROL):.Ω至.Ω

五、保护功能

- UVLO:当VDD电压低于UVLO阈值时,输出保持低电平。

六、设备功能模式

- 正常模式:输出状态取决于IN+和IN-引脚的状态。

- UVLO模式:当VDD电压低于UVLO阈值时,设备进入UVLO模式,输出保持低电平。

七、典型应用

- 提供了非反相和反相配置的典型应用图。

- 详细描述了设计要求和设计过程,包括输入输出逻辑、输入阈值类型、VDD偏置供电电压、峰值源和沉电流、启用和禁用功能、传播延迟、功率耗散和封装类型等考虑因素。

八、布局指南

- 推荐将驱动器设备尽可能靠近功率器件放置,以最小化高电流迹线的长度。

- 推荐在VDD和GND之间放置低ESR和ESL电容器,并尽可能靠近IC。

- 最小化开通和关断电流回路的寄生电感。

-

UCC27512-EP:高性能单通道低侧栅极驱动器2026-01-09 802

-

UCC27517A 具有 5V UVLO 和负输入电压处理能力的 4A/4A 单通道栅极驱动器数据手册2025-05-20 1433

-

UCC27511A 具有 5V UVLO、分离输出、5V IN 处理能力的 4A/8A 单通道栅极驱动器数据手册2025-05-19 996

-

具有UVLO的5A、5A光耦兼容单通道功能隔离式栅极驱动器UCC23113数据表2024-03-22 609

-

具有4A峰值拉电流和8A峰值灌电流的单通道、高速、低侧栅极驱动器UCC27511A数据表2024-03-21 503

-

【精选】【栅极驱动IC】24V 4A 拉电流、8A 灌电流 单通道驱动器2022-07-26 4750

-

UCC27512 4A/8A Single Channel High-speed Low-side Gate Driver2018-10-16 648

全部0条评论

快来发表一下你的评论吧 !