UCC27526 具有 5V UVLO、使能和双 TTL 输入的 5A/5A 双通道栅极驱动器数据手册

描述

UCC2752x 系列器件是双通道、高速、低侧栅极驱动器器件,能够有效驱动 MOSFET 和 IGBT 电源开关。UCC2752x 采用一种从本质上就将击穿电流降至最低的设计,可向容性负载提供高达 5A 拉电流和 5A 灌电流的高峰值电流脉冲,同时具有轨到轨驱动能力和极小的传播延迟(通常为 13ns)。此外,驱动器具有两个通道之间的匹配内部传播延迟。这些 delay 非常适合需要具有关键时序的双栅极驱动的 应用,例如 synchronous rectifier。这还允许将两个通道并联,以有效地提高电流驱动能力,或用一个输入信号驱动两个并联的开关。输入引脚阈值基于 TTL 和 CMOS 兼容的低电压逻辑,该逻辑是固定的,独立于 VDD 电源电压。高阈值和低阈值之间的宽滞后提供了出色的抗噪性。

*附件:ucc27526.pdf

UCC2752x 系列提供三个标准逻辑选项的组合 — 双反相、双同相、一个反相和一个同相驱动器。UCC27526 采用双输入设计,可为每个通道提供灵活的反相 (IN– 引脚) 和非反相 (IN+ 引脚) 配置。IN+ 或 IN– 引脚控制驱动器输出的状态。未使用的 input 引脚用于 enable 和 disable 功能。为安全起见,UCC2752x 系列中所有器件的输入引脚上的内部上拉和下拉电阻器可确保在输入引脚处于浮动状态时,输出保持为低电平。UCC27523 和 UCC27525 器件具有使能引脚(ENA 和 ENB),可以更好地控制驱动程序应用程序的运行。引脚在内部上拉至 VDD 以实现高电平有效逻辑,并保持开放状态以进行标准作。

UCC2752x 系列器件采用 SOIC-8 (D)、带外露焊盘 (DGN) 的 MSOP-8 封装和带外露焊盘 (DSD) 的 3mm × 3mm WSON-8 封装。UCC27526仅提供 3mm × 3mm WSON (DSD) 封装。

特性

- 行业标准引脚布局

- 两个独立的栅极驱动通道

- 5A 峰值拉电流和灌电流驱动电流

- 每个输出的独立启用功能

- TTL 和 CMOS 兼容逻辑阈值,与电源电压无关

- 具有高抗噪能力的迟滞逻辑阈值

- 输入和使能引脚电压电平不受 VDD 引脚偏置电源电压的限制

- 4.5V 至 18V 单电源范围

- 在 VDD-UVLO 期间,输出保持低电平(确保在上电和断电时无毛刺运行)

- 快速传播延迟 (典型值为 13ns)

- 快速上升和下降时间(典型值为 7ns 和 6ns)

- 两个通道之间的 1ns 典型延迟匹配

- 两个输出并联,以实现更高的驱动电流

- 当输入悬空时,输出保持低电平

- PDIP (8)、SOIC (8)、MSOP (8) PowerPAD™ 和 3mm × 3mm WSON-8 封装选项

- 工作温度范围为 –40°C 至 140°C

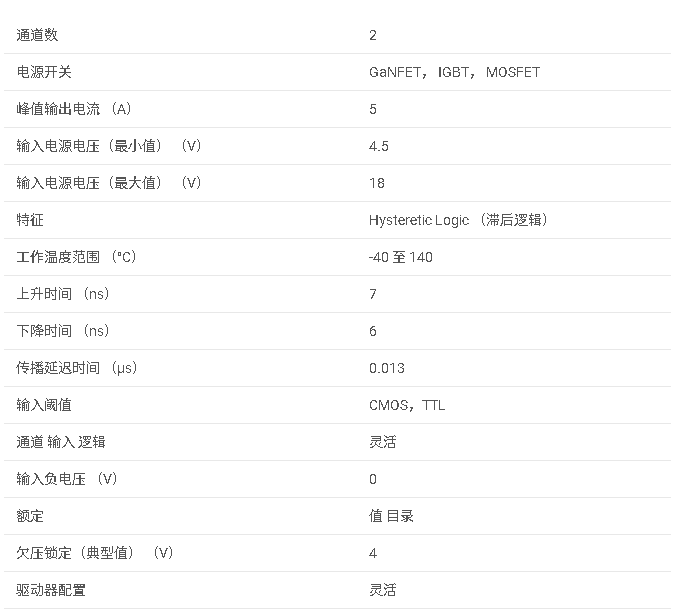

参数

方框图

一、产品概述

- 型号:UCC

- 类型:双通道、高速、低侧栅极驱动器

- 特点:

- 双独立栅极驱动通道

- A峰值源和沉驱动电流

- 独立使能功能

- TTL和CMOS兼容逻辑阈值

- 宽VDD工作范围:.V至V

- 输出在VDD欠压锁定(UVLO)期间保持低电平

- 低传播延迟:典型值3ns

- 通道间ns典型延迟匹配

二、应用领域

- 开关模式电源

- DC-DC转换器

- 电机控制、太阳能电源

- 新兴宽带隙功率器件(如GaN)的栅极驱动器

三、引脚配置与功能

- ENA/ENB:使能输入,高电平使能对应通道输出,低电平禁用输出,允许悬空。

- INA/INB:输入A/B,用于控制对应通道的输出状态。

- GND:地,所有信号参考此引脚。

- OUTA/OUTB:输出A/B,提供栅极驱动电流。

- VDD:偏置供电输入。

- INA+/INB+ 、 INA-/INB- (UCC特有):提供反相和非反相输入配置选项,未使用的输入引脚可作为使能功能。

四、电气特性

- VDD工作范围:.V至V

- 输入阈值:

- VIN_H(输入高阈值):典型值2.1V

- VIN_L(输入低阈值):典型值1.2V

- 输入滞回:典型值0.9V

- 输出特性:

- 峰值源/沉电流:A

- 高电平输出电压(VOH):I OUT = -0 mA时,0.5V至.V(VDD=V时)

- 低电平输出电压(VOL):I OUT = mA时,.1V至.5V(VDD=2V时)

- 传播延迟:

- 输入到输出延迟:典型值3ns(VDD=2V,C LOAD = .nF)

- 使能到输出延迟:典型值3ns(VDD=2V,C LOAD = .nF)

五、保护功能

- UVLO:欠压锁定功能,当VDD电压低于UVLO阈值时,输出被拉低。

六、设备功能模式

- 反相/非反相模式:通过选择输入引脚(IN-或IN+)来配置通道的输出逻辑。

- 使能功能:通过使能引脚(ENA/ENB)或未使用的输入引脚(IN+/IN-)来控制通道的输出状态。

七、典型应用

- 提供了典型应用电路图,展示了如何使用UCC6驱动功率MOSFET。

- 详细描述了设计要求和设计过程,包括输入输出逻辑配置、VDD偏置供电电压、峰值源和沉电流、传播延迟、使能功能等考虑因素。

八、布局指南

- 推荐将驱动器尽可能靠近功率MOSFET放置,以最小化栅极驱动回路的电感。

- 推荐在VDD和GND之间放置低ESR/ESL陶瓷电容器,以支持FET开通时的高峰值电流。

- 提供了布局示例和功率耗散考虑因素。

九、文档与支持

- 提供了相关技术文档、工具、软件和社区资源的链接。

- 提供了静电放电警示和术语表。

-

UCC27524A-Q1 具有 5V UVLO 和负输入电压处理能力的汽车类 5A/5A 双通道栅极驱动器数据手册2025-05-20 1109

-

UCC27524A1-Q1 具有 5V UVLO 和负输入电压处理能力的汽车类 5A/5A 双通道栅极驱动器数据手册2025-05-19 971

-

UCC23113 具有功能隔离 (1.2kVRMS) 的 4A/5A 单通道光兼容隔离式栅极驱动器数据手册2025-05-16 1013

-

UCC23525 具有12V UVLO的 5A/5A、5.7kVRMS、增强型单通道光兼容隔离式栅极驱动器数据手册2025-05-15 1194

-

具有-10V输入能力的30V、5A、双通道、低侧栅极驱动器UCC27624数据表2024-04-03 613

-

具有UVLO的5A、5A光耦兼容单通道功能隔离式栅极驱动器UCC23113数据表2024-03-22 608

-

UCC27526 双路 5A 高速低侧电源 MOSFET 驱动器2018-10-16 592

全部0条评论

快来发表一下你的评论吧 !