射频前端模块中使用的集成无源元件技术

描述

文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了在射频前端模块(RF-FEM)中使用的集成无源元件(IPD)技术。

集成无源元件(IPD)通过将电感、电容、天线等无源器件嵌入封装基板,显著提升了射频前端模块(RF-FEM)的性能与集成度,本文分述如下:

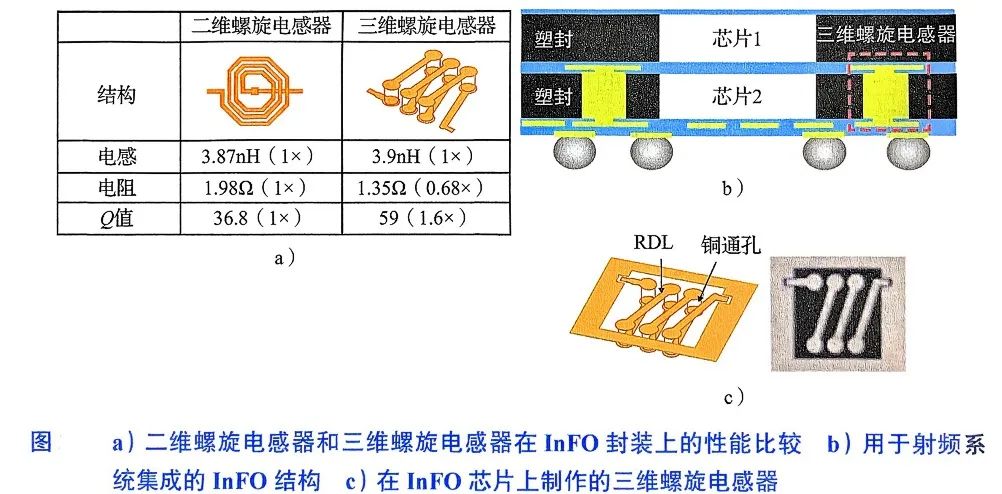

高Q值三维螺线圈电感技术

天线集成封装(AiP)技术

毫米波系统级无源元件集成

扇出式WLSI封装技术对比

晶圆级工艺驱动规模化降本

高Q值三维螺线圈电感技术

传统二维螺旋电感受限于趋肤效应与邻近效应,在毫米波频段Q值急剧下降。扇出封装通过以下创新实现性能提升:

立体结构优化

采用RDL层构建三维螺旋电感,线宽/间距(L/S)达2μm/2μm,层间通孔(VIA)间距5μm,形成紧凑型三匝线圈。与使用薄金属的二维螺旋电感器相比, 在低损耗塑封料中使用厚金属三维电感器可以获得更高的Q值。

相较二维电感,3GHz频点Q值提升1.6倍(达59),串联电阻降低68%。

材料与工艺协同

使用低损耗环氧树脂模塑料,将介质损耗降至0.1dB/mm以下;

通过电化学镀(ECP)实现20μm厚铜布线,较薄金属电感Q值提升40%。

电磁耦合抑制

正交布局双电感耦合度较平行布局降低12dB,满足多通道射频前端隔离度要求(>30dB)。

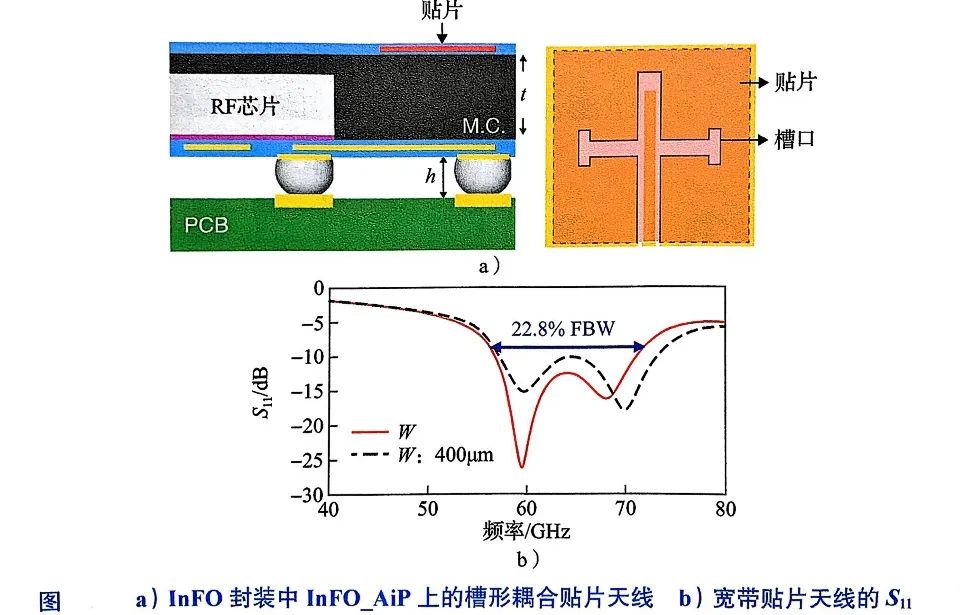

天线集成封装(AiP)技术

5G毫米波频段(24-86GHz)对天线封装提出严苛挑战,InFO技术通过三大创新实现突破:

低损耗互连通道

采用超光滑RDL表面处理(Ra<5nm),将传输损耗控制在0.3dB,较有机基板降低35%;

通过激光诱导前向转移(LIFT)技术实现芯片-天线垂直互连,过渡损耗仅0.2dB。

宽带天线设计

开发槽型耦合贴片天线,通过RDL层构建馈电网络,实现22.8%相对带宽(56.6-71.2GHz)。

天线效率达65%,辐射实现大幅度增益,满足5G NR FR2频段覆盖需求。

热机械可靠性提升

通过EMC配方优化(CTE=8ppm/K),将热循环寿命提升至1000次以上,满足车载毫米波雷达可靠性要求。

毫米波系统级无源元件集成

InFO技术实现从电感到滤波器的全无源元件集成,典型应用包括:

高性能电感阵列

构建开口尺寸100μm的单匝线圈电感,5-49GHz频段Q值>20,自谐振频率(SRF)达75GHz;

通过多层RDL堆叠,实现300pH/460pH/600pH多值电感集成,满足不同频段匹配需求。

滤波器与功率分配网络

采用环形谐振器实现32GHz/64GHz双频点滤波,插入损耗<1.5dB;

功率合成器损耗3.5dB,较片上器件降低34%,支持16通道相控阵波束成形。

传输线与阻抗匹配

共面波导(CPW)传输线损耗0.35dB,较CMOS后道工艺(BEOL)降低30%;

通过渐变线宽设计实现50Ω阻抗匹配,回波损耗>15dB。

随着5G-Advanced与6G技术演进,IPD技术正从单一元件集成向全频段覆盖、多功能融合方向发展,推动射频前端模块尺寸缩小50%以上,功耗降低40%。

扇出式WLSI封装技术对比

为全面评估扇出式晶圆级系统集成(WLSI)封装的竞争力,本研究对比了InFO PoP与倒装芯片PoP(FC_PoP)、高带宽存储器FC-HMB PoP及硅通孔(TSV)3D IC在信号/电源完整性、热管理、外形尺寸及成本等关键指标。

InFO PoP通过以下技术实现信号完整性提升

超细线宽布线:采用1μm/1μm L/S RDL,较FC PoP(5μm/5μm)信号路径缩短30%,串扰降低15dB;

阵列化BGA设计:将传统外围引脚转换为12×12阵列布局,使电源/地网络覆盖面积提升40%,同步开关噪声(SSN)降低40%;

嵌入式去耦电容:在RDL层间集成MIM电容(容值密度0.5nF/mm²),将电源噪声抑制至20mV以下。

相较之下,FC-HMB PoP虽通过额外基板实现BGA阵列,但受限于有机基板介电损耗(Dk≈3.8),60GHz频段插入损耗达1.2dB,较InFO PoP高出0.7dB。

热管理:直接散热通道实现低温升

InFO PoP的热优势源于:

低热阻路径:逻辑芯片直接贴装于PCB,结-环境热阻仅45℃/W,较FC PoP(Ψja=65℃/W)降低30%;

漏电流抑制:在1.2V工作电压下,结漏电流(Ioff)仅0.8nA,较3D IC(Ioff=3.2nA)减少75%;

功率上限提升:允许SoC功耗达8W,较FC PoP提升23%,支持高性能计算(HPC)核心频率突破3.5GHz。

FC-HMB PoP虽通过多层基板实现热扩散,但总热容增加导致瞬态热时间常数(τ)延长至120ms,较InFO PoP(τ=85ms)响应速度降低29%。

外形尺寸:无基板设计突破厚度极限

无基板架构:总厚度仅0.8mm,较FC PoP(1.0mm)减薄20%,较3D IC(0.9mm)减薄11%;

垂直互连优化:采用铜柱通孔(Cu TIV)替代微凸点,z轴互连高度压缩至50μm,较FC PoP(100μm)降低50%;

模塑料减薄技术:通过激光解键合(Laser Debonding)实现EMC厚度30μm,满足可折叠设备铰链区封装需求。

晶圆级工艺驱动规模化降本

InFO PoP的成本优势

工艺整合:利用WLSI平台共享RDL、TIV及IPD工艺,较FC PoP减少30%工艺步骤;

良率提升:通过芯片先置(Die-First)方案与预补偿算法,使12英寸晶圆级封装良率达96%,较3D IC(82%)提升显著;

材料复用:采用与CMOS后道工艺兼容的低损耗EMC(Dk=3.2),较FC-HMB PoP专用基板材料成本降低40%。

市场周期分析显示,InFO PoP从设计到量产仅需16周,较FC PoP缩短40%,满足5G终端快速迭代需求。

综上所述,InFO PoP通过超细RDL、直接散热通道及晶圆级工艺整合,在性能、功耗、尺寸及成本四维指标上形成综合优势,确立了其在移动计算与边缘AI领域的标杆地位。

-

集成无源元件技术对PCB技术的影响2018-09-11 1951

-

无源元件与RF有源元件集成的策略介绍2019-06-25 1476

-

什么是集成无源元件?对PCB技术发展产生了什么影响?2019-08-02 3426

-

手机射频技术和射频模块有什么关键元件?2019-08-12 4323

-

手机射频技术有什么关键元件?2019-08-26 3051

-

什么是理想无源元件2009-06-30 4427

-

无源元件介绍2016-06-29 1076

-

cdma射频前端的智能集成2017-08-03 1064

-

集成无源元件对PCB技术发展的影响分析2017-12-01 1446

-

射频工艺和手机射频元件的集成2017-12-07 944

-

集成无源元件对PCB技术发展有什么样的影响2020-10-15 942

-

集成无源元件(IPC)简化了封装中的信号调节2022-08-09 2921

-

集成无源元件的制备工艺2022-09-15 3963

-

集成无源元件对PCB技术发展的影响2023-11-15 1899

-

集成无源元件的电源管理集成电路2023-11-28 2014

全部0条评论

快来发表一下你的评论吧 !