IGBT功率模块动态测试中夹具杂散电感的影响

描述

在IGBT功率模块的动态测试中,夹具的杂散电感(Stray Inductance,Lσ)是影响测试结果准确性的核心因素。杂散电感由测试夹具的layout、材料及连接方式引入,会导致开关波形畸变、电压尖峰升高及损耗测量偏差。

一、杂散电感对动态测试的影响机制

开关损耗与电压尖峰

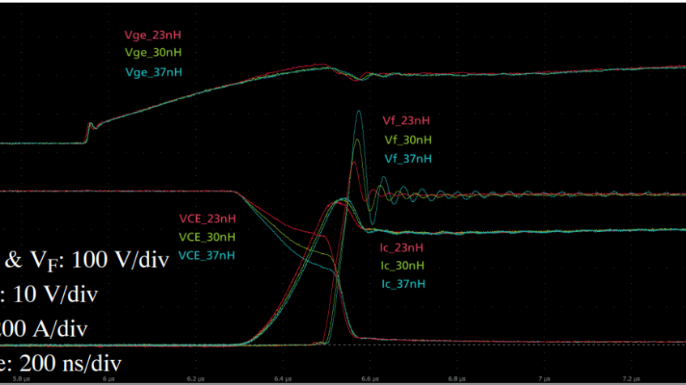

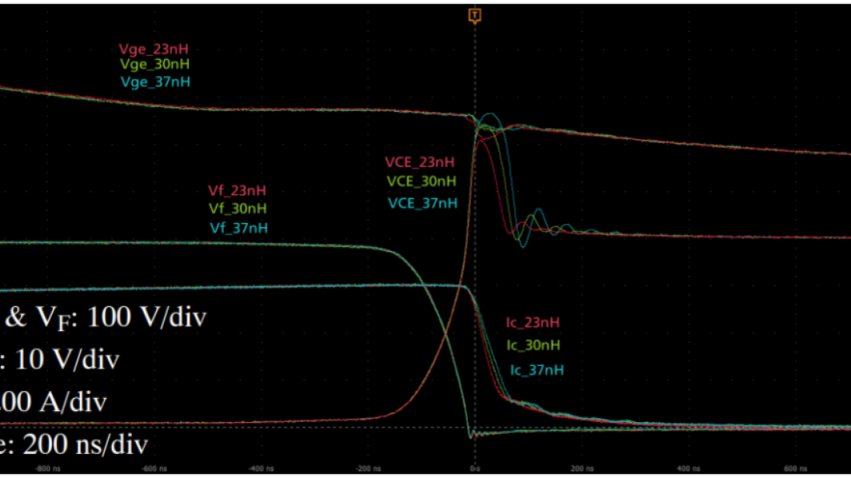

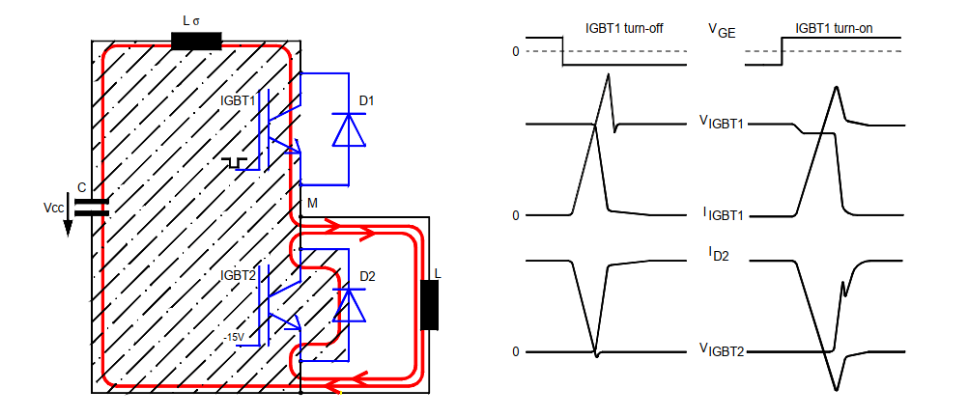

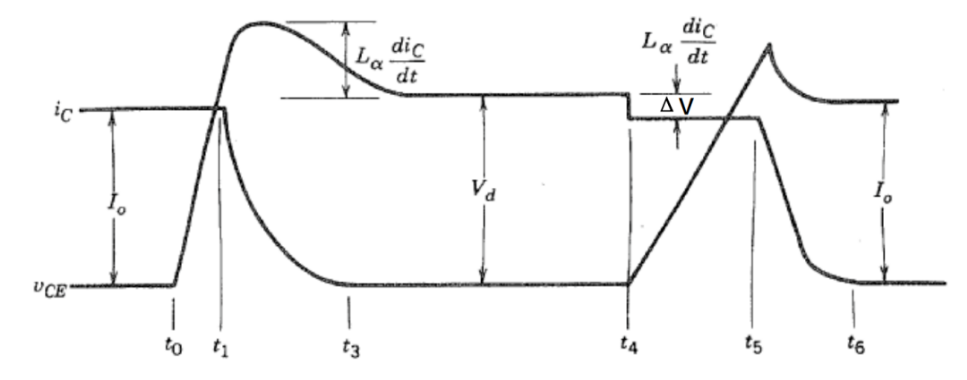

●导通阶段:杂散电感与电流变化率(di/dt)相互作用,在导通瞬间产生感应电压(Lσ⋅di/dt),导致IGBT的集-射极电压(VCE)压降增大。高杂感会降低导通di/dt,减少导通损耗(Eon),但可能引发振荡,加剧电磁干扰(EMI)。

●关断阶段:关断时的高di/dt在杂感上产生反向电压尖峰(Vpeak=Lσ⋅di/dt+VDC),可能超过模块的反向偏置安全工作区(RBSOA)限制。例如,当杂感从23nH增至50nH时,VCE峰值可升高15%~20%,需增大关断栅极电阻(RG(off))以抑制过冲。

二、杂感测量与夹具设计优化

1. 杂感测量方法

●双脉冲测试法:通过测量IGBT导通或关断时的电压降(ΔV)与电流变化率(di/dt),计算杂感值(Lσ=ΔV/di/dt)。导通暂态因干扰较少,更适合精确测量。

2.低感夹具设计原则

●对称布局与层叠结构:采用对称母排布局(如镜像对称或星型布局)可抵消部分磁场,降低环路电感。

●低阻抗材料:使用低电阻探针,减少导体自身电感。同时,缩短电流回路长度,避免锐角走线以降低分布电感。

●栅极驱动优化:根据杂感调整栅极电阻(RG)。

夹具杂散电感是IGBT动态测试的核心干扰源,直接影响开关损耗、电压应力。通过低感夹具设计、栅极参数优化及标准化测试流程,可显著提升测试精度与模块评估可靠性。未来需进一步探索杂感与多物理场耦合机制,推动测试技术向高精度、高鲁棒性方向发展。

-

杂散电感对IGBT开关过程的影响(2)2025-04-28 1512

-

杂散电感对IGBT开关过程的影响(1)2025-04-22 2138

-

一文详解杂散电感对SiC和IGBT功率模块开关特性的影响2024-03-08 3620

-

如何测量功率回路中的杂散电感2024-03-07 2572

-

什么是无杂散动态范围 (SFDR)?为什么SFDR很重要?2023-10-31 11295

-

如何测量IGBT换流回路中杂散电感?2023-02-07 6155

-

为什么要做杂散测试?2022-09-16 5705

-

模块数据手册中杂散电感的定义方法2021-10-13 6130

-

认识宽带GSPS ADC中的无杂散动态范围2018-11-01 1755

-

变流器母排杂散电感优化方法2018-03-07 1492

-

压接式IGBT模块的动态特性测试平台设计及杂散参数提取2017-12-26 1810

-

杂散电感对高效IGBT4逆变器设计的影响2012-08-13 2484

-

无杂散动态范围(SFDR)2011-01-01 14449

-

有效抑制IGBT模块应用中的过电压2010-03-14 858

全部0条评论

快来发表一下你的评论吧 !