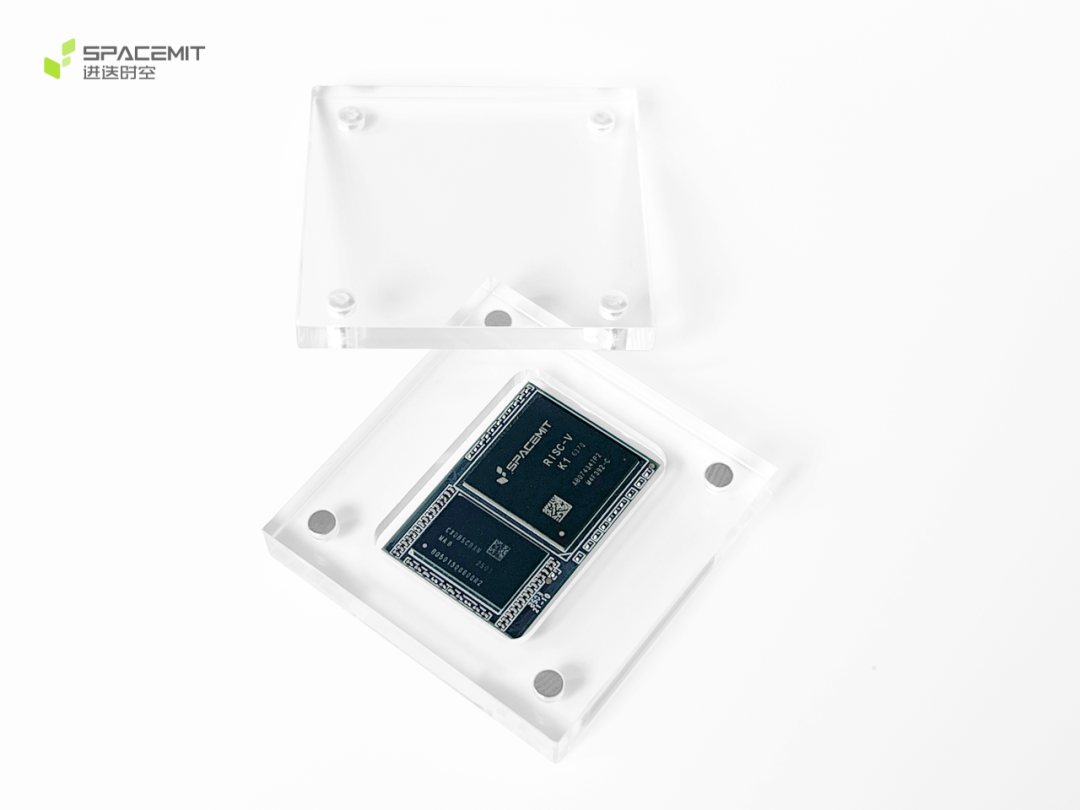

高度集成,基于RISC-V AI CPU芯片K1的PsP封装CoM产品发布

描述

进迭时空推出首款PsP(Package-side-Package)封装CoM(Computer-on-Module)产品B1,集成RISC-V AI CPU芯片K1、LPDDR4x芯片和无源器件,重布线DDR接口信号,重排布信号电源ball。通过进一步优化硬件解决方案,可以协助解决客户设计DDR模板的困难,缩短客户产品开发周期,助力RISC-V生态建设。

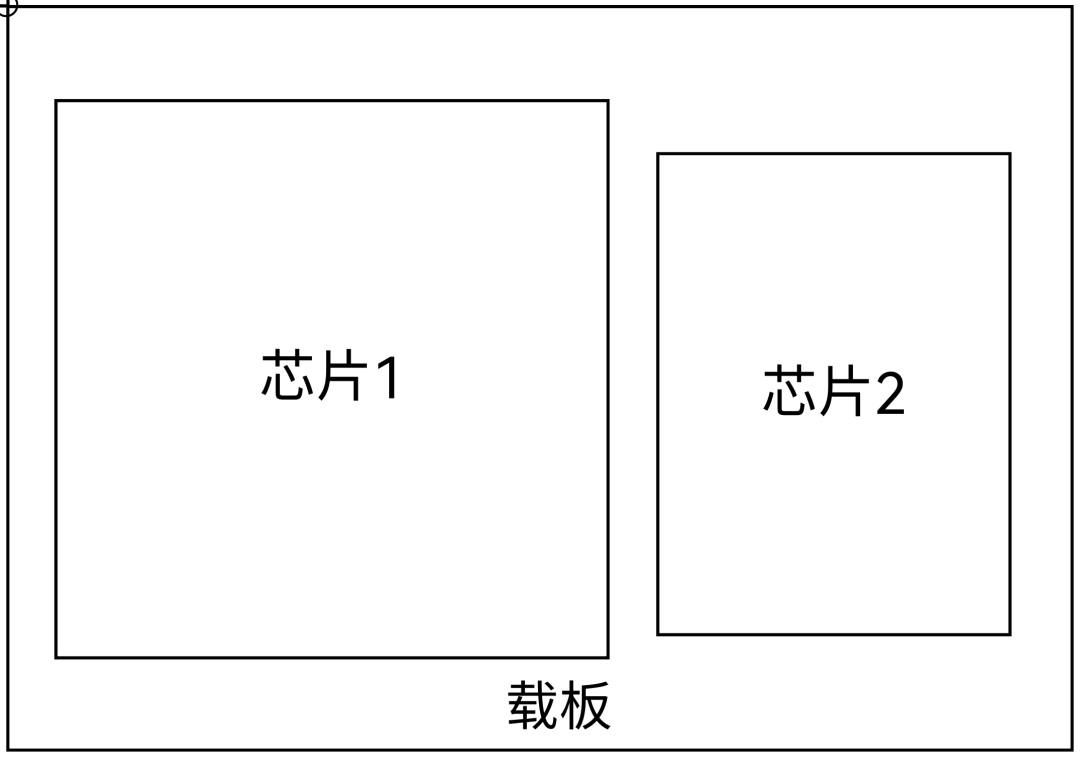

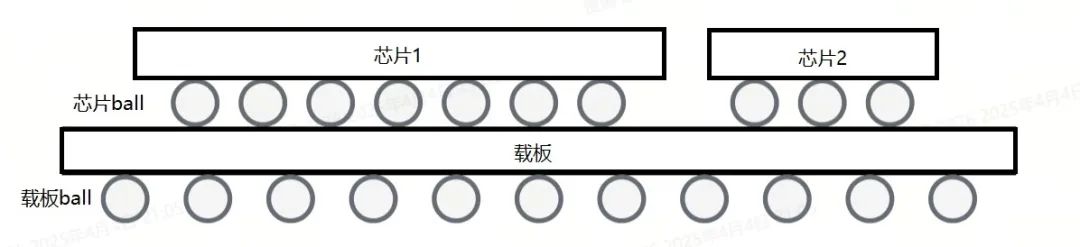

B1产品结构

(a)顶视图

(b)剖视图

B1产品规格

▲

CPU:RISC-V AI CPU芯片K1

▲

AI:CPU融合2.0Tops

▲

DDR:4GB/8GB/16GB容量;2666MT/s数据率

▲

接口:丰富接口组合,满足多样连接需求

视频类:

MIPI-DSI 4lane;HDMI 1.4;MIPI-CSI 4+4(2+2)lane

存储类:

2*SDIO3.0;MMC5.1;QSPI

控制类:

4*SPI;4*I2S;10*I2C;2*CANFD;30*PWM;12*UART

高速类:

2*USB2.0;1*USB3.0 combo PCIe2.1 x1;2*PCIe2.1 x2;2*GMAC

▲

封装:

类型:PsP-BGA Package

引脚数:568-pin

尺寸:23mm×33mm×2.4mm

间距:1mm pitch

焊球尺寸:0.6mm

B1产品优势

更优的SIPI性能

① 重布线DDR接口信号,B1缩短了DDR芯片与K1芯片的物理距离,信号传输路径减小约50%。

② 重排布信号ball,所有信号均能在Top层扇出,差分信号支持包地。

③ CORE电源和DDR电源ball数量,相比K1翻倍;支持底板Bottom层添加0603大电容。

更短的开发周期

① DDR模板layout和SIPI仿真,一般不少于15天。B1不需要再进行DDR模板layout和SIPI仿真,可以节省至少15天的开发时间。

② B1支持4层通孔底板设计,相比K1,量产制板时间可省约3天。

③ B1精简电源数量为15路,相比K1减少约50%,只需2层就能完成所有信号电源的扇出,显著降低了layout难度,缩短了layout时间。

更少的开发问题

B1集成确定型号的LPDDR4x芯片,经过严格的稳定性和可靠性测试,提前解决了DDR模板问题,客户开发和量产中将不会为DDR问题而困扰。

更低的量产成本

随着B1生产量上升,相比客户单独采购,有机会获取更优惠的LPDDR4x芯片价格,为客户争取到量产成本降低的实际收益。

-

risc-v多核芯片在AI方面的应用2024-04-28 960

-

香蕉派 BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片设计2024-07-30 1621

-

进迭时空 K1 系列 8 核 64 位 RISC - V AI CPU 芯片介绍2025-01-06 3566

-

香蕉派 BPI-CM6 工业级核心板采用进迭时空K1 8核 RISC-V 芯片开发2025-03-25 3797

-

大象机器人携手进迭时空推出 RISC-V 全栈开源六轴机械臂产品2025-04-25 7322

-

【CIE全国RISC-V创新应用大赛】基于 K1 AI CPU 的大模型部署落地2025-11-27 1600

-

探索RISC-V在机器人领域的潜力2025-12-03 953

-

Banana Pi 开源社区联合进迭时空发布最新RISC-V芯片K3开发套件:BPI-SM10(K3-CoM260)2026-01-30 498

-

RISC-V应用领域的拓展2021-06-18 2716

-

4款玄铁RISC-V芯片亮相2022-03-08 2961

-

阿里平头哥发布首个 RISC-V AI 软硬全栈平台2023-08-26 809

-

香蕉派发布RISC-V架构BPI-F3开发板2024-02-03 2220

-

Banana Pi BPI-F3 进迭时空 RISC-V K1芯片开发板支持8G/16G内存2024-07-23 1939

-

进迭时空亮相RISC-V产业发展大会:新AI CPU引领大模型时代2024-12-31 1436

-

Canonical 与进迭时空携手:Ubuntu 全面支持 K3/K1 RISC-V AI CPU 计算平台2026-02-06 27352

全部0条评论

快来发表一下你的评论吧 !