浮思特 | 一文读懂何为超结MOSFET (Super Junction MOSFET)

描述

在功率半导体领域,突破硅材料的物理极限一直是工程师们的终极挑战。随着电力电子设备向高压、高效方向快速发展,传统MOSFET结构已逐渐触及性能天花板。本文将深入解析超结MOSFET技术如何通过创新的纵向电荷补偿机制,成功打破存在数十年的"硅极限"定律。

硅极限 (Silicon Limit)

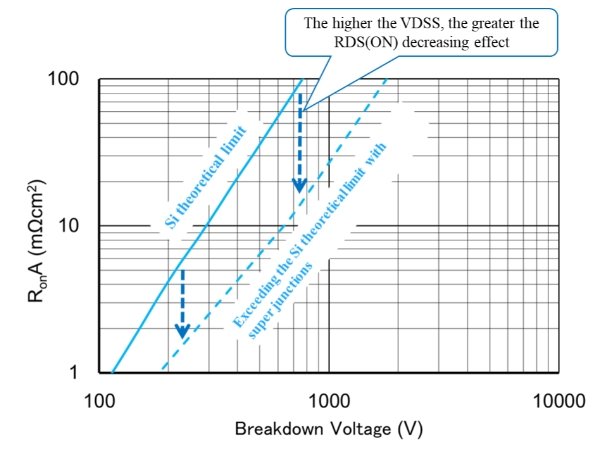

在功率MOSFET领域,存在着一个被称为“硅极限”(理论极限)的瓶颈。其核心在于:即使将除漂移层以外的所有电阻降至接近于零,由于漂移层本身固有的电阻限制,器件的导通电阻 RDS(ON) 也无法进一步降低。这就是所谓的“硅极限”。

对于传统的平面栅MOSFET,其导通电阻 RDS(ON) 与漏源击穿电压 VDSS 的关系符合 VDSS^2.5 ∝ RDS(ON) 的计算公式。这意味着:

VDSS 增加至 2 倍 ⇒ RDS(ON) 增加至约 5.6 倍

VDSS 增加至 10 倍 ⇒ RDS(ON) 增加至约 316 倍

对于低耐压 (VDSS) 的 MOSFET,其性能距离理论极限尚有一定空间。然而,对于高耐压 MOSFET,其性能早在多年前就已接近理论极限。因此,市场对高耐压 MOSFET 实现新的技术突破有着强烈的需求。

⇒ 超结结构正是旨在突破这一硅极限、同时继续基于硅材料的一项创新技术。

超结结构带来的 RDS(ON) 降低优势

超级结原理

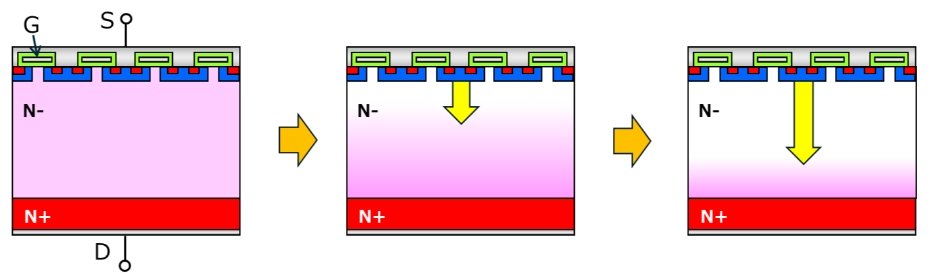

传统结构 MOSFET:

其漏源击穿电压 (VDSS) 依赖于外加电压下耗尽层的纵向扩展。耗尽层的扩展程度(即耗尽层厚度)决定了其耐压能力。因此,在高耐压 MOSFET 中,漂移层的杂质浓度不能过高。这就导致 VDSS 越高,漂移层电阻越大,RDS(ON) 也越高。

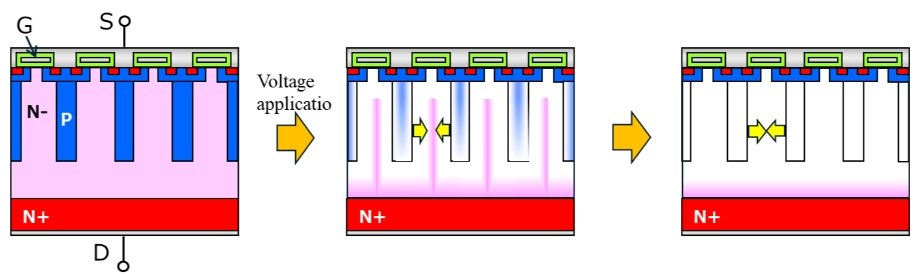

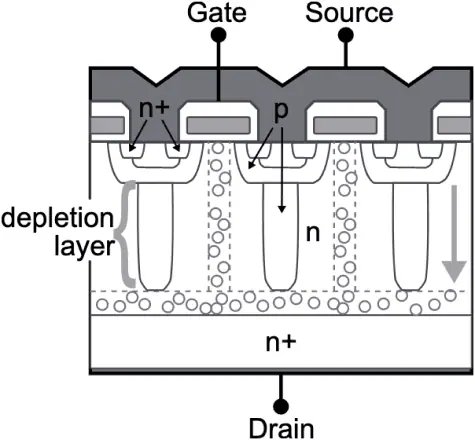

超结结构 MOSFET:

在该结构中,漂移层内部精确地交替排列着纵向的 N 型柱和 P 型柱(通常通过深沟槽刻蚀工艺形成,例如 Semihow 的超结 MOSFET 技术就采用了先进的刻蚀工艺来构建这些柱体)。当施加电压时,耗尽层主要在相邻的 N 柱和 P 柱之间横向扩展,并迅速相接,最终形成一个厚度等于沟槽深度的完整耗尽层。

由于耗尽层只需扩展到柱间距的一半即可合并,其最终形成的耗尽层厚度等同于沟槽的深度。这种结构使得耗尽层的扩展距离更短且更有效,允许大幅提高漂移层的杂质浓度(可达传统结构的约 5 倍),从而实现 RDS(ON) 的显著降低。

从上述原理可以看出,制造尽可能窄间距和深度的沟槽至关重要。超结 MOSFET 正是通过这种与传统 MOSFET 不同的耐压机制,成功突破了硅材料的理论极限,实现了更高的性能表现。Semihow 的超结 MOSFET 技术正是基于对这一核心原理的深刻理解,专注于优化沟槽结构和制造工艺,以有效降低高耐压器件的导通电阻。

传统的平面架构

首个采用平面工艺的功率MOSFET器件于上世纪70年代问世。制造平面MOSFET的过程涉及多种工艺,并需要利用多种氧化物、杂质和抗蚀剂方可获得最终产品。

平面制造步骤:

1、在晶圆上喷涂氧化膜

2、在晶圆表面添加p层掺杂剂,并通过热处理将其扩散到晶圆中

3、应用抗蚀剂/

4、在晶圆表面添加n+掺杂剂,并通过热处理将其扩散到晶圆中

5、清除掉抗蚀剂

超结MOSFET架构

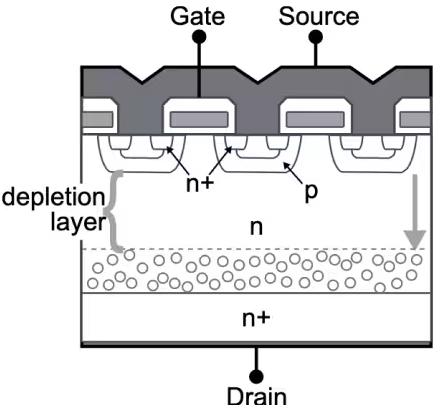

超结MOSFET可在晶圆中蚀刻出深而窄的沟槽,因而能够突破平面设计的限制。该架构可显著抑制耗尽区的扩大,因而能够有效提升掺杂浓度并降低RDS(on)。

麦克斯韦方程表明电场的斜率等于电荷密度r除以介电常数e:

dE/dy=r/e

电压V是E的积分,也可表示为E曲线下的阴影面积为y的函数。比较这两个图后我们发现,p型柱的引入明显改变了电场分布,并使关闭状态下可以维持的电压升高。因此在给定电压的情况下,可降低漏极电阻率,从而降低导通电阻。

超结MOSFET技术的出现,标志着功率半导体设计从二维平面结构向三维立体结构的范式转变。通过精密的柱状交替掺杂和独特的横向耗尽机制,这项技术不仅实现了理论上的突破,更在实际应用中展现出显著的效率优势。随着Semihow等厂商在深沟槽刻蚀工艺上的持续创新,超结MOSFET正在5G基站、新能源逆变器、工业电源等高压应用场景中加速替代传统解决方案。

-

瑞萨600V耐压超结MOSFET 导通电阻仅为150mΩ2012-06-26 1664

-

300nm晶圆首次用于制造功率器件,英飞凌推出超结MOSFET2013-02-25 2072

-

超结MOSFET的基本结构与工作原理2026-01-04 1843

-

三分钟读懂超级结MOSFET2017-08-09 4352

-

超级结MOSFET的优势2018-10-17 3196

-

超级结MOSFET2018-11-28 4064

-

超结理论的产生与发展及其对高压MOSFET器件设计的影响2009-12-13 706

-

600V MOSFET继续扩展Super Junction2010-01-26 1440

-

维安高压超结MOSFET,轻松解决LED电源浪涌2022-12-30 1508

-

SiC-MOSFET和功率晶体管的结构与特征比较2023-02-08 1309

-

R课堂 | 600V耐压Super Junction MOSFET PrestoMOS™产品阵容又增新品2023-07-12 1620

-

超结MOSFET的结构和优势2024-10-15 2588

-

超结MOSFET升级至650V碳化硅MOSFET的根本驱动力分析2025-03-01 1061

-

浮思特|SiC MOSFET与普通MOSFET的区别及应用分析2025-09-04 662

全部0条评论

快来发表一下你的评论吧 !