verilog是什么_verilog的用途和特征是什么

电子常识

描述

verilog是什么

Verilog一般指Verilog HDL。Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

Verilog发展历史

1、1981年Gateway Automation(GDA)硬件描述语言公司成立。

2、1983年该公司的Philip Moorby首创了Verilog HDL,Moorby后来成为Verrlog HDL-XL的主要设计者和Cadence公司的第一合伙人。

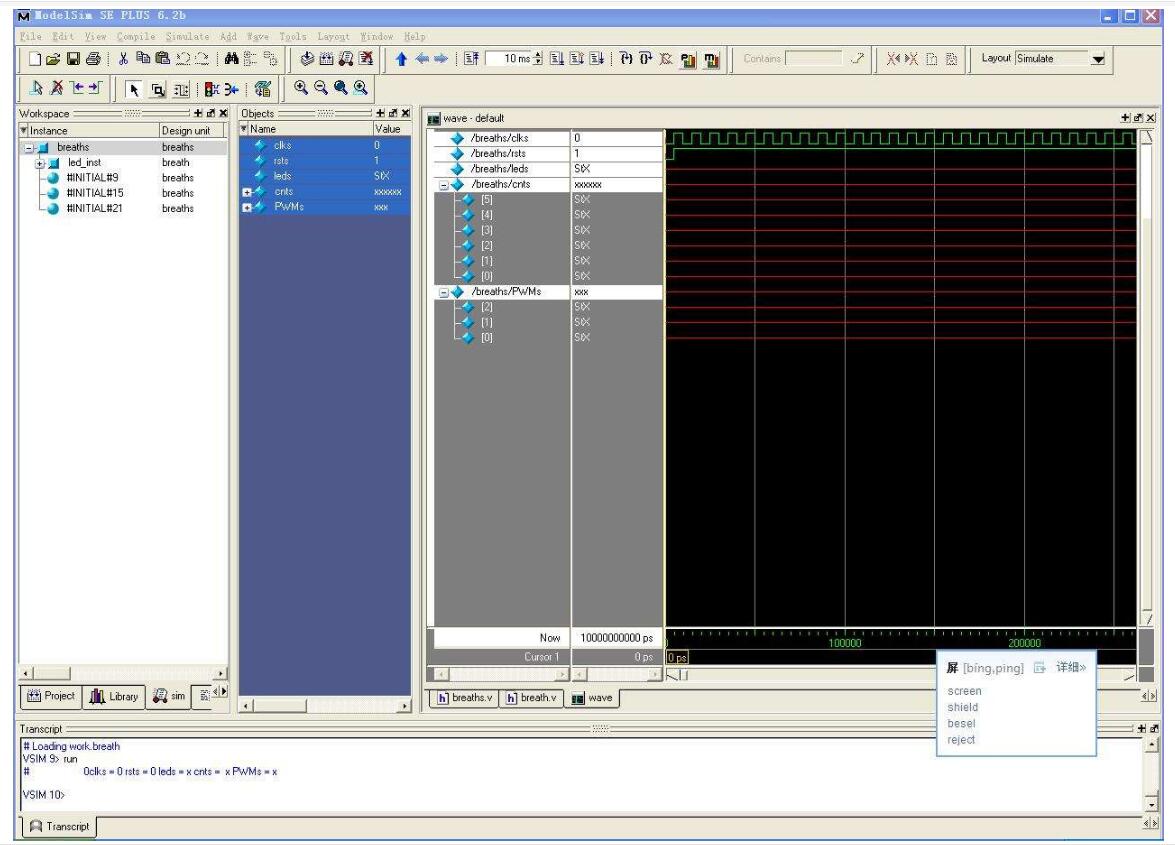

3、1984-1985年Moorby设计出第一个关于Verilog HDL的仿真器。

4、1986年Moorby对Verilog HDL的发展又做出另一个巨大的贡献,提出了用于快速门级仿真的XL算法。

5、随着Verilog HDL-XL的成功,Verilog HDL语言得到迅速发展。

6、1987年Synonsys公司开始使用Verilog HDL行为语言作为综合工具的输入。

7、1989年Cadence公司收购了Gateway公司,Verilog HDL成为Cadence公司的私有财产。

8、1990年初Cadence公司把Verilog HDL和Verilog HDL-XL分开,并公开发布了Verilog HDL.随后成立的OVI(Open Verilog HDL International)组织负责Verilog HDL的发展,OVI由Verilog HDL的使用和CAE供应商组成,制定标准。

9、1993年,几乎所有ASIC厂商都开始支持Verilog HDL,并且认为Verilog HDL-XL是最好的仿真器。同时,OVI推出2.0版本的Verilong HDL规范,IEEE接收将OVI的Verilog HDL2.0作为IEEE标准的提案。

10、1995年12月,IEEE制定了Verilog HDL的标准IEEE1364-1995.

任何新生事物的产生都有它的历史沿革,早期的硬件描述语言是以一种高级语言为基础,加上一些特殊的约定而产生的,目的是为了实现RTL级仿真,用以验证设计的正确性,而不必像在传统的手工设计过程中那样,必须等到完成样机后才能进行实测和调试。

verilog的特征

1、采用verilog HDL 进行电路设计的最大优点是设计与工艺无关系,这使得设计在进行电路设计时可以不必过多考虑工艺实现时的具体细节,只需要根据系统设计的要求施加不同的约束条件,即可设计出实际电路。

2、能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性;

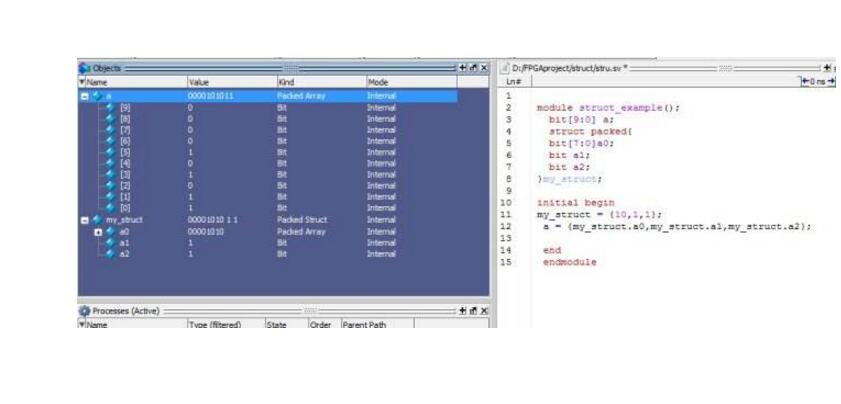

3、能够在不同的抽象层次上,如系统级、行为级、RTL (RegisterTransfer Level) 级、门级和开关级,对设计系统进行精确而简练的描述。

Verilog逻辑门级描述

逻辑门级描述的抽象级别较低,仅次于晶体管级。实际的硬件电路往往都是以逻辑门级网表作为基础构建的,而设计人员常常会在进行更高抽象级别的设计。尽管如此,逻辑门级的设计还是更接近真实电路形式。Verilog提供了一系列逻辑门原语(Primitive)供用户使用。例如,非(not)、与门(and)、或门(or)、与非门(nand)、或非(nor)、异或(xor)、同或(xnor)。逻辑门原语和模块类似,可以通过实例引用的方式使用。

Verilog晶体管级描述

Verilog能够在低抽象级别对电路进行描述,是它的一个重要特点。Verilog中提供了多种晶体管级(也称开关级)元件类型,包括N型金属氧化物半导体场效应管(关键字为nmos)、P型金属氧化物半导体场效应管(关键字为pmos)、互补式金属氧化物半导体(关键字为cmos)、带阻抗的互补式金属氧化物半导体(关键字为rcmos)、电源单元(关键字为supply1)、接地单元(关键字为supply0)等。所有的晶体管都可以设置延迟属性。设计人员可以利用这些低抽象级元件构建所需要的逻辑门或直接构成其他高级组件。

verilog的用途

Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种硬件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL成为IEEE标准,即IEEE Standard 1364-1995.

Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。与之相比,VHDL的学习要困难一些。但Verilog HDL较自由的语法,也容易造成初学者犯一些错误,这一点要注意。

-

Verilog与VHDL的比较 Verilog HDL编程技巧2024-12-17 3437

-

Verilog常用的循环语句及用途2023-05-12 4171

-

Verilog HDL程序设计案例2023-02-13 812

-

Verilog的程序框架案例2022-09-13 2004

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2407

-

Verilog教程之Verilog HDL程序设计语句和描述方式2020-12-09 1352

-

Verilog语法基础2019-03-08 13953

-

Verilog教程之Verilog的命令格式资料说明2019-01-09 1111

-

Verilog HDL入门教程之Verilog HDL数字系统设计教程2018-09-20 2458

-

Verilog实现74LS194芯片设计程序2017-12-22 7341

-

VHDL,Verilog,System verilog比较2012-01-17 1996

-

The Verilog PLI Handbook2009-07-22 691

全部0条评论

快来发表一下你的评论吧 !