MIS基板封装技术的推动者之一

电子说

描述

翻译:长电科技陈灵芝博士。陈博士多年从事MIS基板技术研究,是MIS基板封装技术的推动者之一。

MIS在模拟、功率IC和数字货币等领域作为一种新型封装方式而出现。基于一种新兴技术MIS的IC封装正在积蓄动力。 日月光(ASE)、嘉盛(Carsem)、长电科技(JCET)/ 星科金朋(STATS ChipTAC)、宇芯(Unisem)等都在开发基于MIS基板的IC封装技术,目前在模拟、功率IC、及数字货币等市场领域迅速发展。

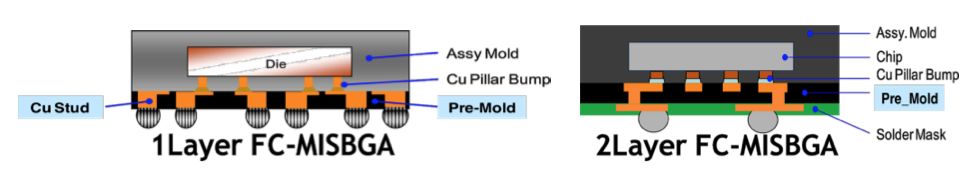

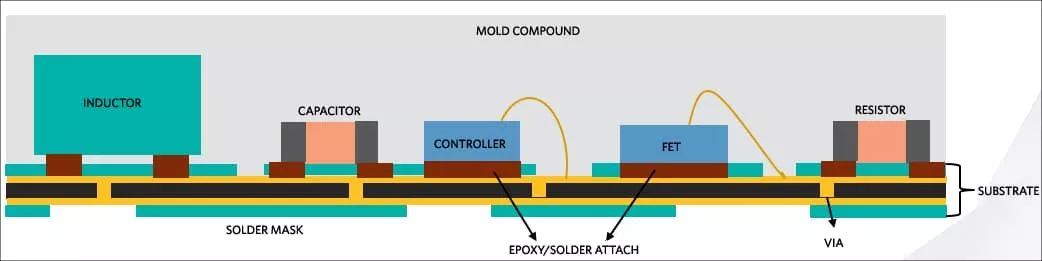

MIS封装采用特有的基板材料,开始主要用在一些特定的IC封装上。MIS基板目前有多家的供应商在进行开发及销售,因此封装厂可以从多家厂商采购,然后进行IC封装。有人认为MIS基板是一种引线框。 MIS与传统的基板不同,包含一层或多层预包封结构。每一层都通过电镀铜来进行互连,以提供在封装过程中的电性连接。MIS支持单芯片或多芯片封装,为超薄、高密度细节距封装提供方案。它可以被用于开发先进的引线框封装、倒装芯片封装、模组封装及系统级封装。

图1:预包封的MIS引线框架

图2:基于MIS的IC封装

表面上,MIS类似于扇出型(Fan-Out)晶圆级封装。它们之间最大的区别是,MIS在I/O和密度方面稍加逊色。因此,在实际封装使用中,MIS主要跟目前一些已经比较成熟的中端封装进行竞争。

MIS已经存在了近十年,但市场刚刚开始起来。“(MIS)由于其先进的布线能力和可靠性,在高、低功率应用上都很适用,” 日月光工程技术营销总监Mark Gerber说。

此外,MIS还为客户提供了一种新的封装选择,以及现有封装的一种潜在的替代方案。“出货量在这几年不断上升,”Nokibul Islam说。“可以用MIS来替代一些传统的如QFN封装或基于引线框的封装,因为MIS具有更细的布线能力,更优的电和热性能,和更小的外形。” 还有, MIS封装被锁定用于数字货币芯片的封装,进入了数字货币服务器市场。这个市场的量是非常巨大的。当然也有一些人开始考虑数字货币市场是否或者说何时可能结束。 什么是MIS? MIS是在2010年左右开发的,长电科技是最早期的开发者之一,然后将这项技术授权给其兄弟公司芯智联(MISpak)。 MISpak开发和销售MIS材料给封装厂(OSAT),其他MIS基板供应商还包括ASM、PPT、QDOS和SIMMTECH。 因此,封装厂购买MIS基板有更多的选择。然后,在封装过程中,把芯片放在MIS基板上进行封装,最后形成MIS封装。

图3:矽品的倒装MIS BGA封装(FC-MISBGA)

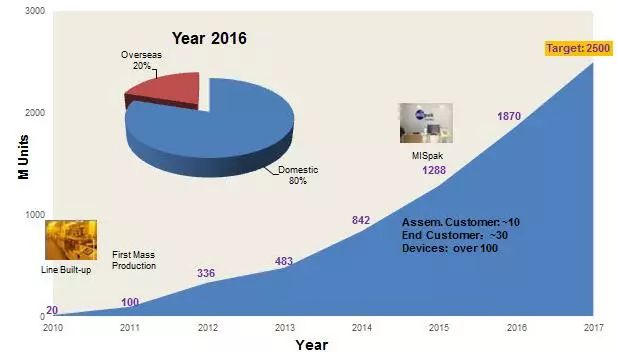

随着时间的推移, MIS业务规模开始迅速成长。2017年,仅芯智联(MISpak)一家就预计出货25亿颗,而在2010年,其出货量仅2000万颗。在MIS封装领域,芯智联(MISpak)宣称其大约有30多家终端顾客。当然这中间还没包括其他MIS供应商的出货量。

图4:芯智联MIS基板出货量

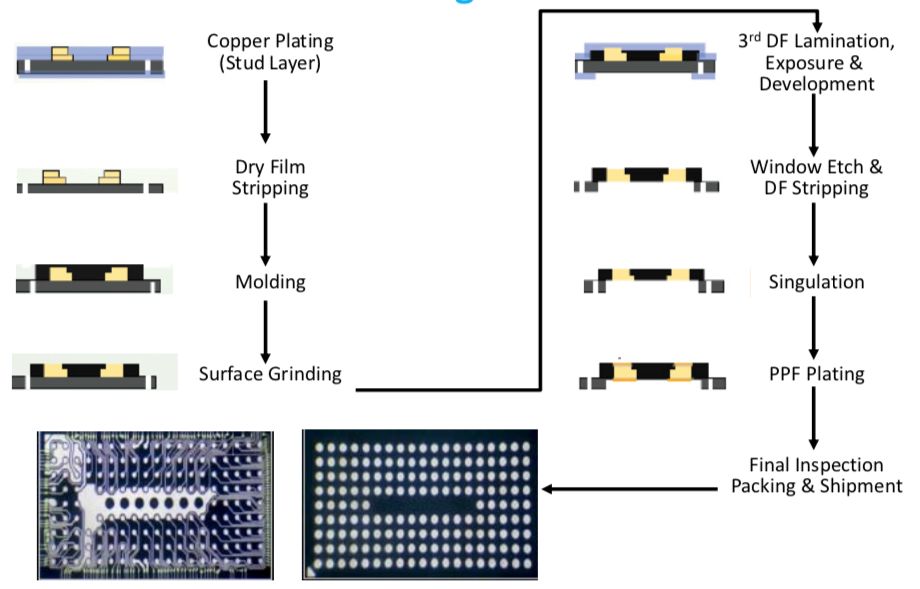

MIS与传统 IC封装基板不同。传统封装采用的是有机基板,这是基于PCB类材料的多层基板技术。在封装中,芯片置于基板之上。 “MIS技术的特点是,它是从包封技术引申发展出来的。在MIS基板中,铜布线是嵌入式的。因此,这种嵌入式结构就可以做到更细的布线,” Nokibul Islam说。 MIS还具有其他的一些特性。“它使用包封料作为各层之间的绝缘材料,” Mark Gerber说。“当你使用该类型的引线框,并在此上进行封装,那么封装的包封料与引线框的材料特性就是相似的。因此,从吸潮性或功能的角度来看就非常好。” 目前制作MIS基板的方法有多种。MIS最早是以尺寸250mmX70mm的长条形出现 。MIS制作需要经过一系列的工艺步骤,如蚀刻、研磨、光刻、包封和电镀。 比如,单层MIS工艺流程,往往从载板开始。“在金属载板上,通过电镀铜来制作基板的布线,”Nokibul Islam解释道。“所以在完成电镀铜后,下一步就是去除光阻膜工艺。” 在去膜后。“就开始进行包封。然后研磨包封料进行减薄,达到所要求的厚度。最后蚀刻载板,”Nokibul Islam说。

图5:MIS基板制造工艺流程

对于MIS封装,该技术最有优势的是薄型、I / O在150〜200之间的封装。但该技术受限于25μm左右的线宽线距,这意味着它主要面向中端应用。线宽线距是指封装中的金属布线。

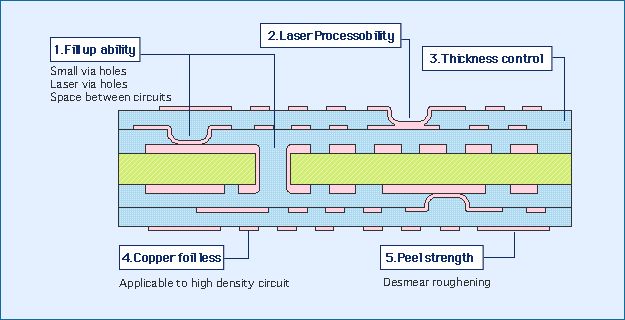

对比来看,主要用于高端应用的扇出型封装(Fan-Out),其标准密度是: I / O小于500的封装,其线宽线距在8μm以上;而高密度扇出型封装,其I / O大于500,线宽线距小于8μm。 同时,MIS材料本身相对较薄。该类基板在封装过程中容易出现翘曲及均匀性问题。产量和成本问题则另论。 “不同的应用需求在设计灵活性和封装厚度方面需要特殊的封装材料,” ASM材料业务部市场副总裁Ho Kwok Kuen说。“相比引线框架,ABiT-MIS有能力可以生产出要求高、线路复杂的预包封基板。但是,为了达到设计的解析度需要更多的工艺步骤,因此为了达到最终产品的良率目标,我们需要高度关注在每一个工艺过程中如何实现更高的良率。

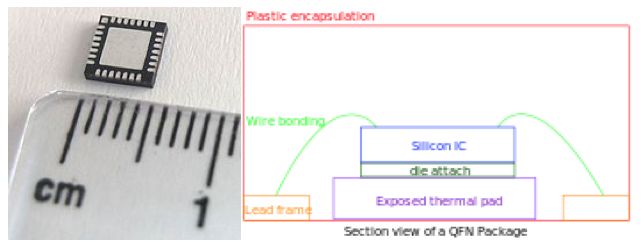

” 除了设备,ASM也提供引线框架和MIS封装材料。这里是指ASM加层互连技术(ABiT,ASM Buildup Interconnect Technology )。 尽管面临种种挑战,但是MIS市场还是迅速成长。“在过去的两年里,我们已经看到了许多客户希望使用MIS封装来满足数字货币挖矿应用的需求。”Ho说,“MIS不仅在通讯领域射频封装的市场份额不断增加,其实在电源管理和汽车应用方面的需求也在不断增加。” 同时在市场上, MIS也是面临着激烈的竞争。这里指“Fan-Out”技术,尽管MIS并不会与Fan-Out技术竞争。其实MIS主要是与引线框封装和LGA封装进行竞争。“MIS的应用领域主要是介于标准QFN封装和简单的双层基板两者之间的封装。”宇芯北美区副总裁Gil Chiu说。 引线框封装包括若干封装类型,诸如四面扁平无引线(QFN)和四面扁平封装(QFP)。引线框是金属框架,芯片粘贴在框架上,使用细导线进行连接。

图6:QFN封装

来源:维基百科

QFN是成熟、价格低廉且可靠的封装方式,因此在模拟、汽车电子、物联网、RF等市场方面,QFN的需求巨大。通常来讲,虽然QFN是一个I / O能力有限的单层技术,但是“如果你可以用QFN实现,你显然会这么做,因为QFN的成本比MIS更低,”Chiu说。“但是当你使用QFN时,你要接受间距的限制。” MIS还与LGA封装技术竞争。LGA在封装底部有用于连接的金属焊盘阵列。LGA适用于模块、处理器等产品。

图7:电源模块LGA封装结构

MIS相比LGA更便宜,但功能更少。然而,宇芯公司认为LGA有时会受高昂的材料成本、连接孔(Via)成型成本等影响。 因此,QFN和LGA都有一些缺点,这里就是MIS的用武之地。例如,IC设计公司可能会在给定的工艺节点有现成的芯片设计,且芯片封装采用QFN封装。在这个假设的例子中,供应商会面临一些挑战。“客户基本上会说,我有一个现成的方案,我不想改变我的芯片,我不希望缩小我的芯片,但我想缩小我的封装,我希望得到一个更薄、更小尺寸的封装,”Chiu说。

一种有效的解决方案就是从QFN封装转向MIS封装。通常,你可以采用与引线框封装相同的芯片,用在MIS上进行封装。MIS封装可以做到跟QFN封装类似,但MIS可以有更多的I / O和更好的性能。 采用MIS封装,基本上可以和其他封装类型一样,例如:倒装芯片、模块和SiP。“MIS技术是不同的。它本质上是一种积层工艺。它可以让你实现更密的金属布线。因此,您可以缩小封装,而同时保持相同的芯片尺寸,”Chiu说。“使用MIS,客户不必花费时间或资源来重新设计一个更小的芯片以及不必缩小芯片的外形。采用MIS,你可以让产品获得额外的。它可以让你保持与现成方案的匹配。所以,MIS在相同的成本下可以为您提供更小的封装。” “搭上”或“错过”? 一段时间以来,一些OSAT厂已经不断出货MIS封装。但是每个供应商都有不同的战略。

长电科技/星科金朋已经出货了各类基于MIS技术的Chip-on-lead、FC、模组及SiP封装产品。“MIS具有其特定的优势。最优的是低I / O数的高功率、高散热的应用。” 长电科技的Islam说。 到目前为止,业内主要出货的是线宽线距在25/25μm的单层MIS封装。“对于未来的市场,我们目前正在做更高的解析度,这意味着更细的线宽线距,以及更轻薄的外形,”Islam说。“两年以后,它可以做到15/15μm的线宽线距。” 此外,长电科技/星科金朋以及其他厂商都在全力致力于基于Ajinomoto的ABF(Ajinomoto Build-up Film)膜技术的更先进的工艺。使用激光成型和直接电镀铜,ABF可以使MIS做到线宽线距达12/12μm的多层基板,这样可以实现二层、三层及四层的多层封装。

图8:Ajinomoto 的ABF膜

“使用ABF膜,MIS的工艺流程基本完全是一样的。我们只是使用更厚的ABF膜来替代包封料,我们可以提供这种类型的多层MIS基板,”他说。“在今年年底左右我们就会开始使用基于ABF膜的两层或三层MIS基板。” 日月光的MIS封装也正在成长中。日月光的MIS技术被称为C2IM / MIS。“MIS可以让你做到型同QFN封装而同时具备精细节距布线能力的封装,” 日月光的Gerber说。“(有些客户)非常坚持使用QFN封装,但是有布线能力的限制。当你可以进行20/20μm或30/30μm的布线,这就一下子为他们提供了一层布线金属层的解决方案。” 除了C2IM / MIS,日月光还提供另一个竞争性的技术叫“ChipLast扇出封装”,这不同于现行的扇出型封装。“它本质上是一个芯片后置的工艺,这就意味着它是一个倒装芯片工艺,”Gerber说。“ChipLast扇出封装是一个根据布线密度使用两种不同绝缘材料,而只有一层金属布线的无芯基板工艺方案”。

此外,相对于MIS基板,日月光还有另一个选择方案叫做aS3 +。“aS3 +是一个嵌入式线路(ET)的无芯有机基板,这个技术也可以提供与C2IM / MIS类似优势的方案。此外,aS3 + / ET基板可以做到三层或更多层布线,而在这方面C2IM / MIS相对比较欠缺,”他说。“aS3 + / ET可以使用传统绝缘材料或ABF绝缘材料。同时由于不需要芯板材料以及其制造工艺流程和它内在的结构特点,它可以带来有利于更高速度连接的层间超低电感,同时不失成本竞争力及可靠性 ”。 对宇芯来讲,他们看到的是MIS封装的三个应用。这些封装都可以做到整体厚度达到0.33毫米或更低。 第一种应用是该公司所谓的空腔,芯片封装在这个封装体的空腔里。

“我们正在利用MIS实现介于基板封装与QFN封装之间的细间距芯片倒装封装,在这方面可以一展身手,”宇芯的Chiu如是说。“我们同样还在考虑使用MIS进行系统级封装,这对于LGA标准模块封装来说,是一个成本更低的方案。” 对于MIS来说,最大的市场是电源/功率IC。另一个驱动因素是数字货币IC封装。展望未来,MIS可能会超出这些市场。“好消息是,我们看到越来越多的常规产品也在考虑是否使用MIS封装.”Chiu补充说。

-

封装基板设计的详细步骤2025-03-12 2384

-

SMT技术:电子产品微型化的推动者2025-02-21 1659

-

迎接玻璃基板时代:TGV技术引领下一代先进封装发展2025-01-23 3700

-

玻璃基板时代,TGV技术引领基板封装2024-05-30 5928

-

芯片那么小,封装基板走线损耗能大到哪去?2023-04-07 1645

-

能量收集是新兴的物联网推动者2023-01-03 1743

-

为什么要选择陶瓷基板作为封装材料?2021-04-19 2341

-

苹果将是智能电动汽车强势的推动者2021-01-04 2356

-

封装基板的技术简介详细说明2020-07-28 1899

-

什么是封装基板2020-03-30 9424

-

关于MIS封装技术的分析介绍2019-09-02 14713

-

安防上市企业是目前人工智能+安防最有利的推动者2018-10-16 1622

-

多芯片模块的相关技术和低成本的MCM和MCM封装技术2018-08-28 2545

-

爱立信5g移动新时代的推动者2018-07-13 2036

全部0条评论

快来发表一下你的评论吧 !