基于板级封装的异构集成详解

描述

来源:学习那些事

异构集成

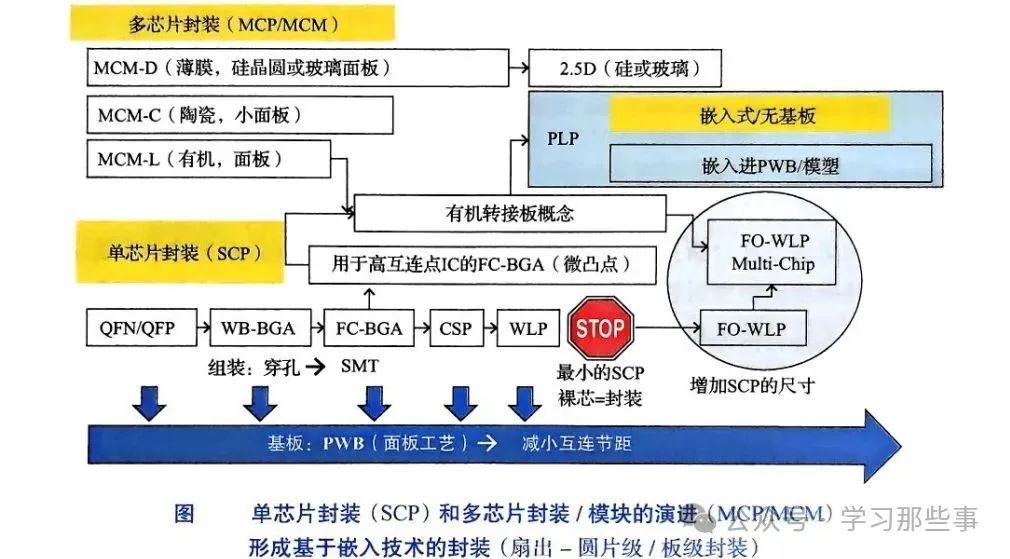

基于板级封装的异构集成作为弥合微电子与应用差距的关键方法,结合“延续摩尔”与“超越摩尔”理念,通过SiP技术集成多材料(如Si、GaN、光子器件等)裸片及无源元件,借助扇出晶圆级/板级封装等技术,实现更低成本、风险及更高灵活性,推动电子系统可靠性向十亿分之几故障率发展。

本文分述如下:

扇出板级封装技术介绍

板级封装的经济效益分析

扇出板级封装技术介绍

扇出板级封装(FO-PLP)作为扇出晶圆级封装(FO-WLP)的技术延伸,通过将有源和无源元件嵌入模塑料中,显著提升了布线面积并推动了封装的小型化潜力。其核心优势在于无基板设计,采用薄膜金属化替代传统引线键合或倒装芯片(FC)凸点,实现了更短的芯片间直接互连,从而降低了热阻、提升了性能并减少了寄生效应,尤其在高频应用中,相比FC-BGA封装具有更低的电感。

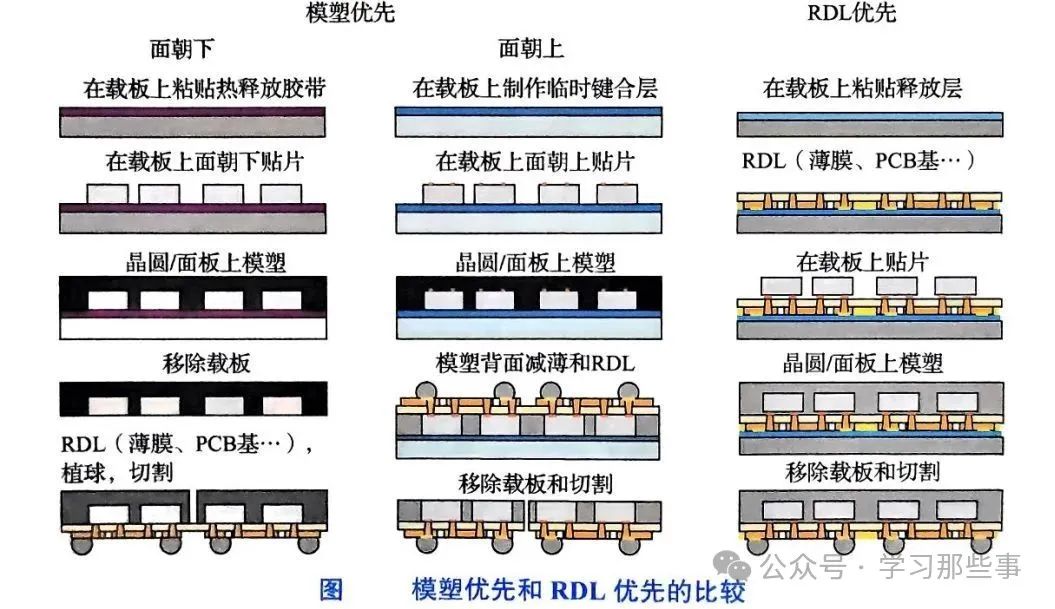

FO-PLP的工艺流程主要分为模塑优先和RDL(再布线层)优先两类:模塑优先工艺中,面朝下路径通过直接电镀通孔具有最短的互连,在RF和毫米波领域表现最优,因互连路径最短、高频损耗最低;面朝上路径则需铜柱互连,而RDL优先工艺需焊料互连,两者均需额外聚合物/底部填充层。

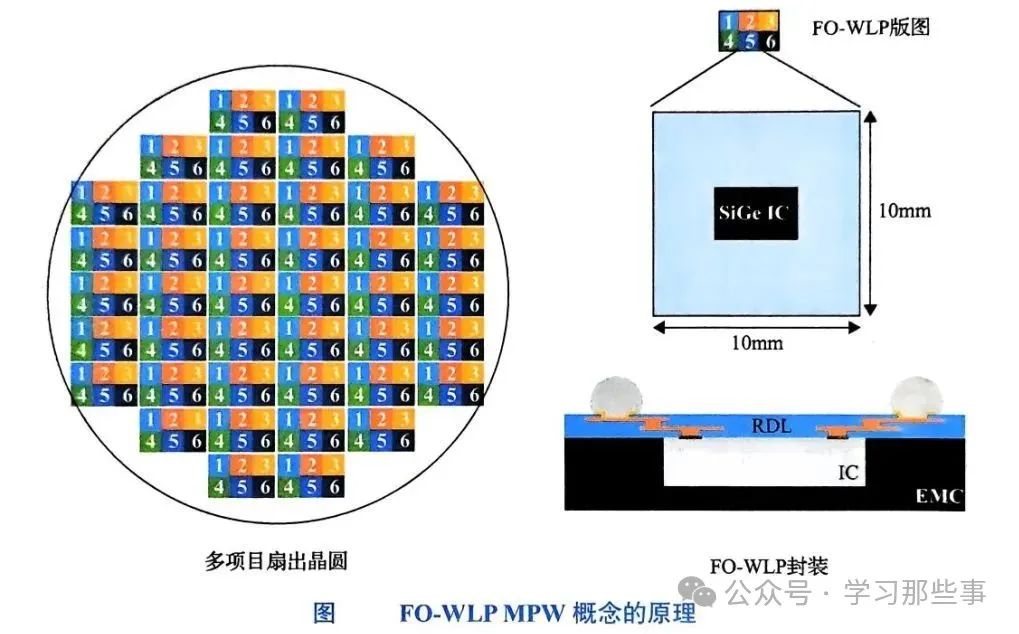

FO-PLP的异构集成能力尤为突出,可无缝集成不同材料(如Si、SiGe、GaN)、不同供应商甚至不同化合物技术的裸片,无需额外植球等准备步骤。

这一特性通过多项目晶圆(MPW)加工得到了验证。

例如,采用250nm/130nm SiGe BiCMOS工艺制作的60GHz低噪声放大器(LNA)、120GHz收发器、50GHz IF-IF转换器等多种射频IC,可集成于同一封装中,采用低温固化(<250℃)、低介电常数/损耗的介质层材料,配合三层介质、两层金属的RDL结构,最终电性能测试证实了其在异构射频集成中的适用性。

材料与设备创新

低温固化材料:采用介电常数低、损耗小的介质层,固化温度低于250℃,适配环氧树脂塑封料(EMC),玻璃化转变温度低于200℃。

玻璃基板:中科院等机构研发玻璃通孔(TGV)技术,提升热稳定性与集成度,台积电、三星等均布局玻璃基板封装,以替代传统硅中介层,降低翘曲率并提升良率。

最新产业动态与技术突破

台积电:计划2027年将FOPLP+TGV(玻璃通孔)技术导入量产,采用玻璃基面板级封装以提升面积利用率并降低成本。2026年将设立扇出型面板级封装实验线,初期使用300×300mm面板,逐步过渡到更大尺寸。

三星:已将FOPLP技术用于移动或可穿戴设备(如Galaxy Watch),并开发出高达800×600mm的面板。其“3.3D”封装技术结合RDL与3D堆叠,目标2026年量产,旨在连接逻辑芯片与高带宽存储器(HBM)。

日月光:FOPLP技术已量产,主要应用于射频、电源管理等领域。2025年AI先进封装需求强劲,将增加资本支出布局先进封装及智能生产。

群创光电:利用旧3.5代厂转型为全球最大尺寸FOPLP厂,2024年下半年试产,2025年逐步量产,月产能目标达3000~4500片,客户涵盖恩智浦、意法半导体等车用与电源管理领域厂商。

板级封装的经济效益分析

板级封装的经济效益分析需基于多层次、高颗粒度的自下而上成本模型,该模型通过详细拆解工艺步骤(如组装、模塑、RDL制备、UBM/球贴装)及设备参数(投资、占地面积、处理时间、功耗),结合材料类型与用量、基建成本(电力、洁净室、租金)等要素,实现对不同技术选择(芯片先置/后置、光刻技术)、产品场景(裸片数量、封装尺寸、RDL层数)及商业需求(生产地点、产量、交期)的差异化成本评估。

以面朝下模塑优先工艺为例,其成本构成涵盖三层光敏介质RDL、镍-金UBM及SnAgCu球的制备流程,核心挑战集中于组装精度与速度、模塑翘曲控制、RDL线宽/线距(L/S)优化等模块,而测试环节未纳入模型。

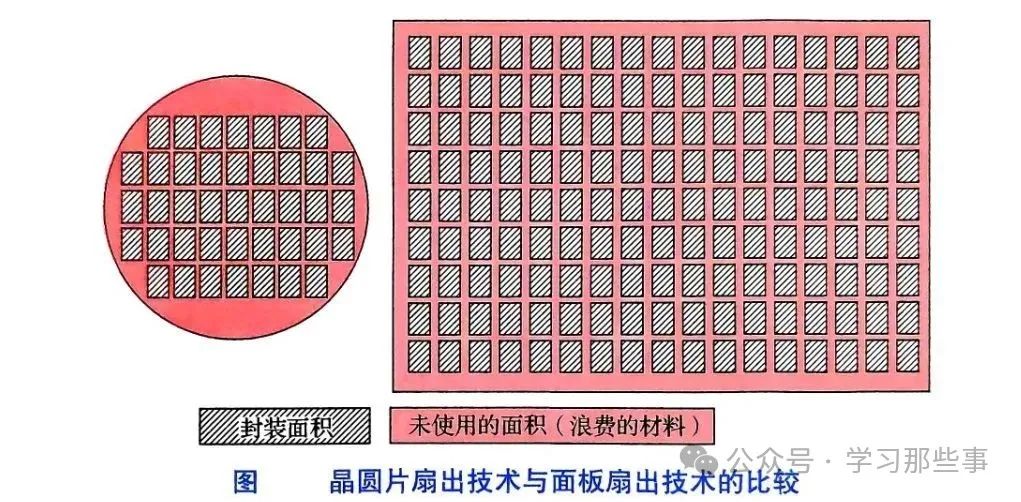

关键经济优势体现在材料利用率与面积效率的提升:

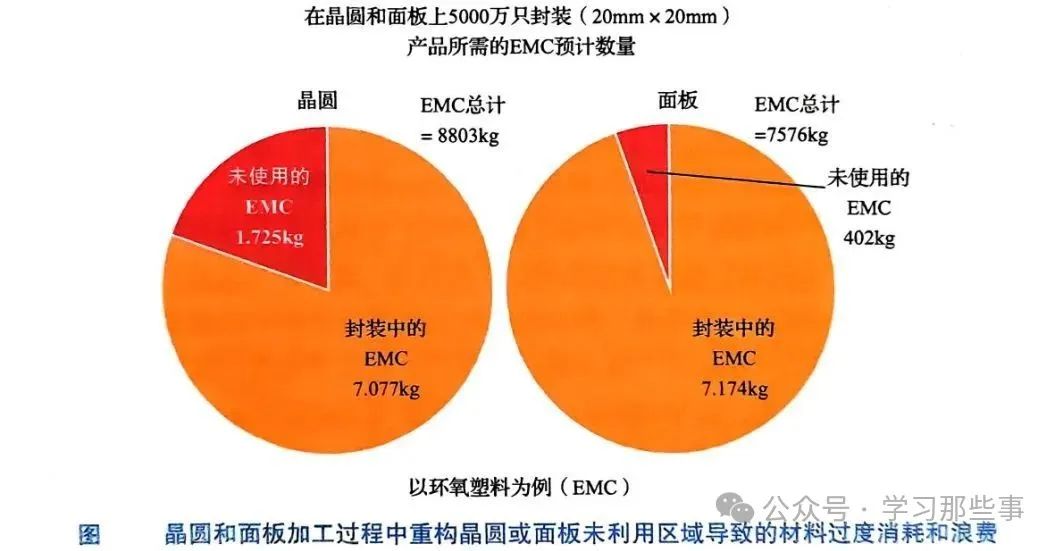

相较于300mm晶圆,457mm×610mm矩形面板在封装尺寸较大时(如≥11mm×11mm)可实现更高的面积利用率(AU≥90%),而晶圆AU仅85%~88%且仅适用于小封装。AU的提升直接减少基板非封装区域的材料浪费——以生产5000万只20mm×20mm封装为例,面板方案较晶圆方案减少14%的环氧树脂塑封料(EMC)消耗(402kg vs 1725kg),显著降低材料成本(EMC为FO-PLP流程中最贵材料之一)。

此外,矩形面板的灵活性允许封装水平或垂直放置,适配更多长宽比组合,进一步优化AU。

生产效率方面,面板方案通过提升组装设备单位/小时(UPH)性能可降低组装成本,且随着面板尺寸增大(如610mm×457mm),单位基板面积的相对成本因组装密度提升而下降,尤其对多芯片模块(如三芯片)的成本改善更为显著。对比300mm晶圆的单芯片封装,大面板方案在保持芯片数量不变时,相对成本始终更低,且面板尺寸扩大进一步降低重构区域的成本分摊。

综上,板级封装通过高AU、低材料浪费、适配多芯片/大尺寸封装的优势,结合自下而上的精细成本模型验证,展现出显著的经济效益,尤其在高端应用(如射频、汽车电子、AI加速器)中,其成本效率与环境友好性成为推动异构集成技术落地的重要支撑。

-

Chiplet与异构集成的先进基板技术2025-11-04 2389

-

先进封装技术-7扇出型板级封装(FOPLP)2024-12-06 5582

-

异构集成封装类型详解2024-11-05 2806

-

日月光应邀出席SEMICON China异构集成(先进封装)国际会议2024-03-27 1213

-

一文解析异构集成技术中的封装天线2024-02-29 3002

-

异构集成 (HI) 与系统级芯片 (SoC) 有何区别?2023-11-29 4818

-

异构集成时代半导体封装技术的价值2023-11-28 1237

-

什么是异构集成?什么是异构计算?异构集成、异构计算的关系?2023-11-27 12484

-

异构集成推动面板制程设备(驱动器)的改变2023-04-11 1122

-

行业资讯 I 异构集成 (HI) 与系统级芯片 (SoC) 有何区别?2023-01-05 3341

-

英特尔异构3D系统级封装集成2021-03-22 3260

-

异构集成的三个层次解析2020-07-07 3113

-

PCB封装详解手册2012-03-18 17760

-

集成电路芯片封装技术知识详解2008-05-12 2600

全部0条评论

快来发表一下你的评论吧 !