vivado调用IP核详细介绍

描述

大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。

首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

使用Verilog调用IP核

这里简单举一个乘法器的IP核使用实例,使用Verilog调用。首先新建工程,新建demo.v顶层模块。

一、添加IP核

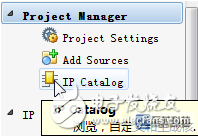

1. 点击Flow Navigator中的IP Catalog。

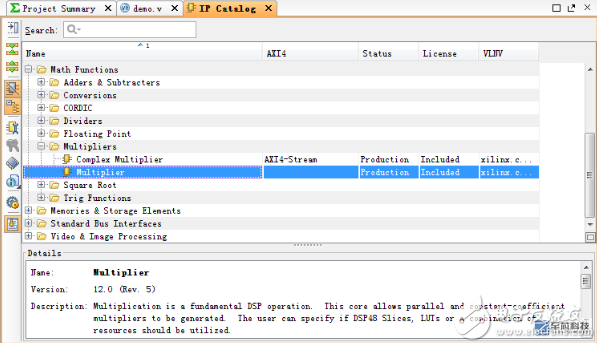

2. 选择Math Functions下的Multiplier,即乘法器,并双击。

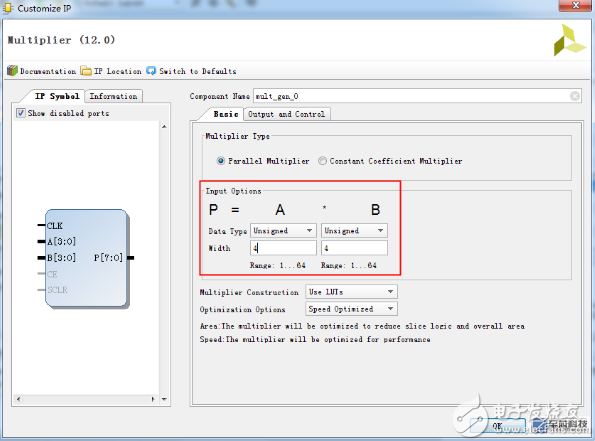

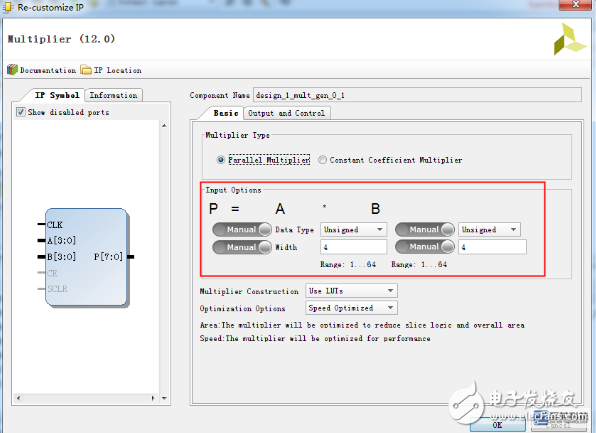

3. 将弹出IP核的参数设置对话框。点击左上角的Documentation,可以打开这个IP核的使用手册查阅。这里直接设置输入信号A和B均为4位无符号型数据,其他均为默认值,点击OK。

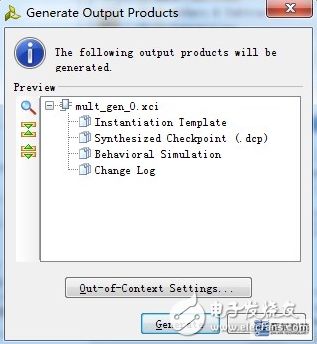

4. 稍后弹出的窗口,点击Generate。

二、调用IP核

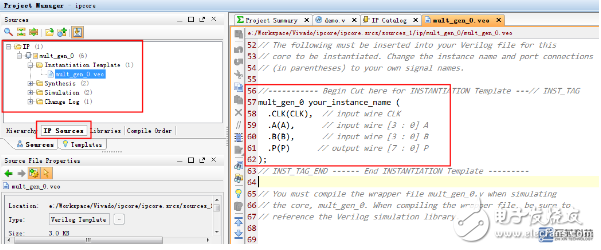

1. 选择IP Sources,展开并选择mult_gen_0 - Instantiation Template - mult_gen_0.veo,可以打开实例化模板文件。如图,这段代码就是使用Verilog调用这个IP核的示例代码。

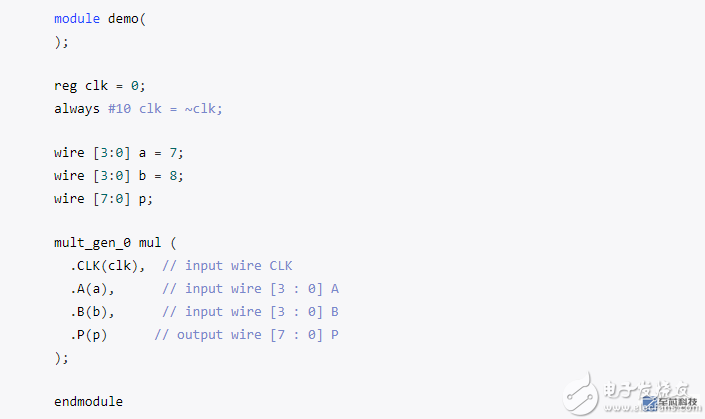

2. 将示例代码复制到demo.v文件中,并进行修改,最终如下。代码中声明了无符号型的4位变量a和b,分别赋初值7、8,作为乘数使用;无符号型的8位变量p,用于保存计算结果。clk为Testbench编写的周期20ns的时钟信号;mult_gen_0 mul(...)语句实例化了mult_gen_0类型的模块对象mul,并将clk、a、b、p作为参数传入。

三、行为仿真验证

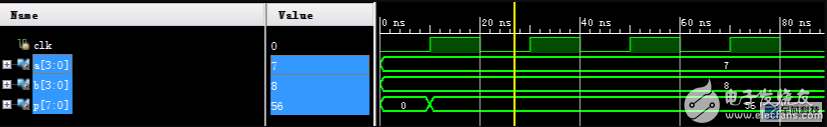

以demo为顶层模块,启动行为仿真,即可输出波形。设置a、b、p显示为无符号十进制(右击选择Radix - Unsigned Decimal)。如图,可以看到a=7, b=8,第一个时钟上升沿后p = a * b = 56。

框图(Block Design)中调用IP核

这里举一个简单的例子,通过调用乘法器IP核,产生一个能计算平方的新模块。

一、创建框图设计文件

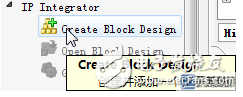

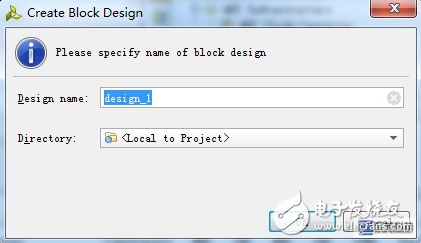

1. 选择Flow Navigator中的Create Block Design,创建一个框图设计文件。

2. 输入文件名并点击OK。

二、添加IP核

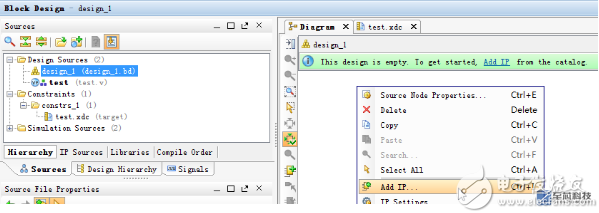

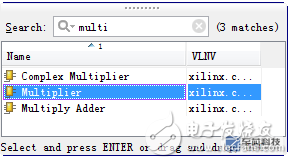

1. 在框图空白处右击,选择Add IP。

2. 可以直接搜索需要的IP核,双击确认。

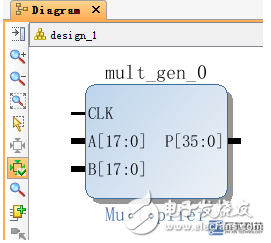

3. IP核即可被添加进来,可以用导线将其与其他器件连接。

4. 双击这个IP核符号,可以打开参数设置对话框。点击左上方的Documentation可以查看IP核的手册。这里将输入的A、B均设置为4为无符号型,其他为默认值,点击OK确认。

三、绘制电路

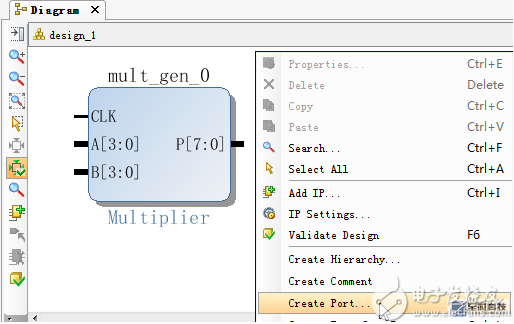

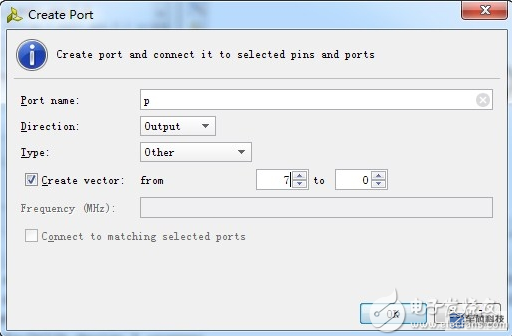

1. 右击Diagram窗口空白处,选择Create Port。

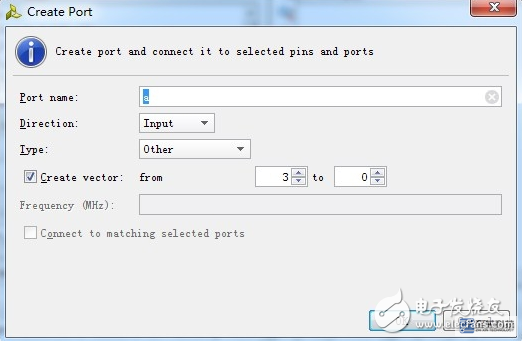

2. 弹出窗口中,设置端口a为4位输入信号,并点击OK。

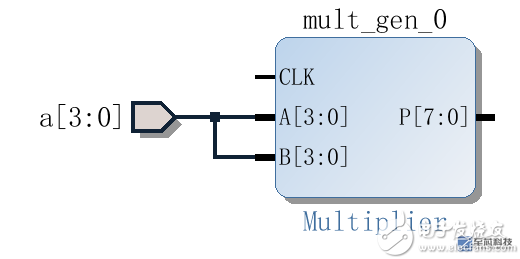

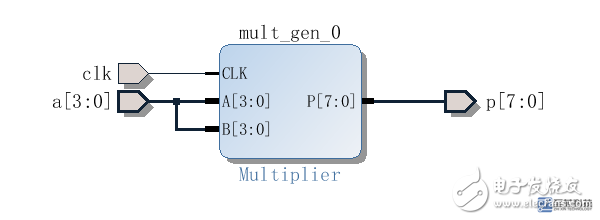

3. 将a与A、B都连接起来。

4. 同样的方法,添加一个8位输出端口p,与P连接。

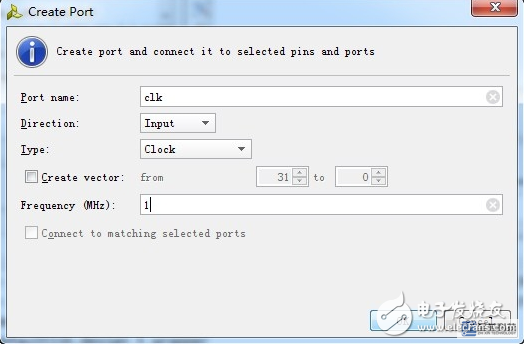

5. 再添加一个clk时钟输入端口,与CLK连接。

6. 最终结果如图。

四、仿真测试

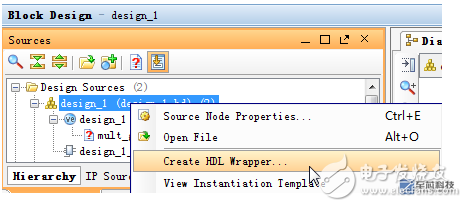

1. 右击框图设计文件design_1,选择Create HDL Wrapper。

2. 选择第二项并点击OK。

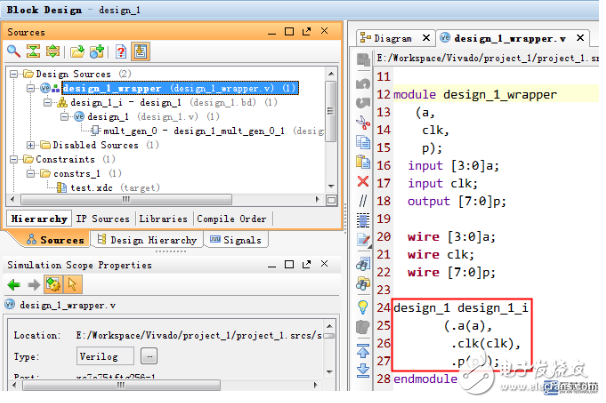

3. 打开生成的design_1_wrapper.v文件如图,红框中的代码用来调用前面画好的Block Design模块。

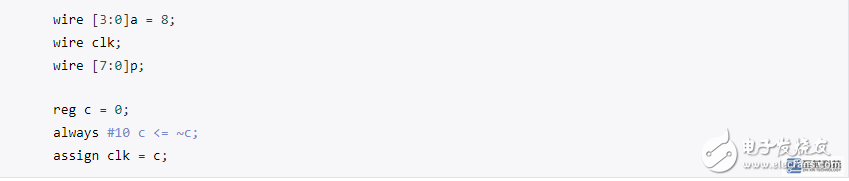

4. 在design_1_wrapper.v文件中,添加Testbench代码即可进行行为仿真。修改代码如下,给输入信号a赋初值为8,clk连接到Testbench生成的时钟信号c上。

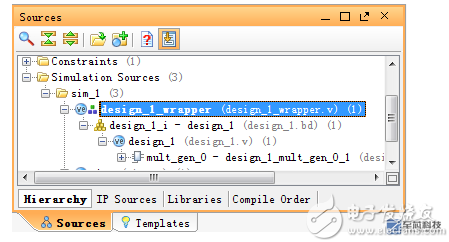

5. 在Simulation Sources文件夹下,设置design_1_wrapper.v为行为仿真的顶层文件(右击,选择Set as Top)。

5. 在Simulation Sources文件夹下,设置design_1_wrapper.v为行为仿真的顶层文件(右击,选择Set as Top)。

启动行为仿真,最终输出的波形如下。可以看到,在clk的第一个上升沿后,就有 p = a*a = 64,即实现了平方运算。

-

Vivado中FFT IP核的使用教程2024-11-06 5562

-

VCS独立仿真Vivado IP核的问题补充2023-06-06 2859

-

Vivado生成IP核2023-04-24 3411

-

FPGA应用之vivado三种常用IP核的调用2023-02-02 4979

-

vivado有哪几种常用IP核?如何去调用它们2021-07-29 2779

-

关于Vivado三种常用IP核的调用详细解析2021-04-27 25631

-

使用Vivado调用ROM IP核2021-01-08 3680

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 13248

-

调用Vivado IP核的方法2018-12-22 5193

-

详细操作 vivado 调用IP核(附图)2018-05-16 13643

-

vivado 调用IP核 详细介绍2018-05-15 7914

-

了解Vivado中IP核的原理与应用2017-11-15 10564

-

vivado带ip核的工程封装2017-07-14 4378

-

Xilinx Vivado的使用详细介绍(3):使用IP核2017-02-08 3080

全部0条评论

快来发表一下你的评论吧 !