FPGA设计中的HLS 工具应用

可编程逻辑

描述

1 概述

在集成电路行业飞速发展的今天,缩短产品开发的周期而又不牺牲验证过程,这不可避免地成为了商业市场的一个关键因素。Xilinx Vivado High Level Synthesis (即Vivado HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

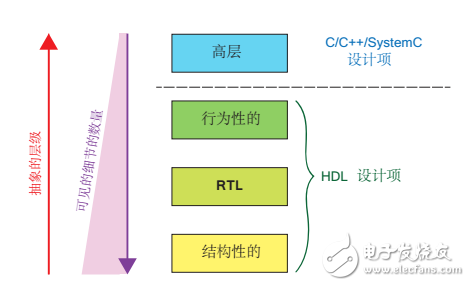

图 1 FPGA设计中的抽象层次

从图1 可知,抽象的层次越高可见的细节就越少,对于设计者来说设计起来越容易。

2 labs 1 vivado hls 生成RTL级文件

本次实验以fir(Finite Impulse Response)滤波器,有限长单位冲激响应滤波器为例。

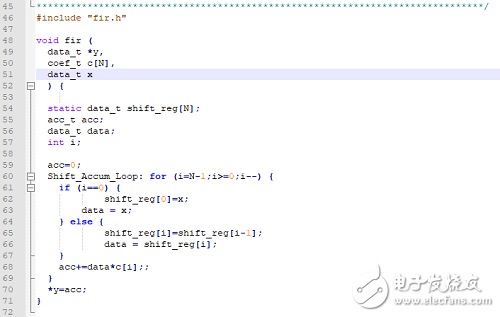

Fir.c源代码:

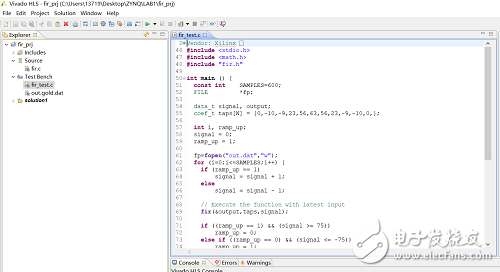

fir_test.c源码:

******************************************************************************/

#include

#include

#include "fir.h"

int main () {

const int SAMPLES=600;

FILE *fp;

data_t signal, output;

coef_t taps[N] = {0,-10,-9,23,56,63,56,23,-9,-10,0,};

int i, ramp_up;

signal = 0;

ramp_up = 1;

fp=fopen("out.dat","w");

for (i=0;i<=SAMPLES;i++) {

if (ramp_up == 1)

signal = signal + 1;

else

signal = signal - 1;

// Execute the function with latest input

fir(&output,taps,signal);

if ((ramp_up == 1) && (signal >= 75))

ramp_up = 0;

else if ((ramp_up == 0) && (signal <= -75))

ramp_up = 1;

// Save the results.

fprintf(fp,"%i %d %d\n",i,signal,output);

}

fclose(fp);

printf ("Comparing against output data \n");

if (system("diff -w out.dat out.gold.dat")) {

fprintf(stdout, "*******************************************\n");

fprintf(stdout, "FAIL: Output DOES NOT match the golden output\n");

fprintf(stdout, "*******************************************\n");

return 1;

} else {

fprintf(stdout, "*******************************************\n");

fprintf(stdout, "PASS: The output matches the golden output!\n");

fprintf(stdout, "*******************************************\n");

return 0;

}

}

本次实验将通过vivado hls将fir.c生成verilog代码,实现c到verilog的转换,展示了如何创建一个高层次的合成项目,验证C代码,合成对RTL进行设计,并对RTL进行验证。

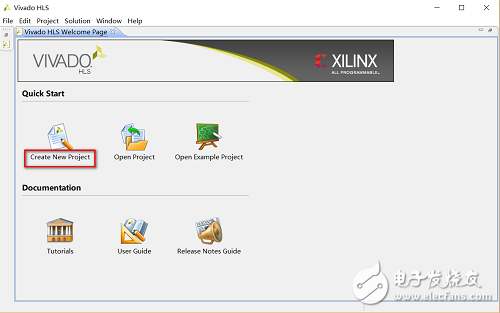

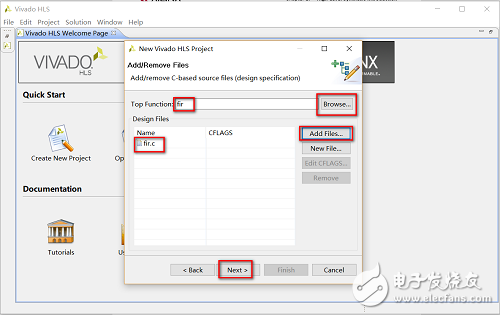

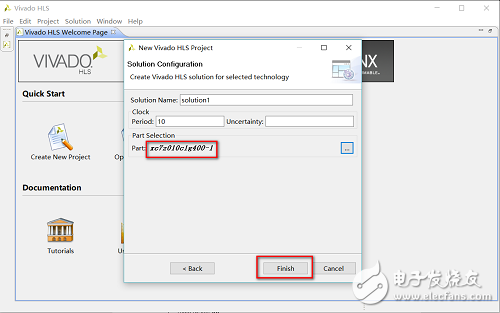

第一步:创建工程

打开Vivado hls点击创建新工程

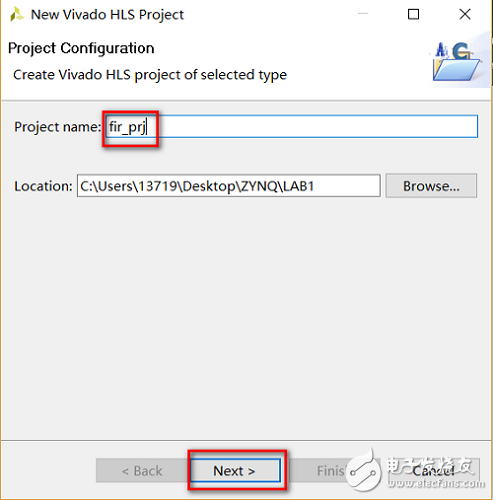

工程名字:fir_prj下一步

点击浏览,添加fir.c文件下一步

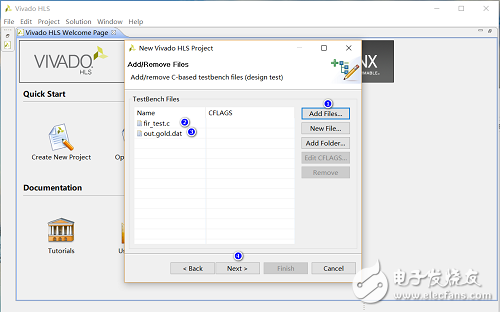

添加fir_test.c文件以及out.gold.dat文件下一步

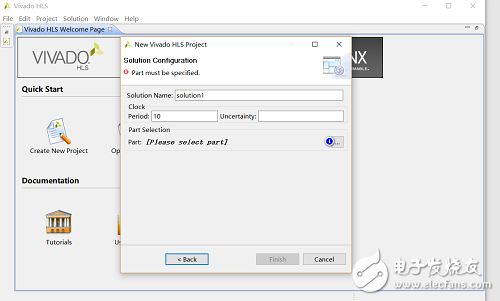

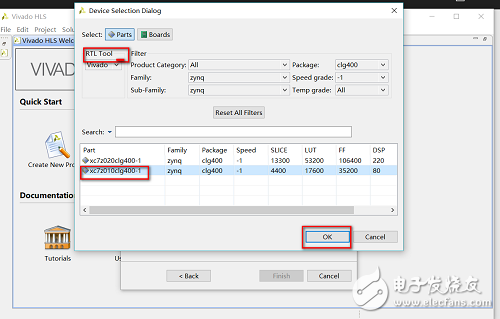

Part选择自己开发板对应的器件。

点击ok

点击finish

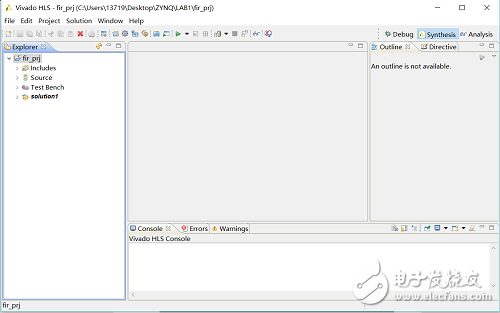

工程创建完成。Source 包括我们的设计源文件,Test Bench是我们的仿真文件。

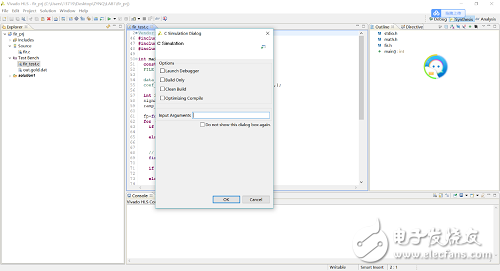

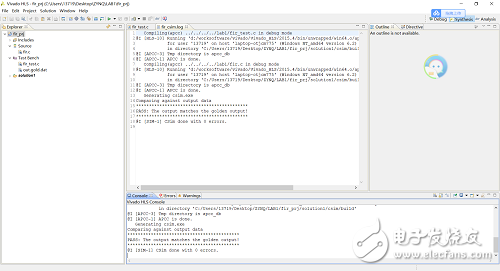

第二步:验证C源代码

点击project>run c simulation 点击ok

C代码仿真完成 0 errors

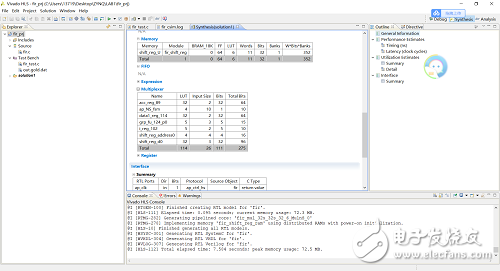

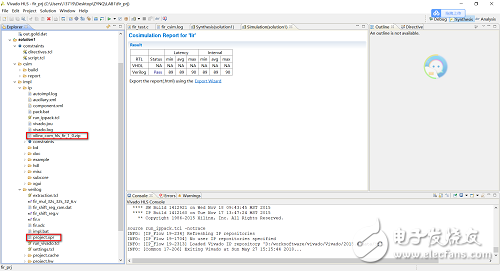

第三步:高级综合

点击solution > run c synthesis>active solution

综合完成。

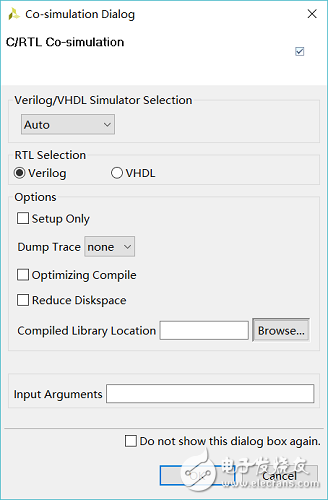

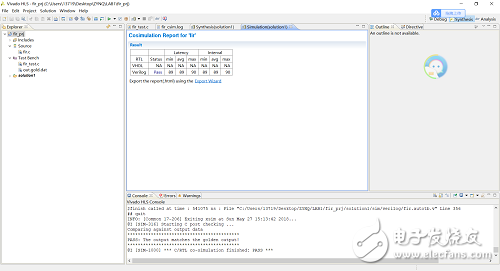

第四步:RTL验证点击solution>run c/rtl cosimulation ok

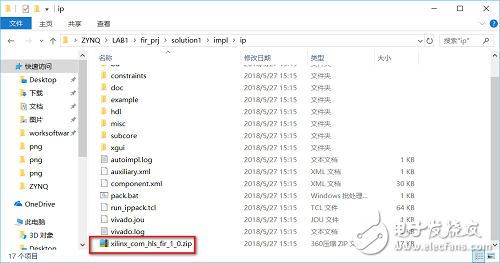

第五步:IP创建

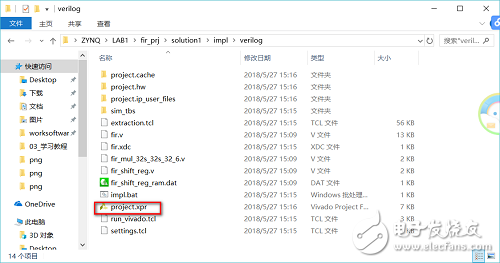

Verilog代码以及ip已经生成。

Fir滤波器工程也已经生成。

至此vivado hls的基本使用,以及fir滤波器从c代码已经完全转化为verilog和vhdl的代码以及ip。下节将演示如何使用vivado添加fir滤波器ip。

-

优化 FPGA HLS 设计2024-08-16 1114

-

合成中的Vivado HLS中的Pragma错误怎么解决2020-05-21 2939

-

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南2020-10-10 2544

-

HLS高阶综合的定义与解决办法2021-07-10 4087

-

FPGA高层次综合HLS之Vitis HLS知识库简析2022-09-07 3856

-

使用Vitis HLS创建属于自己的IP相关资料分享2022-09-09 5561

-

使用Vivado高层次综合 (HLS)进行FPGA设计的简介2016-01-06 1458

-

极客对Xilinx Vivado HLS工具使用经验和心得2019-07-30 5669

-

XIlinx利用HLS进行加速设计进度2019-07-31 7653

-

Vitis HLS工具简介及设计流程2022-05-25 3747

-

使用网络实例比较FPGA RTL与HLS C/C++的区别2022-08-02 2378

-

ThunderGP:基于HLS的FPGA图形处理框架2022-10-27 902

-

FPGA基础之HLS2022-12-02 7737

-

FPGA——HLS简介2023-01-15 6826

-

HLS设计中的BRAM使用优势2026-01-28 411

全部0条评论

快来发表一下你的评论吧 !