栅极驱动器环路设计对SiC MOSFET开关性能的影响

描述

*本论文摘要由PCIM官方授权发布

内容摘要

每个功率开关都需要一个驱动电路,这是必要的,但容易被忽视。栅极驱动电路对功率器件的开关过程有着非常重要的影响,本文分析了驱动电路的输出能力和杂散参数这两个参数。本文以 SiC MOSFET关断过程为基础,分析了与驱动电路输出能力和杂散参数相关的影响因素,并通过理论分析和仿真结果进行验证。此外,还列出了栅极驱动器回路设计技巧,以提供一些建议。

引言

如今,随着能源结构的发展,电动汽车和可再生能源以其高效率、低污染的特点越来越受到人们的青睐[1]。在这些应用中,功率开关是最重要的组件之一,功率开关的性能将决定整个系统的性能。

栅极驱动器电路是每个功率开关所必需的,栅极驱动器的能力和性能对功率器件的性能,尤其是开关性能非常重要。

SiC MOSFET具有开关速度快、击穿电压高、开关损耗低和导热性好等优点,被广泛应用于电动汽车和可再生能源领域[2]。然而,由于开关速度较快,较高的dv/dt和di/dt会对栅极驱动回路和功率回路杂散参数造成较严重的影响,包括击穿、振荡、超标等[3-4]。

栅极驱动器要实现更好的性能,有两个要点。一个是输出能力,另一个是杂散参数。本文首先介绍功率器件的基本开关过程,然后分析对于输出能力和杂散参数的影响因素。

开关过程

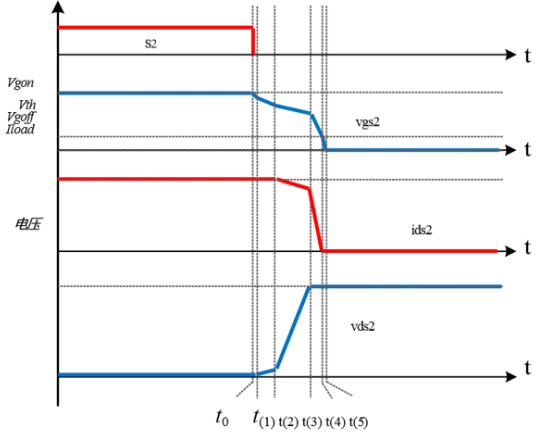

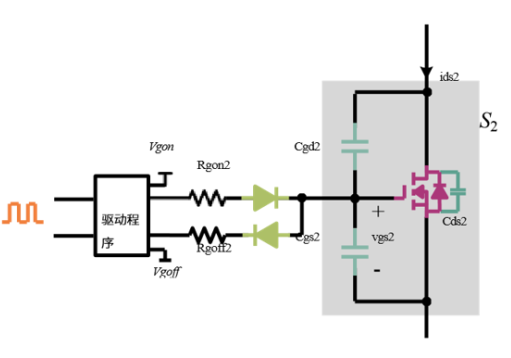

图1.a显示了图1.b中S2的关断过程。

在t0-t1时,栅极充电速度会影响驱动器延迟时间,但不会影响开关性能。

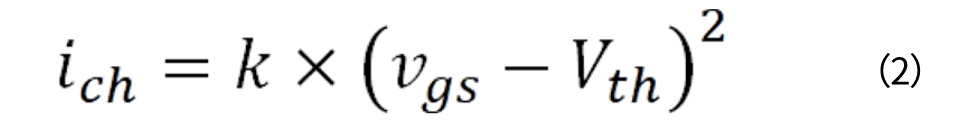

在t1-t2阶段,开关工作在线性区,vgs与vds和ids有关。这一过程可表示为方程(1)。这里的k与器件结构和材料有关。

(a)

(b)

图1.S2的关断过程

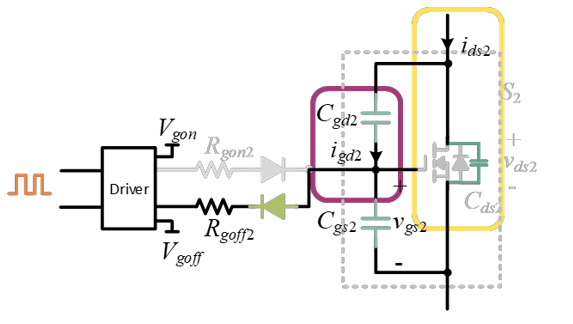

在t2-t3阶段,开关工作在饱和区,vgs与ids的关系如式(2)所示。然而,如图2所示,这一时期的vds受到两个环路的限制,一个是栅极驱动器环路,另一个是功率环路。更多细节将在论文全文中给出。

图2.t2-t3期间vds的双环限制

在t3-t4阶段,vgs和ids下降,开关管通道仍然导通,vds在此阶段没有变化。t4-t5期间,vgs下降,开关管通道不再导通。

输出能力

栅极驱动器的输出能力需要在设计过程中进行检查,但这一点很容易被忽视,尤其是在参考原有的设计进行新系统的更新设计时。

本节将介绍影响驱动输出能力的因素以及输出能力对开关过程的影响。

影响输出能力的因素

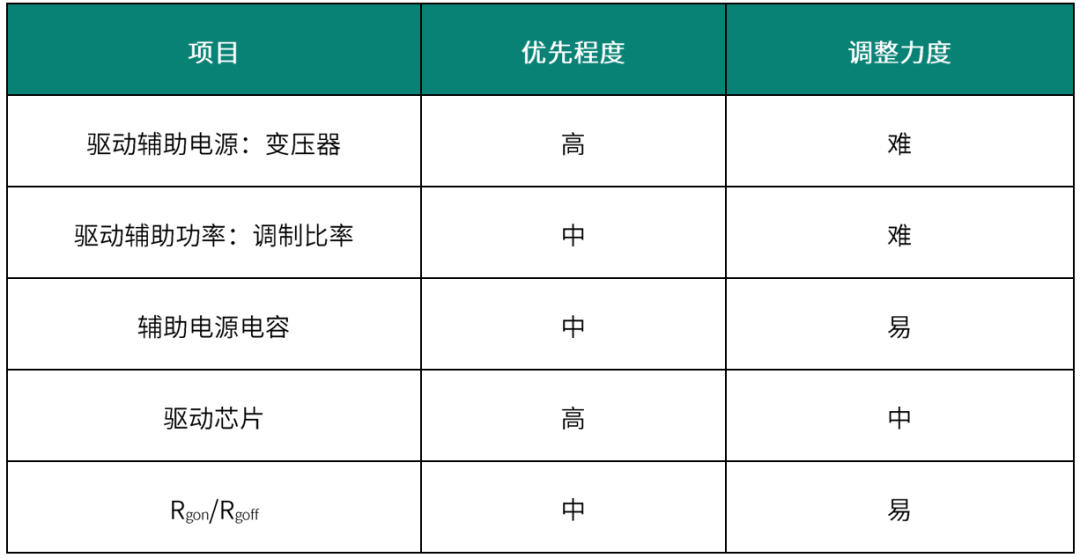

表1列出了与驱动输出能力有关的因素,详细情况和数学分析将在论文全文中列出。

表1.影响输出能力的因素

输出能力的影响

这部分将使用SPICE模型和Simetrix的仿真结果,以说明驱动输出能力的影响。

栅极驱动器杂散参数

栅极驱动器杂散参数会影响栅极电压和栅极电流波形,可能导致意外的开关动作。

影响杂散参数的因素

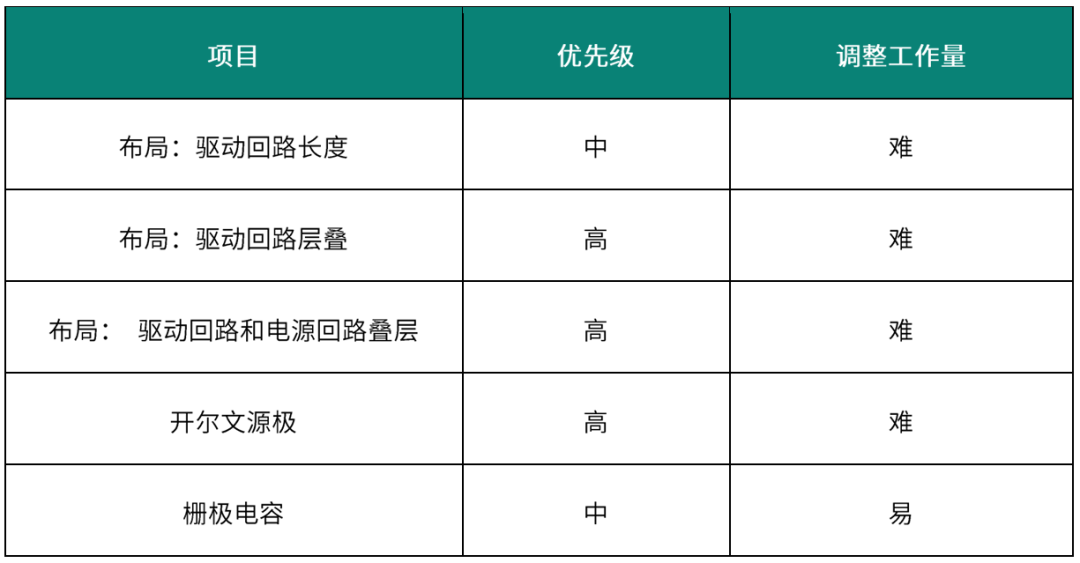

表2列出了与杂散参数有关的因素,详细内容和数学分析将在论文全文中列出。

表2.影响杂散参数的因素

杂散参数的影响

我们将展示使用SPICE模型和Simetrix的仿真结果,以说明驱动回路杂散参数的影响。

栅极驱动器电路设计

为了实现更理想的开关行为,在设计过程中需要检查一些工作。除此以外,还可以依据一些设计技巧,以轻松实现调整目标。

1. 在栅极上添加齐纳二极管。

2. 栅极和源极之间并联电阻。

3. 栅极和源极之间并联电容。

4. 辅助电源Vcc的并联电容。

5. 源极回路中增加电阻或磁珠

更多信息将在论文全文中提供。

结论

本文以SiC MOSFET为例,分析了栅极驱动回路设计的关键痛点。通过数学公式和仿真结果,给出了对于驱动输出能力和杂散参数的影响因素,并说明了这两个痛点的影响。最后,给出了栅极驱动电路的设计技巧,以便在设计过程结束后仍能轻松调整,从而有助于在系统层面取得更好的调试结果。

参考文献

[1] A.Kumar 和 L. B. Prasad,"电动汽车的问题、挑战和未来前景:2018 国际计算、电力和通信技术会议(GUCON),印度大诺伊达,2018 年,第 1060-1065 页。

[2] She X, Huang A Q, Lucia O, et al. Review of silicon carbide power devices and their applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10):8193-8205.

[3] Zhang Z, Wang F, Tolbert L M, et al. 有源栅极驱动器用于抑制相脚配置中的碳化硅器件串扰[J]. IEEE Transactions on Power

Electronics, 2013, 29(4):1986-1997.

[4] Ando M, Wada K. 基于电力电子电路缩放方法的可接受杂散电感设计[J]. IEEE Journal of Emerging and Selected Topics in

Power Electronics, 2016, 5(1):568-575.

-

UCC5880-Q1:汽车应用中高性能IGBT/SiC MOSFET栅极驱动器2026-01-07 418

-

AN-1535:ADuM4135栅极驱动器性能驱动SiC功率开关2025-01-15 372

-

Littelfuse发布IX4352NE低侧SiC MOSFET和IGBT栅极驱动器2024-05-23 1786

-

如何为SiC MOSFET选择合适的栅极驱动器2023-10-09 1766

-

面向SiC MOSFET的STGAP2SICSN隔离式单通道栅极驱动2023-09-05 846

-

SiC MOSFET栅极驱动电路的优化方案2023-08-03 2873

-

如何使用电流源极驱动器BM60059FV-C驱动SiC MOSFET和IGBT?2023-02-21 10171

-

驱动器和 SiC MOSFET 打开电源开关的大门2023-01-03 1623

-

用于SiC MOSFET的栅极驱动器2022-08-03 2879

-

ADI隔离栅极驱动器和WOLFSPEED SiC MOSFET2021-05-27 1468

-

SiC功率模块的栅极驱动其12018-11-30 3268

-

新型功率开关技术和隔离式栅极驱动器的趋势和格局2018-10-24 2235

-

汽车类双通道SiC MOSFET栅极驱动器包括BOM及层图2018-10-16 2891

全部0条评论

快来发表一下你的评论吧 !