「封装技术」PIC光子集成封装-从样机到量产

电子说

描述

翻译自Lee Carroll在2016年发表的文章

摘要

晶圆厂提供的光子集成电路PIC的多项目晶圆(MPW)服务,使得研究人员和中小型企业(SMEs)能够低成本完成硅光子芯片的设计和制造。尽管这些硅光芯片可以在探针台上测试,但如果不将它们封装起来,就无法开发成样机,无法在实验室外进行测试。PIC的光子封装比电子封装更具挑战性,成本高出几个数量级,因为它需要可靠的um级光学对准、精确的温度控制,且通常需要高度的垂直和水平电学集成。光子封装或许是开发具有商业价值的集成光子器件过程中最显著的瓶颈。本文阐述了如何满足硅PIC封装的光、电和热要求,以及在实现规模化量产之前还需要做的工作。

关键词:

光子封装;硅光子学;集成光学;光电子学;光子集成电路(PICs)

1. 引言

过去十年,硅光子学被视为在电信、数通、医疗技术、安全和传感等领域实现革命性进展的平台[1-3]。其背后的主要驱动力是,小型化高集成度的光子系统,这些子系统可以利用CMOS电子学的几十年丰富制造经验、技术和可扩展性[4]。最终目标是开发出具有集成电路EIC类似的低成本、高容量光子集成芯片(PICs),并充分利用硅平台的全部潜力—即硅光子用于高速信号传输和感知,CMOS电子用于后续的逻辑运算和计算[5]。

人们已经开发了系列硅光子元件,这些元件作为基础“构件”,在几家硅晶圆厂提供的MPW服务中使用[6-8]。这些元件包括一维(1D)和二维(2D)光栅耦合器、边耦合器、条形/脊形波导和交叉结构、多模干涉(MMI)分束器、阶梯光栅和阵列波导(AWG)复用器/解复用器、热可调谐微环谐振器、高速锗光电二极管、热光移相器、电吸收调制器(EAMs)等。从理论上讲,数千个这样的光子元件,或许还有几十个简单的硅光芯片(PIC)设计,可以布局在单个MPW“区块”(通常为10-30mm²)上,学术研究人员和中小型企业(SMEs)通常将其用作光子设计的测试平台。然而,开发创新的PIC并在实验室环境中(无论是在光学平台上还是在探针台上)展示其功能,只是迈向实用器件的第一步,这些器件需要能够吸引投资并在市场上产生关注度和价值。在将硅PIC产品化的过程中,相关的技术挑战往往被低估,甚至在硅PIC设计阶段被完全忽视,这导致第一代样机的性能显著下降,制造成本不必要地增加。

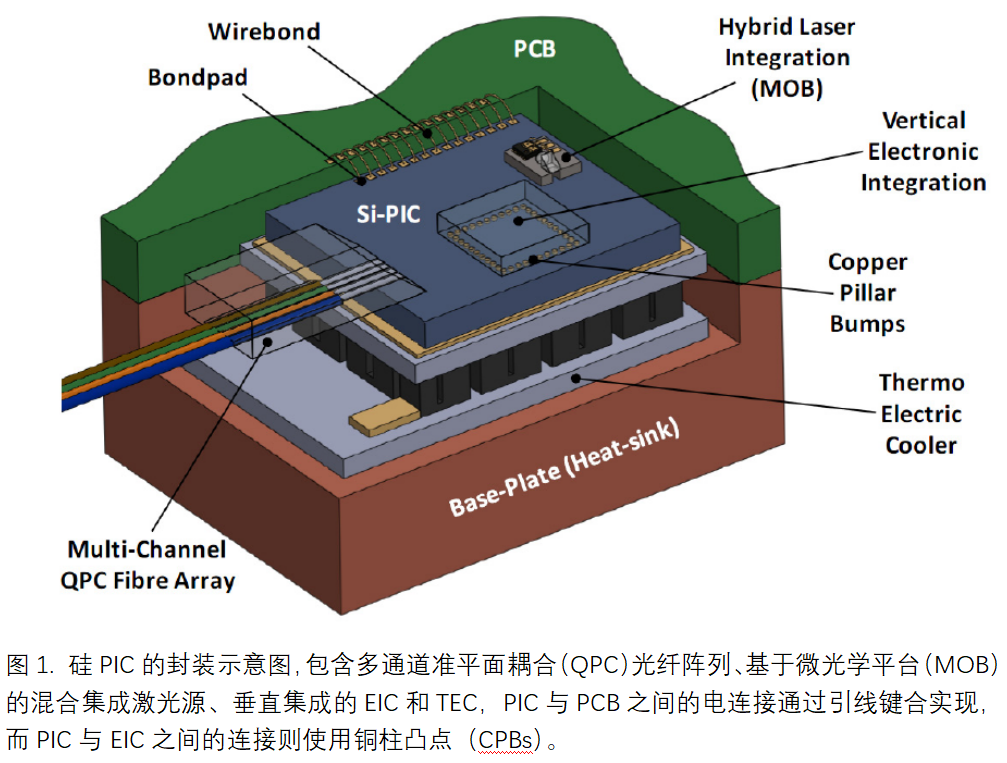

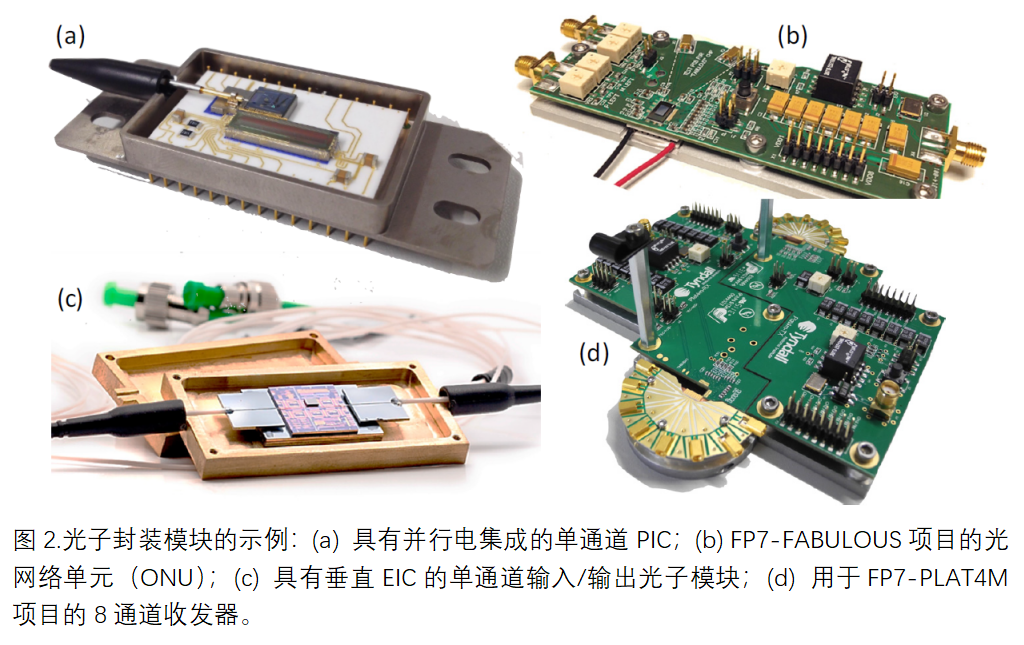

“光子封装”技术涵盖了多种技术和专业能力,这些技术和能力用于在PIC与外部建立光学、电学、热学、机械、甚至化学连接[9-12]。“光子封装“除了包括大家数值的光纤与PIC的耦合,还包括在PIC上集成激光芯片、微光学元件、电芯片和微流体器件;将高速25Gbps传输线通过阻抗匹配的方式从外部连接到PIC上;以及为保证PIC正常工作所需的高效热管理—见图1和图2。

虽然满足这些光子封装要求中的任何一项可能都不难,但要在一个独立可靠的器件中实现全部这些要求以进行现场样机测试却不容易,在更先进的光子器件中更是如此,这些器件需要同时采用多种不同的封装技术,例如多通道光纤与PIC耦合、垂直集成的驱动芯片、高速连接以及TEC[12]。为确保这些器件在制造和组装后能完全正常工作,需要在硅PIC设计阶段就采用封装设计规则(PDRs)。本文介绍光子封装中需考虑的各种光学、电学和热学因素,作为封装设计规则的“入门指南”,同时也介绍了一些有助于光子器件产业化的趋势。

2. 光学封装

硅作为间接带隙半导体,用于激光发射的直接带隙复合概率非常低。因此,所需的光信号必须来自外部激光源,要么间接(即从分立激光器件通过光纤耦合光),要么直接(即III-V族器件/材料与硅PIC的混合/异质集成)。激光与PIC的间接和直接耦合有许多方式,每种方式还可以根据所采用的耦合方案进一步细分,例如光栅耦合、边耦合、倏逝耦合等。光纤与PIC的间接耦合常用于电信和数通应用,因为它允许通过光纤网络传输信息,而集成光源直接耦合则用于安全和传感应用。

2.1. 光纤与PIC的耦合

单模光纤SMF与硅PIC上典型波导之间传输光的主要挑战在于两种材料系统的模场直径MFD存在巨大差异。在通信波长(1260-1650nm)下,光纤中的模场直径约为10μm且呈圆对称,而PIC中的模场直径通常呈椭圆形,尺寸为0.5×0.3μm[13]。因此,除了两种波导的模场尺寸存在一个数量级的差异外,如果单模光纤模式中电场的未知且不稳定方向与PIC波导的基偏振方向(电信和数通应用通常为TE横电,传感应用通常为TM横磁)不一致,还会带来偏振相关损耗PDL。因此,通常需要某种形式的“偏振管理”以确保光纤与PIC耦合——要么直接在耦合器元件本身(如二维光栅耦合器[14]),要么在PIC的后续阶段(如必要用于滤波和旋转偏振的波导元件[15])。如下面三个小节描述的,光纤与PIC的耦合主要有三种方法:边耦合、光栅耦合,以及最近出现的倏逝耦合,每种方法都有其自身的性能优势和局限性,适用于特定的应用。表1给出了这些不同耦合方法对比。

2.1.1. 边耦合

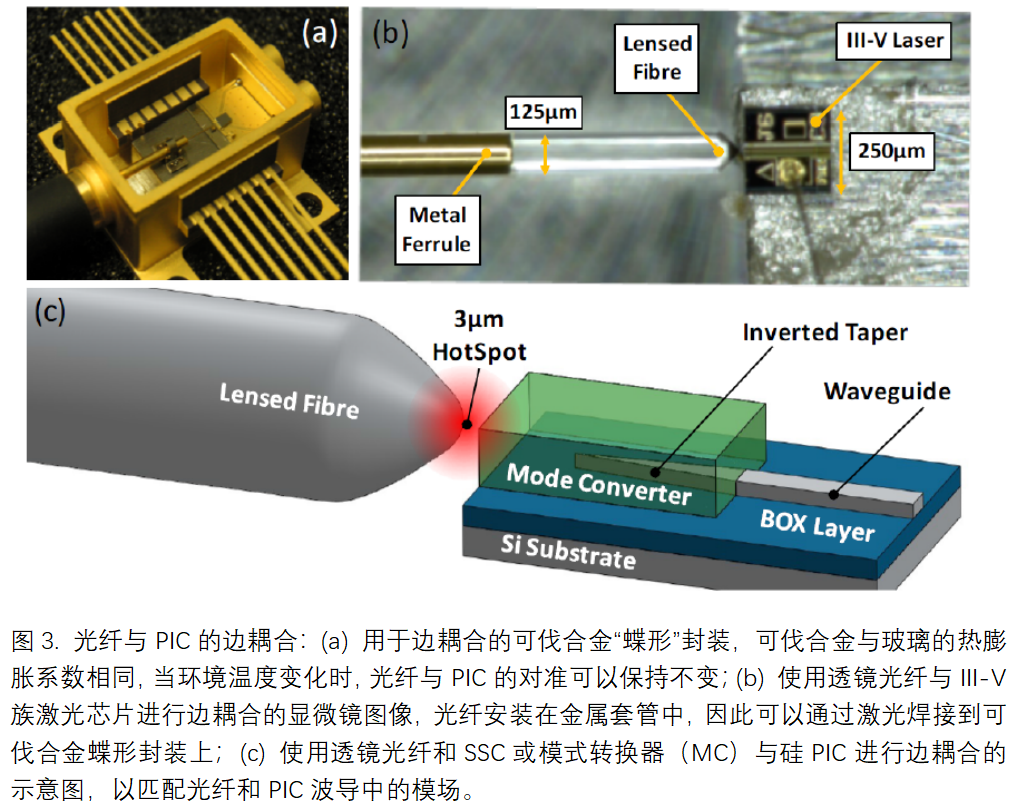

边耦合是激光芯片商业封装中一种成熟的方法[16],具有低耦合损耗(小于1dB)、宽光谱、偏振无关等优良特性 [17],但在硅光子学领域尚未被广泛采用。硅PIC的典型边耦合器由嵌入氮化物模场转换器SSC或后处理沉积的聚合物倒锥结构(长度为100-300μm)组成的SSC,以将PIC上波导模式的MFD增加到约3×3μm[18,19],这与透镜SMF-28光纤或超高数值孔径(UHNA)光纤形成良好的模场重叠,见图3。

由于需沉积和蚀刻3-5um SiON层来制作集成的模式适配器,很难成为标准构件(主要是因为SiON层给晶圆带来了高应变),因此晶圆厂将难以在MPW中引入模场转换。在Si-PIC上添加边耦合器也会增加制造后的处理成本,因为它需要对PIC边缘进行精确的切割和抛光,或者需深蚀刻(>60um)光刻以创建一个刻面和V槽(用于使用无源对准方式将光纤与PIC波导对准),这种方式的主要缺陷是V槽占用了Si-PIC上较大空间。

大多数情况下,边耦合在PIC和透镜光纤之间进行。光纤端面的透镜形成3μm直径的光“热点”,使光纤模式与PIC上的模场转换器的模场直径更好地匹配。这种边耦合器的1dB对准公差通常为亚微米级(约±500nm),因此需要有源对准以降低插入损耗[18,19]。鉴于此对准公差与多通道光纤阵列的制造公差相当,边耦合几乎总是仅用于单通道光纤与PIC的耦合。此外,通常需要将安装在金属套管中的透镜光纤和PIC激光焊接到可伐合金封装上,以确保热胀冷缩引起的位移不会影响光纤与PIC的耦合(可伐合金是一种铁-镍-钴合金,具有与光纤中的玻璃匹配的热膨胀系数),见图3。此外,这种金属间的键合比环氧树脂键合更不易因老化环境影响而发生微小的对准漂移[16]。显然,当前最先进的边耦合的对准公差和材料要求过高,难以可靠地满足中高产量(每年10⁶-10⁷个器件)的需求。

边耦合通常用于硅光子学中的非线性应用,这些应用通常需要较高的输出光功率(约1W)来完成四波混频和其他非线性相互作用。边耦合器的宽带特性意味着可以准确测量泵浦、信号和空闲通道的相对强度(因为所有三个波长都经历相同的插入损耗),从而可以精确计算非线性转换效率。为防止损坏模式适配器,带有边耦合器的非线性应用模块必须采用密封封装,否则,由透镜光纤聚焦的高光功率形成的“热点”的电场梯度可能会产生光镊效应,将空气中的微粒和有机污染物吸引到模式适配器的端面,如果这些污染物吸收了相当一部分光功率,可能会由于端面的局部加热而导致模式适配器的灾难性失效。这种失效在SU-8和PMMA模式适配器中更为常见,而在集成的SiON模式适配器中则较少见,因为介电材料比聚合物光刻胶更耐受热分解。

与光栅耦合器阵列相比,边耦合器阵列具有更低的插损和更宽带宽,许多研究小组和公司正在研究降低边耦合对准公差的方案[21,22],目的是放宽对准公差或提高制造公差[23],以满足电信和数通应用中的多通道边耦合需求。当前MPW光栅耦合器的损耗和带宽通常被公司和标准化机构视为光子器件商业应用的重大障碍。

2.1.2. 光栅耦合

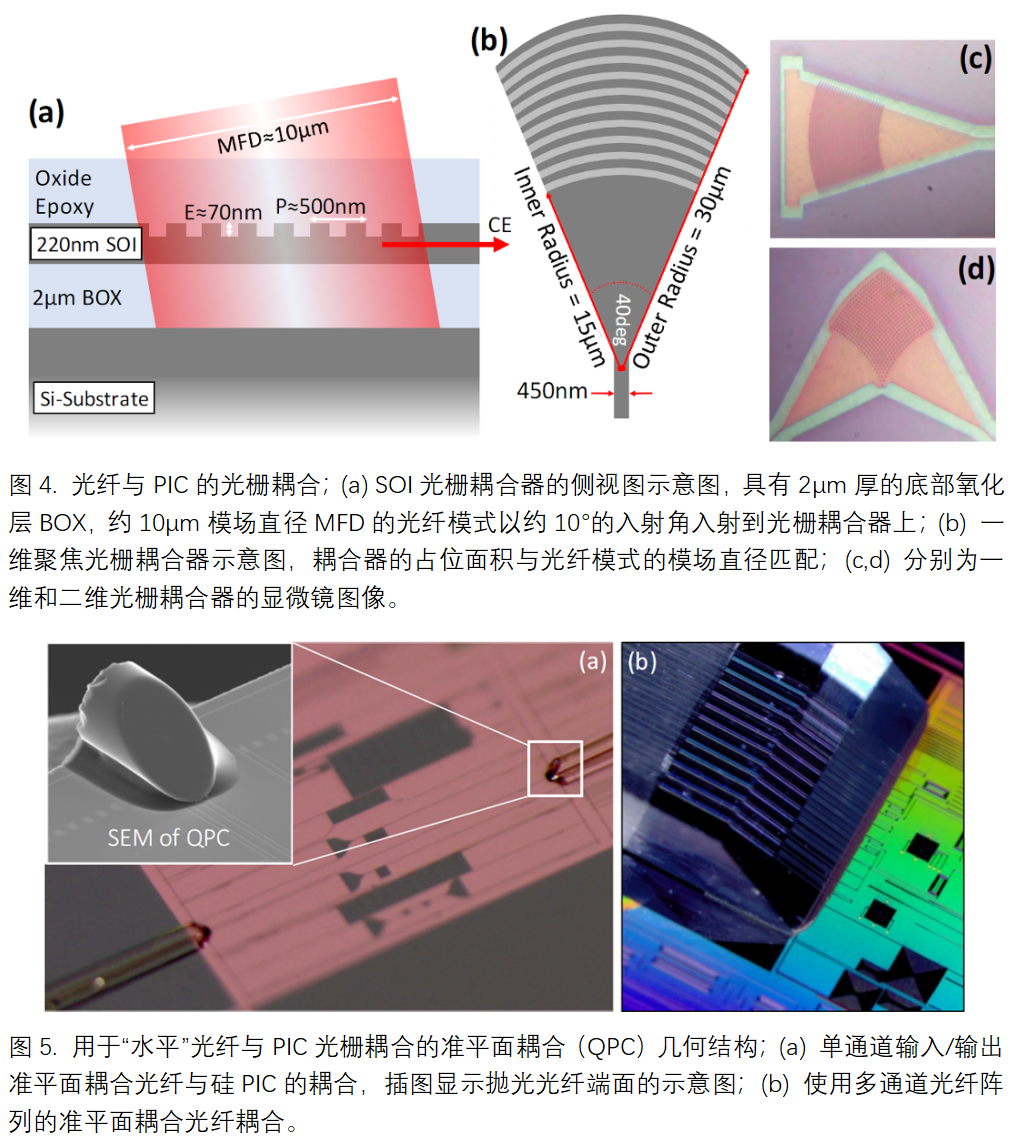

边耦合最常见的替代方案是光栅耦合,其在PIC的波导层中光刻蚀刻亚微米周期结构,以创建相干干涉条件,将光纤模式衍射耦合到PIC波导中[24,25],见图4。光栅耦合器大概102μm大小以在匹配标准电信光纤8-10μm的模场直径,由约20个部分蚀刻到220nm硅层中的周期性沟槽阵列组成[12]。耦合器的峰值波长λ、沟槽间距P、光栅耦合器区域的有效折射率nₑ、氧化层的折射率nₒ和光纤模式的入射角θ之间存在简单关系:λ=P(nₑ−nₒsinθ),其中nₑ的值由沟槽的蚀刻深度和占空比以及光纤模式的偏振决定。通常采用近法线入射角(θ≈10°),以向耦合模式提供方向性,并减少向光纤的背反射。然而,从封装的角度来看,近法线入射的光纤与PIC耦合可能会导致器件体积庞大且机械性能不佳。为解决这一问题,已开发出一种用于光纤与PIC耦合的“准平面”方法,其中光纤端面被抛光至约40°,以创建全内反射条件,将光纤模式以正确的10°角导向光栅耦合器[26,27],见图5。这种几何结构形成了几乎“二维”的封装,在其中更容易满足电信光纤的最小弯曲半径(≈5cm),同时保持合理的器件占位面积。

光栅耦合器比边耦合器具有更宽松的对准公差,面内±2.5μm错位通常产生1dB的代价[13]。光栅耦合器放置位置灵活,无需放置在芯片边缘,可以放置在PIC表面的任何位置,也不需要切割和抛光等后续工艺,使得硅PIC在封装前就可以进行晶圆级测试和表征。尽管有这些优点,但光栅耦合的插损要高于边耦合。好消息是,光栅耦合器设计的最新研究进展已经开始缩小这一性能差距,有报道称在SOI平台中,均匀和切趾光栅耦合器的插入损耗分别为1.6dB和1.2dB(测量)[28,29]。更先进但商业化较低的光栅耦合器设计(在后工艺步骤中添加金属背反射层)可实现0.6dB的插入损耗[30],这表明先进的光栅耦合器已与边耦合器具有相同水平的性能,并具有宽松的对准公差。

因为通信光的偏振未知且不稳定,而标准的“一维”光栅耦合器通常偏振相关,这使得它们不适合电信和数通连接。一种解决方案是二维光栅耦合器,它由两个正交的一维光栅耦合器叠加而成,可以接收任何偏振状态的光纤模式,并将其衍射到两个均为TE偏振的PIC上的波导中[31]。最近关于硅光子学二维光栅耦合器优化的工作预测,带背反射器和不带背反射器的设计的插入损耗分别为1.0dB和2.0dB,偏振相关损耗PDL低至0.3dB[32,33]。

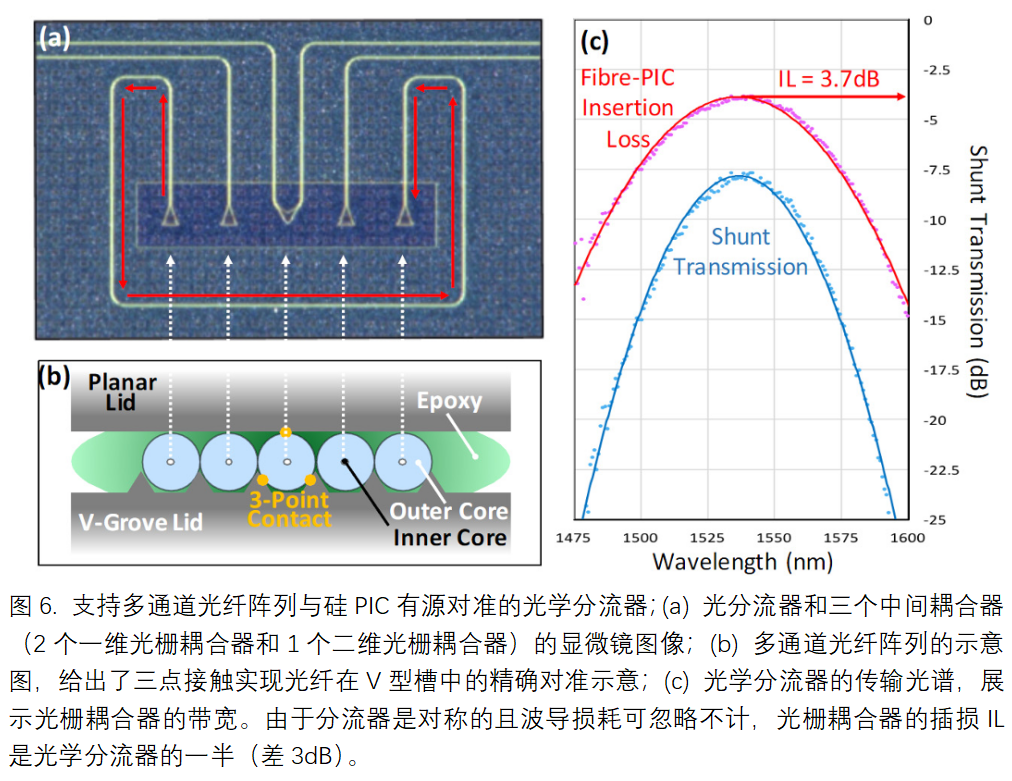

对于许多通信领域应用,通常需要将多个通道封装到同一个PIC上,目标甚至是128和256个通道。不必单通道对准,可使用“光分流器”来同时将每个光纤与匹配的光栅耦合器对准[34]。在这种方法中,需构建一个精密光纤阵列,它使用一块玻璃板,在玻璃板上精确蚀刻有一系列平行的V槽,间距通常为127μm或250μm,以对应标准电信光纤的直径,还有一个平的玻璃“盖子”,见图6。当光纤插入V型槽通道并盖上盖子后,三点接触条件确保了不同通道的精确位置和间距。这些光纤阵列中光纤内芯的标称中心度为±0.5μm,这完全在光栅耦合器±2.5μm的1dB对准公差范围内。因此,当第一个和最后一个光栅耦合器通过分流波导连接时,使分流传输最大化的光纤阵列单次有源对准也会将所有中间光纤通道相对于其光栅耦合器对准(公差为±0.5μm)。一旦完成单通道或多通道光纤与PIC的对准,就使用低收缩折射率匹配的紫外(UV)固化环氧树脂将其固定。

尽管分流对准有助于降低光纤与PIC封装的单通道封装成本,但需要采用一次有源对准步骤,而实现量产封装需要采用无源对准方案。最近有研究展示的“倒装芯片”光纤与PIC对准方法 [35],它使用分束器系统将光纤阵列中的内芯与PIC上的匹配光栅耦合器进行视觉对准,公差为±1μm,无需有源对准。由于这在光栅耦合器的1dB对准公差范围内,这种方法仍然具有低耦合损耗,但比有源对准至少快一个数量级。另一种无源对准方案使用大面积30μm×30μm光栅耦合器,其提供±10μm的1dB对准公差,目前也在研究中。它的主要缺点是光谱带宽减小,这导致其不适合波分复用应用。

2.1.3. 倏逝耦合

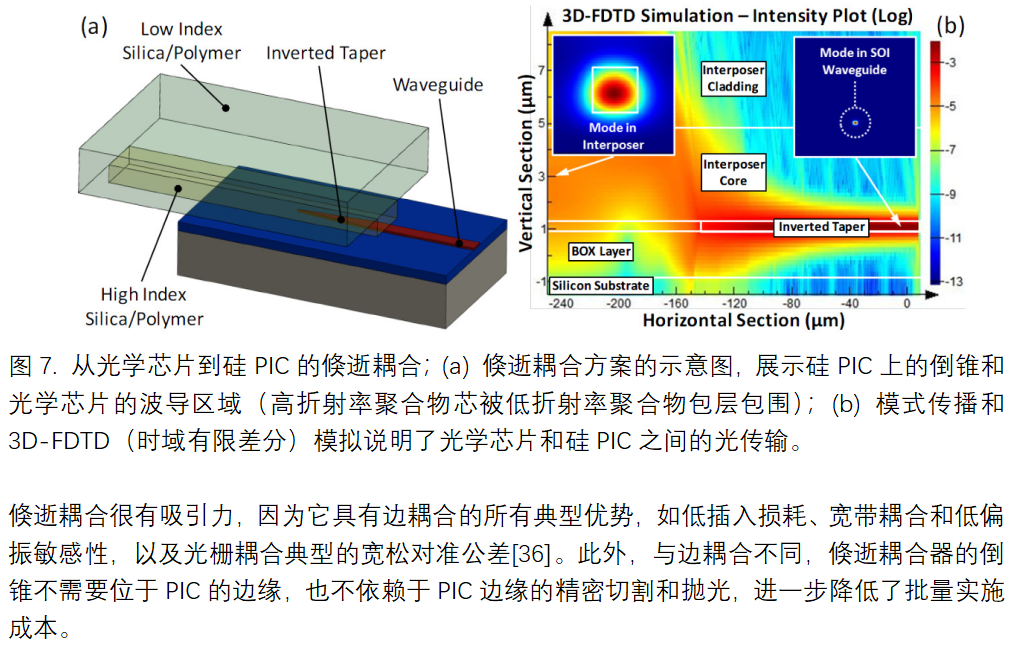

2015年,IBM-苏黎世首次将一种称为“倏逝耦合”的新方法应用于硅光子学 [36]。与边耦合类似,它使用倒锥从PIC波导中高效提取模式。然而,该模式不是被PIC上的模场转换器捕获,而是倏逝耦合到另一个光学芯片上的第二个波导中,该光学芯片与PIC面对面非常接近,见图7。然后,光芯片上的折射率和模场直径可以轻松匹配标准单模光纤,从而实现两步(光纤-芯片-PIC)耦合过程。目前,芯片与芯片的倏逝耦合仅在硅PIC和基于聚合物的光芯片之间得到证明,但没有明显的理由表明这种方法不能转移到基于玻璃或SiON的光芯片上,以用于更可靠的光子器件。

2.2. 激光与PIC的集成

对于光子学中的许多传感应用,希望在硅PIC上本地生成连续波或调制光信号。由于没有可与CMOS单片集成的激光二极管,这要么需要(i)III-V族材料与硅PIC的异质集成;要么需要(ii)III-V族器件与硅PIC的混合集成。

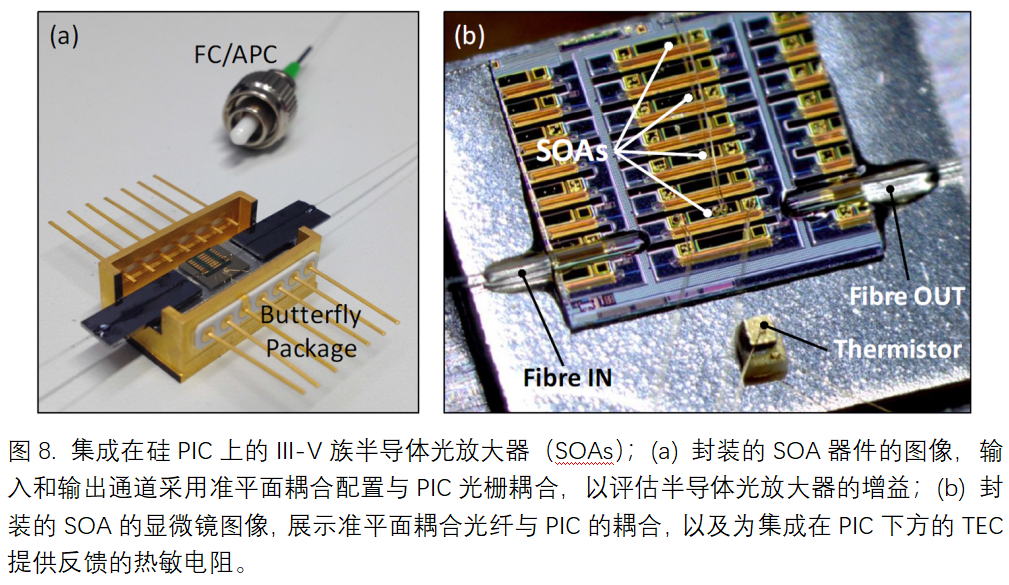

异质集成是将具有光学增益的III-V族材料键合到硅PIC上(直接键合或通过中间聚合物粘合剂层),然后蚀刻材料以创建激光腔条件。根据应用的不同,腔可以通过两个蚀刻端面、两个布拉格反射器,或者使用微环来形成[37,38]。产生的激光发射随后倏逝耦合到PIC上的波导中。异质集成可以被视为一种后处理步骤,而不是光子封装,通常用于制造半导体放大器(SOAs),其提供光增益以抵消硅PIC上的插损和波导损耗[39],见图8。这些集成的半导体光放大器的光增益具有强的热依赖性,需要温度稳定以实现稳定的性能。

混合集成涉及将光从分立的III-V族激光器件耦合到硅PIC上,要么直接耦合,要么通过微光机电(μOEM)平台。混合集成方案的集成密度往往低于异质集成方案,但具有使用“已知优良器件”的优势,具有更高的良率和更好的性能分布。两种很有前景的混合集成方案是微光学平台和直接VCSEL集成。

2.2.1. 微光学平台

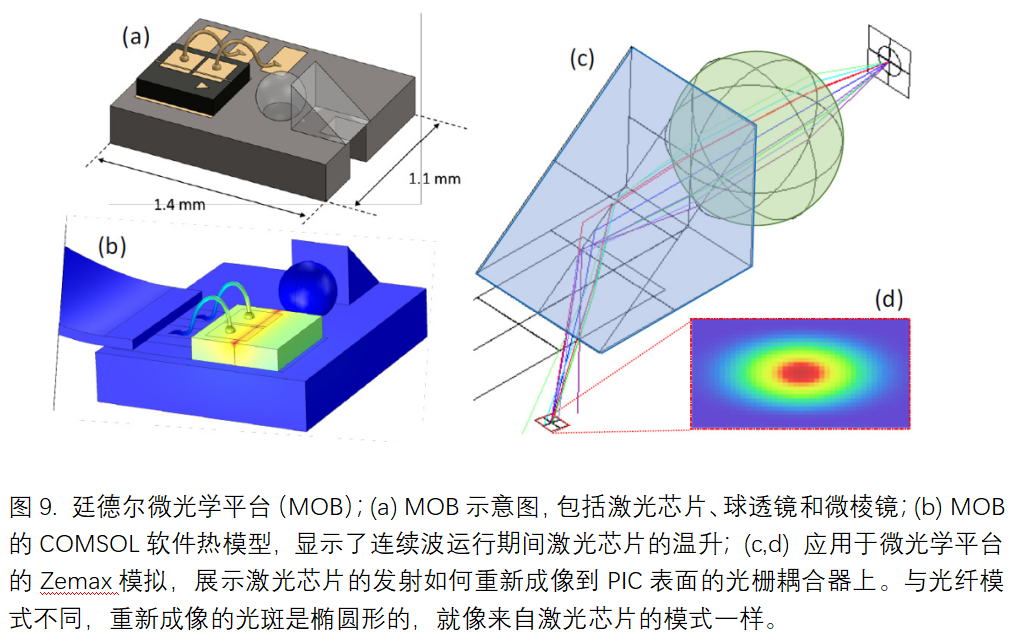

Luxtera和廷德尔国家研究所都展示了微光学平台(MOB)[40,41]。这些微光学平台由AlN或Si底座组成,其上安装有边发射激光芯片、用于准直和聚焦的球透镜以及用于光束转向的反射镜(或全内反射元件),见图9。密封的Luxtera微光学平台还包括一个微光学隔离器,以减少对激光芯片的反馈。微光学平台的功能是将来自边缘发射激光的光重新成像到PIC表面的光栅耦合器上,具有所需的近法线入射角。可以使用PIC上的标准一维光栅耦合器,但为更好地匹配来自微光学平台的椭圆光斑而设计的定制光栅耦合器具有更低的插损。

在廷德尔微光学平台中,300μm的球透镜在精密激光钻孔中自对准,然后为微棱镜反射元件的对准和安装提供固定参考点。微光学平台的总面积约为1×1mm,激光芯片、微透镜和微棱镜的单个元件的最大尺寸为300μm。组装完成后,微光学平台相对于硅PIC上的光栅耦合器进行有源对准,1dB对准公差与光纤与PIC耦合相当(±2.5μm)。如果没有足够的散热,微光学平台上的激光芯片可能会过热,导致性能下降或烧毁。微光学平台与PIC以及TEC之间良好的热接触对于微光学平台的稳定运行是必要的[42]。

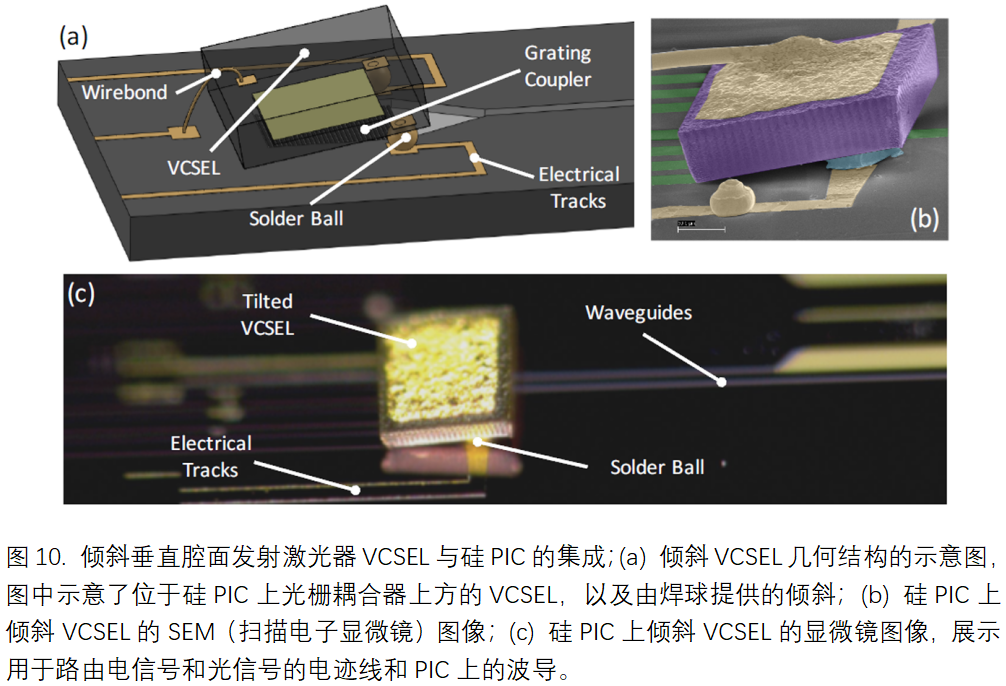

2.2.2. 垂直腔面发射激光器集成

垂直腔面发射激光器(VCSELs)的直接集成也是混合集成的一种很有前景的途径。与微光学平台(1×1mm)相比,VCSEL芯片(250×250μm)的占位面积显著减小,可以实现非常高的集成度。已有采用平面VCSEL与PIC的集成方案,其中基于光刻胶的“楔形物”用于将VCSEL模式折射到光栅耦合器上,具有所需的近法线入射角[43]。或者,可以设计光栅耦合器将垂直腔面发射激光器模式耦合到一对相对的波导中,在相位补偿后可以将其重新组合到单个通道中[44]。还可以使用倾斜垂直腔面发射激光器方法,其中垂直腔面发射激光器通过不对称分布的焊球直接倒装到PIC上[45],见图10。通过控制可用于焊料润湿的键合焊盘的接触面积,可以优化垂直腔面发射激光器的倾斜角度。这种倾斜垂直腔面发射激光器方法允许与PIC的倒装芯片无源对准,以实现商业化量产快速组装。

3. 电封装

对于电信和数通应用,光子器件需要高速且超高带宽地运行。这通常需要将多个25Gbps电通道多路复用/解复用为单N×25Gbps光通道,其中N=4、6、12等。需要将这些高速电信号从厘米级SMA(超小型A版)/SMK(超小型K版)连接器高效、低反射、无伪影地路由到PIC上的微观结构。如果需要与PIC进行大量电连接,或者需要在多个通道上进行精确(亚纳秒)的开关控制,还需要EIC驱动芯片的垂直集成。

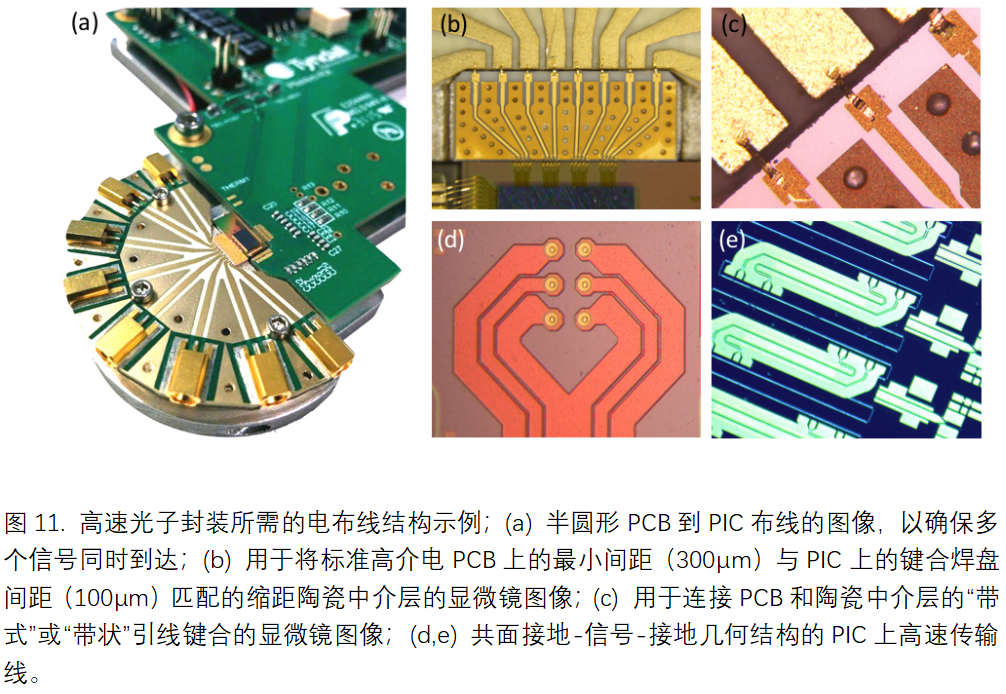

3.1. 高速布线

高速SMA(18-25GHz)和SMK(46GHz)连接器在PCB上的面积约为1cm²,而PIC上电键合焊盘的间距通常为100μm。因此,高速50Ω传输线的间距必须在连接器和PIC之间减小两个数量级,同时需控制不同通道的路径长度以保持信号时序。这通常导致PIC被圆形或半圆形PCB包围,其面积与电通道数量的平方成正比,见图11。

在标准高介电(Dₖ≈10)PCB上,最小特征尺寸将50Ω传输线的间距限制在约300μm,这比PIC上的键合焊盘间距大3倍。这个“差距”可以通过使用基于有限元模式(FEM)高频结构模拟器(HFSS)设计的缩距多层陶瓷中介层来弥合。与PCB相比,中介层提供更小的特征尺寸和更高的制造公差。中介层与PIC上的键合焊盘之间的电连接使用10-20μm直径的金线键合实现。对于直流(DC)连接,使用圆形横截面的引线键合,但对于高速连接,“带状”或“带式”引线键合具有更高的单位体积表面积,由于趋肤效应,对高速信号的电阻更低。

为减少感应效应,所有引线键合应尽可能短且直。这通常意味着PIC应嵌入到PCB中,以实现“齐平”引线键合。一旦连接到PIC,引线键合对任何剪切力都非常敏感,因此PIC、中介层和PCB必须在机械封装中刚性连接。引线键合的“滴胶”封装(使用硅树脂或环氧树脂)可以提供进一步的保护,但只能用于不会干扰光纤与PIC耦合或其他集成元件的封装中。

一旦传输到PIC,高速信号必须从键合焊盘路由到/来自相关的PIC上元件。尽管PCB和中介层上可以采用不同的横截面几何结构(微带、带状线和共面传输线),但硅晶圆厂的设计规则通常将高速传输线限制为共面几何结构。为避免显著的损耗和反射,必须使用HFSS在硅晶圆厂可用的特定材料和层厚度的边界条件内优化这些PIC上的传输线[6-8]。

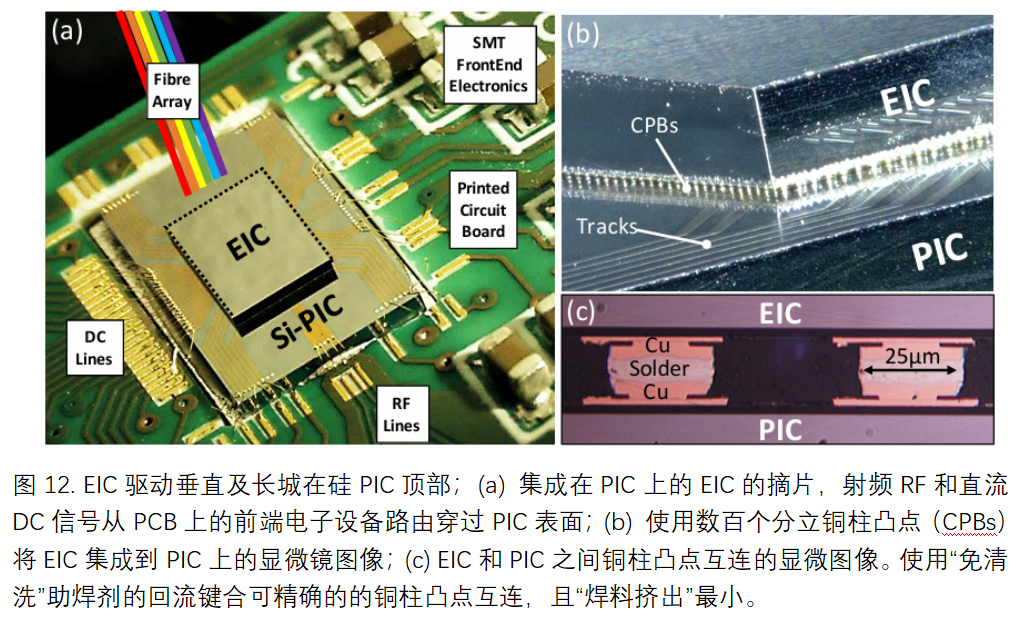

3.2. 垂直集成

将光子和电子功能单片集成到单个芯片上通常是大规模硅光子学的最终目标[4]。然而,在中低产量(每年10⁴-10⁵个芯片)下,将电子和光子功能垂直集成到两个单独的硅芯片上可以带来经济优势,因为可以采用不同的CMOS制程。具体而言,PIC的制造公差可以使用功能45nm制程在相对低成本的200mm晶圆上完成,而高性价比的EIC可能需要300mm晶圆上的14nm制程上进行。PIC的面积(10-30mm²)通常比典型的EIC大得多,因为有大型光子元件(AWGs、延迟线等)以及为光纤与PIC耦合预留的空间,因此不在更昂贵的CMOS制程上“浪费”这部分空间可以显著降低总体成本。

EIC与PIC的垂直集成可以使用焊球凸点(SBBs)或铜柱凸点(CPBs)互连实现,这些互连提供两个芯片之间的电机热接口[46,47]。特别是,垂直集成改善了与PIC的高速电子接口,它使用短的(≈10μm)凸点互连取代了长的(100-500μm)可能弯曲的引线键合,从而最大限度地减少了寄生感应效应[48-50],见图12。除了高速、高密度电子集成外,焊球凸点和铜柱凸点提供的机械连接还允许桥接不同的功能技术,如MEMS(微机电系统)、III-V族、非CMOS ASIC(专用集成电路)等[3]。

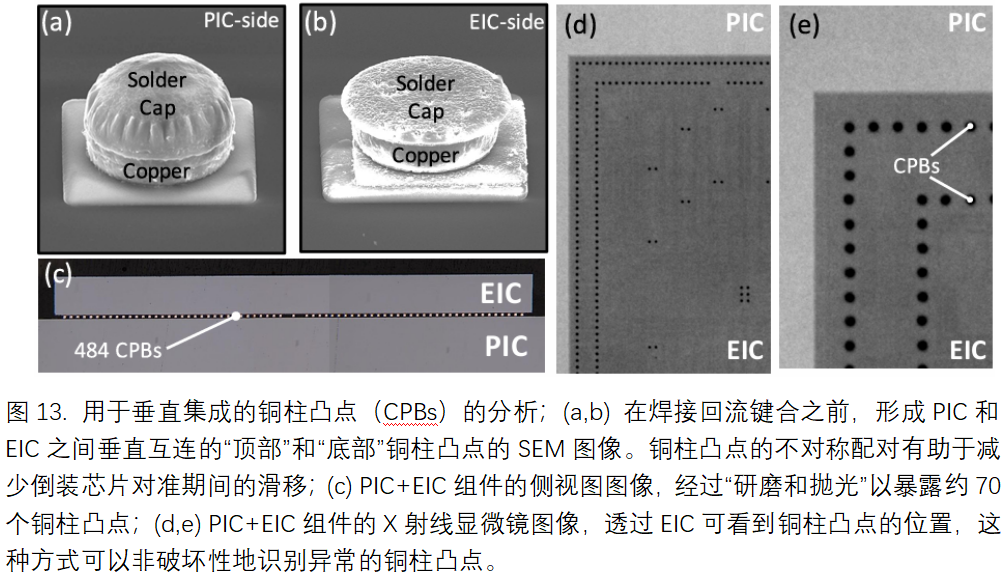

铜柱凸点的直径通常为20-30μm,通过在PIC和EIC上的凸点下金属焊盘上电镀铜,然后沉积(无铅)Sn-Ag-Cu焊料帽形成。通过使用倒装芯片系统的分束器相机对准两个芯片上的匹配铜柱凸点对;使两个芯片接触;然后应用热压焊或回流焊将成对的焊料帽融合在一起,实现PIC和EIC的垂直集成。这些焊料帽将被原生氧化层覆盖,必须去除以确保形成良好的电和机械互连[51]。电封装中使用的传统焊料通常不适用于光子封装,因为它们会留下化学残留物,污染光纤与PIC耦合的光学界面,这会导致插损增加,还会削弱光纤与PIC键合的机械强度。相反,在回流焊过程中应使用“免清洗”助焊剂。这种助焊剂不含挥发性有机化合物VOC,在焊料的熔点下活化并蒸发[52],因此不需要可能污染PIC的键合后溶剂冲洗[53,54]。

在倒装芯片系统中对准EIC和PIC,并应用“免清洗”助焊剂焊接回流周期(通常为250°C,30s)后,可以在顶部和底部铜柱凸点之间实现出色的键合。可以使用多种诊断方法——电阻测量、破坏性剥离测试和X射线显微镜——来评估铜柱凸点互连的质量。可以实现优于±1μm的对准,并几乎没有“焊料挤出”(这可能导致相邻互连之间的电短路),见图13。

4. PIC的热管理

光子元件,如半导体光放大器(SOAs)和微环谐振器,具有强烈的温度依赖性。20°C的温度变化通常足以使PIC偏离其工作范围[55,56]。光子器件中PIC的全局热稳定(通常使用TEC)对于需要在现场测试的样机至关重要,因为现场的季节性温度波动通常为±10°C。TEC提供的额外全局稳定性有助于更高效且更可重复地对PIC上的单个光子元件(如微环谐振器、热光移相器等)进行局部温度调谐。提高这些模块中TEC的性能系数(CoP)是降低已部署光子学运营成本的重要考虑因素。

图14展示了带有PIC和EIC的模块的典型热力图。电功率输送到EIC,通过焦耳加热转化为热功率(H=dQ/dt),然后通过焊球凸点或铜柱凸点互连层流入PIC。从那里,热量传导到散热板,并继续传导到TEC的“冷端”,再传导导模块的底板,最后通过被动对流/传导或“机架式”强制对流冷却将热量散发到周围环境中。

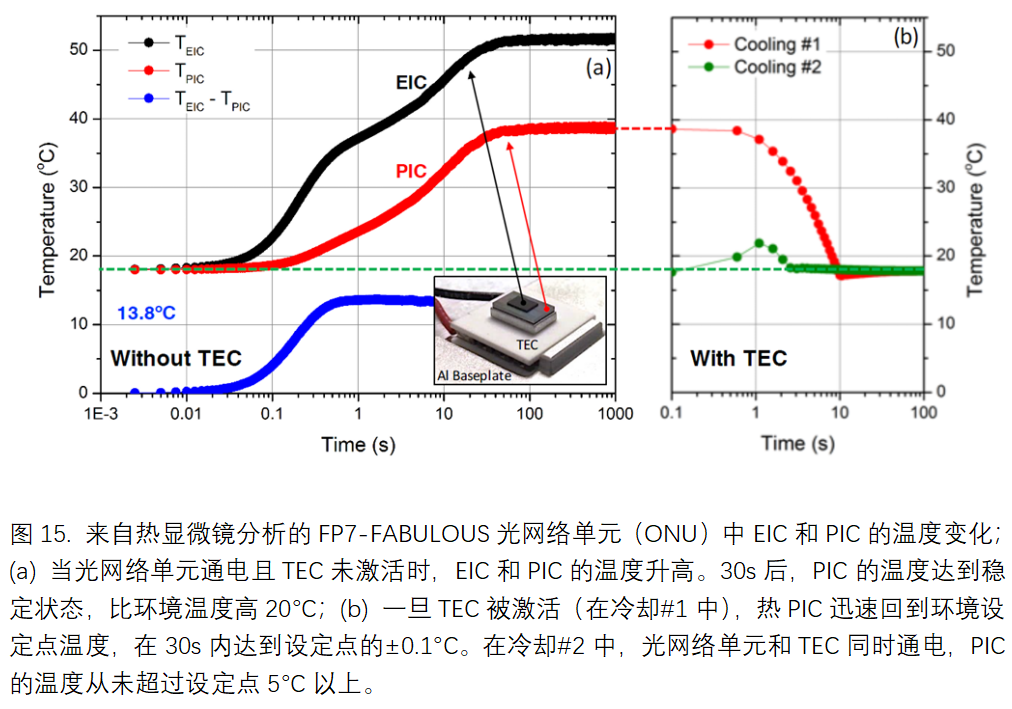

未受控制的焦耳热的影响可以通过在TEC断电时给EIC通电来说明,如图15所示。在为欧盟FP7“FABULOUS”项目开发的硅光子光网络单元(ONU)中,我们向EIC施加1.1W的功率,导致EIC和PIC的温度分别升高34°C和20°C[57]。我们使用热显微镜进行测量,该显微镜允许对PIC(100μm尺度)和整个光子模块(10cm尺度)进行精确的非接触温度测量。这些动态温度测量提供了关于热堆叠的热传导和热容量的定量信息。大致而言,这些动态测量中的“拐点”对应于热量“填充”堆叠中不同材料块所需的时间。EIC和PIC之间的稳态温差(ΔT=13.8°C)还可以对铜柱凸点互连层热阻(Rₜ)进行直接测量,即Rₜ=ΔT/H。整个铜柱凸点层的热阻为12.5K/W=13.2°C/1.1W,而互连层由484个铜柱凸点组成,进而得到每个互连的电阻为6.1×10³K/W。通过热显微镜测量的动态和稳态信息可用于验证当前的热模型,并优化未来的设计。

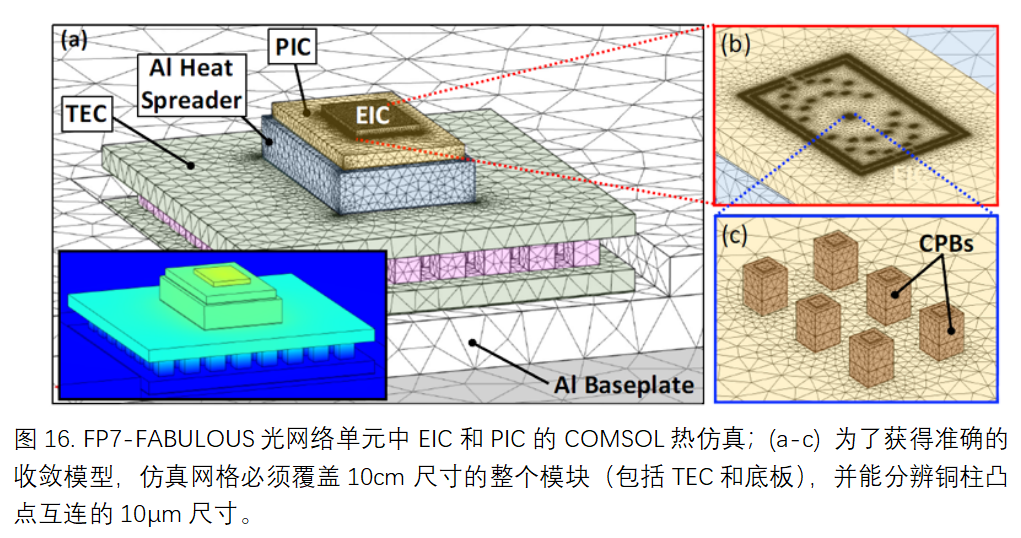

一旦TEC开启,PIC迅速稳定到外部PID控制器设置的温度(Tₛₚ)。在靠近PIC的热源附近放置一个微珠或SMT热敏电阻,以向PID控制器提供热监控反馈。对于来自“FABULOUS”项目的光网络单元,PIC在30s内稳定到Tₛₚ±0.1°C,在60s内稳定到Tₛₚ±0.01°C。在这种稳态下,当向EIC施加1.1W的电功率时,TEC需要消耗0.5W才能使PIC恢复到18°C的室温设定点,性能系数为2.2=1.1W/0.5W,并表明热管理占模块运行功率预算的30%= 0.5W/(0.5+1.1W)。通过改善模块内热量的分布和消散来提高PIC热电冷却的性能系数是一个活跃的研究课题。COMSOL中的有限元模拟可用于测试和优化新的堆叠设计,然后使用来自热显微镜的动态温度测量进行实验验证,见图16。

5. 光子封装的新兴技术

除了前几节描述的成熟技术外,已出现很多新兴技术,可能在将来会对光子封装技术产生重要的影响。

倏逝耦合的相同聚合物波导技术可以与电FR4(阻燃4级)PCB结合,创建一个能够将电信号和光信号从外部连接器路由到单个或多个硅PIC的平台[36]。与玻璃中介层相比,其主要优势是聚合物波导的成本优势和加工灵活性(即直接激光写入或光刻),特别是对于大面积情况,这些“光PCB”的预期传播距离在几十厘米范围内,因此需要克服的主要挑战是将波导传播损耗降低到0.1dB/cm以下。

卡尔斯鲁厄理工学院开发的光子引线键合(PWBs)为PIC与PIC[58]和多芯光纤与PIC[59]的光学连接提供了一种新的解决方案。这些PWB通过密集的聚焦的飞秒激光脉冲沿着连接两个光学界面(例如硅PIC上的倒锥与单模光纤的内芯)的自由3D路径曝光光刻胶。光子线键合的形状可以轻松调整,因此不需要在连接的PIC和光纤之间进行高精度机械对准,这对于未来的规模化是一个优势。目前,写入PWB还是串行方式,未来能否在晶圆级低成本的实施(每个晶圆需要数千或数万个光子线键合)还有待观察。

在光栅耦合器设计方面也有许多创新,包括用亚波长光刻特征取代单线沟槽,这可以采用高水平的折射率工程。在某些情况下,这些亚波长特征被设计为切趾结构,几乎完美地匹配入射光纤模式的轮廓[60],具有非常低(<1dB)的插损。另一种策略是使用亚波长光刻特征在SOI(绝缘体上硅)层中创建具有高度非线性图案的区域,形成一块超材料[61]。当这种超材料中的图案经过适当优化后,它可以将光从自由空间耦合到SOI波导中,甚至可以耦合不同偏振的光,类似二维光栅耦合器。这些超材料耦合器的效率至少与更标准的光栅耦合器相当,并且可以提供更宽的带宽,因为多个导模负责耦合,这使得超材料耦合器对波长偏移不太敏感。这两种亚波长耦合器方案的主要缺点是,它们通常只能通过电子束光刻制造,因为它们需要约100nm量级的特征尺寸,而硅光子晶圆厂通常使用的193nm深紫外光刻难以加工这些尺寸。在这些亚波长耦合器能够使用到可扩展的紫外光刻工艺之前,它们很难成为商用光子器件的标准化构件。

除了光纤与PIC的耦合外,光栅耦合器还可用于光学接近耦合或层间耦合[62-64],这允许高效的垂直芯片与芯片甚至板与芯片连接(结合上述光学PCB)。结合用于水平分布的低损耗波导,这种垂直芯片与芯片的光学连接使光能够在光学母板上进行3D集成路由到多个硅PIC。尽管光纤与PIC光栅耦合器的带宽通常相当窄(通常1dB带宽为30-40nm),但在光接近中,因为光栅之间的近场相互作用,同样的光栅将提供宽带耦合。同样的原因,两个相邻光栅耦合器之间的插损不仅仅是两个等效光纤与PIC界面的总和,它可以低得多,与单个光纤与PIC的量级相同。这些光学接近耦合器有望对晶圆级封装产生重大影响,因为它们允许不同光子系统的倒装芯片对准和/或晶圆键合,以用于先进的混合光子器件。

6. 光子封装趋势讨论

光子封装的高成本和低速度是开发具有竞争力的光子器件最显著的瓶颈。随着衍生公司努力将器件推向市场,以及大型跨国公司进入硅光子学领域,开发自动化封装工艺以实现更高产量的生产需求日益增长。明显的趋势是更紧凑的光子设计,更低的插入损耗、更高的集成度(电学和MEMS)、可扩展到多个25Gbps通道,以及高效(理想情况下被动)的热稳定性。为应对这一挑战,光子封装研究人员正从传统的个性化定制样机转向开发标准化和可扩展的解决方案。虽然光纤与PIC无源对准、更精确的倒装芯片垂直集成和更好的热堆叠设计等技术创新都发挥着重要作用,但“软”发展(如封装标准的发布和采用,以及材料和组件供应链的增长和整合)同样重要。

在硅光子学界,为光子封装创建标准化设计规则和标准的需求正逐渐得到认可。这种转变的驱动力是减轻研究人员/工程师的特定应用设计负担,并简化从设计到器件的流程。光子封装小组现在正与行业合作伙伴合作,建立封装设计套件(PDKs)和规则(PDRs),以支持非专业用户开发与最佳实践光子封装兼容的硅PIC。这有助于新用户避免问题,并避免昂贵且耗时的PIC重新设计。新用户经常忽视的重要封装设计规则包括:(i) 硅PIC上光栅耦合器阵列的间距(应与光纤通道的尺寸匹配,即127μm或250μm);(ii) 电键合焊盘的最小间距对于直流连接应>100μm(以最大化引线键合的良率),对于射频连接应>300μm(以消除对昂贵的陶瓷缩距中介层的需求);以及(iii) 光栅耦合器阵列周围需要一个“禁区”,其中不放置任何电连接或相位敏感组件,以防环氧树脂溢出。尽管目前处于发展的早期阶段,但预计这些封装设计规则将随着时间的推移得到扩展和正式化,并纳入硅晶圆厂的设计规则检查(DRC)中。简单的光子封装设计套件已经在PhoeniX BV(OptoDesigner)和Luceda(IPKISS)的PIC设计工具中在软件层面实现[65,66]。

7. 结论

光子封装是实现用于小规模样机制作和商业量产的高集成度硅光子器件的关键步骤。光子器件的封装通常是整个模块制造中最昂贵的部分,并且可能需要在PIC设计阶段关注。同时满足PIC的光学、电学和热学设计考虑因素需要一种“综合”方法,远远超出最广为人知的光纤与PIC耦合问题。封装研究人员越来越多地使用先进的设计工具和不断发展的封装设备来应对这些挑战。随着光子器件和技术走出实验室并进入市场,光子封装也在不断成熟以跟上步伐,其重点正从测试和样机制作转向标准化和可扩展的商业实施。

参考文献

1. Streshinsky, M.; Ding, R.; Liu, Y.; Novack, A.; Galland, C.; Lim, A.; Guo-Qiang, P.L.; Baehr-Jones, T.;Hochberg, M. The road to affordable, large-scale silicon photonics. Opt. Photon. News 2013, 24, 32–39.

2. Soref, R. The past, present, and future of silicon photonics. IEEE J. Sel. Top. Quantum Electron. 2006, 12,1678–1687.

3. Arakawa, Y.; Nakamura, T.; Urino, Y.; Fujita, T. Silicon photonics for next generation system integration platform. IEEE Commun. Mag. 2013, 51, 72–77.

4. Tsybeskov, L.; Lockwood, D.J.; Ichikawa, M. Silicon photonics: CMOS going optical [Scanning the Issue]. Proc. IEEE 2009, 97, 1161–1165.

5. Sun, C.; Wade, M.T.; Lee, Y.; Orcutt, J.S.; Alloatti, L.; Georgas, M.S.; Waterman, A.S.; Shainline, J.M.; Avizienis, R.R.; Lin, S.; et al. Single-chip microprocessor that communicates directly using light. Nature 2015, 528, 534–538. [PubMed]

6. Integrated Silicon Photonics ICs with MPW Service. Available online: http://www2.imec.be/be_en/services-and-solutions/silicon-photonics.html (accessed on 15 October 2016).

7. CEA-LETI Full Platform in MPW. Available online: http://www-leti.cea.fr/en/How-to-collaborate/Focuson-Technologies/Integrated-silicon-photonics (accessed on 15 October 2016).

8. Silicon Photonics Multiple-ProjectsWafer. Available online: http://www.a-star.edu.sg/ime/SERVICES/silicon_photonics_multi-projects-wafer.aspx (accessed on 1 December 2016).

9. Zimmermann, L.; Preve, G.B.; Tekin, T.; Rosin, T.; Landles, K. Packaging and assembly for integrated photonics—Review of the ePIXpack photonics packaging platform. IEEE J. Sel. Top. Quantum Electron. 2011,17, 645–651.

10. Kopp, C.; Bernabé, S.; Bakir, B.B.; Fedeli, J.-M.; Orobtchouk, R.; Schrank, F.; Porte, H.; Zimmermann, L.;Tekin, T. Silicon photonic circuits: On-CMOS integration, fiber optical coupling, and packaging. IEEE J. Sel.Top. Quantum Electron. 2011, 17, 498–509.

11. O’Brien, P.; Carroll, L.; Eason, C.; Lee, J.-S. Packaging of Silicon Photonic Devices. In Silicon Photonics III; Pavesi, L., Lockwood, D.J., Eds.; Springer: Berlin/Heidelberg, Germany, 2016; Volume 122, pp. 217–236.

12. Lee, J.-S.; Carroll, L.; Scarcella, C.; Pavarelli, N.; Menezo, S.; Bernabe, S.; Temporiti, E.; O’Brien, P. Meeting the electrical, optical, and thermal design challenges of photonic-packaging. IEEE J. Sel. Top. Quantum Electron.2016, 22.

13. Taillaert, D.; Van Laere, F.; Ayre, M.; Bogaerts, W.; Van Thourhout, D.; Bienstman, P.; Baets, R. Grating couplers for coupling between optical fibers and nanophotonic wave-guides. Jpn. J. Appl. Phys. 2006, 45, 6071–6077.

14. Taillaert, D.; Chong, H.; Borel, P.I.; Frandsen, L.H.; De La Rue, R.M.; Baets, R. A compact two-dimensional grating coupler used as a polarization splitter. IEEE Photonics Technol. Lett. 2003, 15, 1249–1251.

15. Fukuda, H.; Yamada, K.; Tsuchizawa, T.; Watanabe, T.; Shinojima, H.; Itabashi, S. Silicon photonic circuit with polarization diversity. Opt. Express 2008, 16, 4872–4880. [PubMed]

16. Song, J.; Fernando, H.; Roycroft, B.; Corbett, B.; Peters, F. Practical Design of Lensed Fibers for Semiconductor Laser Packaging Using Laser Welding Technique. J. Lightwave Technol. 2009, 27, 1533–1539.

17. McNab, S.; Moll, N.; Vlasov, Y. Ultra-low loss photonic integrated circuit with membrane-type photonic crystal waveguides. Opt. Express 2003, 11, 2927–2939. [PubMed]

18. Shoji, T.; Tsuchizawa, T.;Watanabe, T.; Yamada, K.; Morita, H. Low loss mode size converter from 0.3 _m square Si wire waveguides to singlemode fibers. Electron. Lett. 2002, 38, 1669–1670.

19. Pu, M.; Liu, L.; Ou, H.; Yvind, K.; Hvam, J.M. Ultra-low-loss inverted taper coupler for silicon-on-insulator ridge waveguide. Opt. Commun. 2010, 283, 3678–3682.

20. Galán, J.; Sanchis, P.; Sánchez, G.; Martí, J. Polarization insensitive low-loss coupling technique between SOI waveguides and high mode field diameter single-mode fibers. Opt. Express 2007, 15, 7058–7065. [PubMed]

21. Romero-Garcıa, S.; Marzban, B.; Merget, F.; Shen, B.; Witzens, J. Edge couplers with relaxed alignment tolerance for pick-and-place hybrid integration of III–V lasers with SOI waveguides. IEEE J. Sel. Top. Quantum Electron. 2014, 20. Appl. Sci. 2016, 6, 426 19 of 21

22. Papes, M.; Cheben, P.; Ye, W.N.; Schmid, J.H.; Xu, D.X.; Janz, S.; Benedikovic, D.; Ramos, C.A.; Halir, R.; Ortega-Moñux, A.; et al. Fiber-chip edge coupler with large mode size for silicon photonic wire waveguides. In Proceedings of the SPIE (9516), Integrated Optics: Physics and Simulations II (95160K), Prague, Czech Republic, 1 May 2015.

23. Solutions for Si-Photonics Connection. Available online: http://www.teemphotonics.com/ioc/offer-andproducts/solutions-for-si-photonics-connection.html (accessed on 15 October 2016).

24. Van Laere, F.; Claes, T.; Schrauwen, J.; Scheerlinck, S.; Bogaerts, W.; Taillaert, D.; O’Faolain, L.; Van Thourhout, D.; Baets, R. Compact focusing grating couplers for silicon-on-insulator integrated circuits. IEEE Photonics Technol. Lett. 2007, 19, 1919–1921.

25. Roelkens, G.; Vermeulen, D.; Selvaraja, S.; Halir, R.; Bogaerts,W.; Van Thourhout, D. Grating-based optical fiber interfaces for silicon-on-insulator photonic integrated circuits. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 571–580.

26. Snyder, B.; O’Brien, P. Planar fiber packaging method for silicon photonic integrated circuits. In Proceedings of the Optical Fiber Communication Conference, Optical Society of America (OM2E.5), Los Angeles, CA, USA, 4–8 March 2012.

27. Li, C.; Chee, K.; Tao, J.; Zhang, H.; Yu, M.; Lo, G. Silicon photonics packaging with lateral fiber coupling to apodized grating coupler embedded circuit. Opt. Express 2014, 22, 24235–24240. [PubMed]

28. Vermeulen, D.; Selvaraja, S.; Verheyen, P.; Lepage, G.; Bogaerts, W.; Absil, P.; Van Thourhout, D.; Roelkens, G. High-efficiency fiber-to-chip grating couplers realized using an advanced CMOS-compatible Silicon-On-Insulator platform. Opt. Express 2010, 18, 18278–18283. [PubMed]

29. Xia, C.; Chao Li, L.; Fung, C.K.Y.; Lo, S.M.G.; Tsang, H.K. Apodized waveguide grating couplers for efficient coupling to optical fibers. IEEE Photonics Technol. Lett. 2010, 22, 1156–1158.

30. Zaoui, W.S.; Kunze, A.; Vogel, W.; Berroth, M.; Butschke, J.; Letzkus, F.; Burghartz, J. Bridging the gap between optical fibers and silicon photonic integrated circuits. Opt. Express 2014, 22, 1277–1286. [PubMed]

31. Pathak, S.; Vanslembrouck, M.; Dumon, P.; Van Thourhout, D.; Bogaerts,W. Compact SOI-based polarization diversity wavelength de-multiplexer circuit using two symmetric AWGs. Opt. Express 2012, 20, B493–B500. [PubMed]

32. Carroll, L.; Gerace, D.; Cristiani, I.; Menezo, S.; Andreani, L. Broad parameter optimization of polarization-diversity 2D grating couplers for silicon photonics. Opt. Express 2013, 21, 21556–21568. [PubMed]

33. Carroll, L.; Gerace, D.; Cristiani, I.; Andreani, L. Optimizing polarization-diversity couplers for Si-photonics: reaching the ��1 dB coupling efficiency threshold. Opt. Express 2014, 22, 14769–14781. [PubMed]

34. Snyder, B.; O’Brien, P. Packaging process for grating-coupled silicon photonic wave-guides using angle-polished fibers. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 954–959.

35. Pavarelli, N.; Lee, J.-S.; Rensing, M.; Scarcella, C.; Zhou, S.; Ossieur, P.; O’Brien, P. Optical and Electronic Packaging Processes for Silicon Photonic Systems. J. Lightwave Technol. 2015, 33, 991–997.

36. Dangel, R.; Hofrichter, J.; Horst, F.; Jubin, D.; La Porta, A.; Meier, N.; Soganci, I.; Weiss, J.; Offrein, B. Polymer waveguides for electro-optical integration in data centers and high-performance computers. Opt. Express 2015, 23, 4736–4750. [PubMed]

37. Van Campenhout, J.; Rojo Romeo, P.; Regreny, P.; Seassal, C.; Van Thourhout, D.; Verstuyft, S.; Di Cioccio, L.; Fedeli, J.; Lagahe, C.; Baets, R. Electrically pumped in P-based microdisk lasers integrated with a nanophotonic silicon-on-insulator waveguide circuit. Opt. Express 2007, 15, 6744–6749. [PubMed]

38. Keyvaninia, S.; Roelkens, G.; Van Thourhout, D.; Jany, C.; Lamponi, M.; Le Liepvre, A.; Lelarge, F.; Make, D.; Duan, G.; Bordel, D.; et al. Demonstration of a heterogeneously integrated III-V/SOI single wavelength tunable laser. Opt. Express 2013, 21, 3784–3792. [PubMed]

39. Park, H.; Fang, A.W.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. A Hybrid Al-Gainas-Silicon evanescent amplifier. IEEE Photonics Technol. Lett. 2007, 19, 230–232.

40. Mack, M.; Peterson, M.; Gloeckner, S.; Narasimha, A.; Koumans, R.; De Dobbelaere, P. Method and System for a Light Source Assembly Supporting Direct Coupling to an Integrated Circuit. US Patent 8,168,939 B2, 1 May 2012. Appl. Sci. 2016, 6, 426 20 of 21

41. Snyder, B.; Corbett, B.; O’Brien, P. Hybrid integration of the wavelength-tunable laser with a silicon photonic integrated circuit. J. Lightwave Technol. 2013, 31, 3934–3942.

42. O’Carroll, J.; Phelan, R.; Kelly, B.; Byrne, D.; Barry, L.; O’Gorman, J.Wide temperature range 0 < T < 85 _C narrow linewidth discrete mode laser diodes for coherent communications applications. Opt. Express 2011,19, B90–B95. [PubMed]

43. Kaur, K.S.; Subramanian, A.Z.; Cardile, P.; Verplancke, R.; Van Kerrebrouck, J.; Spiga, S.; Meyer, R.; Bauwelinck, J.; Baets, R.; Van Steenberge, G. Flip-chip assembly of VCSELs to silicon grating couplers via laser fabricated SU8 prisms. Opt. Express 2015, 23, 28264–28270. [PubMed]

44. Ferrara, J.; Yang,W.; Zhu, L.; Qiao, P.; Chang-Hasnain, C.J. Heterogeneously integrated long-wavelength VCSEL using silicon high contrast grating on an SOI substrate. Opt. Express 2015, 23, 2512–2523. [PubMed]

45. Lu, H.; Lee, J.-S.; Zhao, Y.; Scarcella, C.; Cardile, P.; Daly, A.; Ortsiefer, M.; Carroll, L.; O’Brien, P. Flip-chip integration of tilted VCSELs onto a silicon photonic integrated circuit. Opt. Express 2016, 24, 16258–16266. [PubMed]

46. Worhoff, K.; Heideman, R.G.; Gilde, M.J.; Blidegn, K.; Heschel, M.; Van den Vlekkert, H. Flip-chip assembly for photonic circuits. In Proceedings of the SPIE 5454, Micro-Optics: Fabrication, Packaging, and Integration Strasbourg, France, 8 September 2004.

47. Zhang, X.R.; Zhu,W.H.; Liew, B.P.; Gaurav, M.; Yeo, A.; Chan, K.C. Copper pillar bump structure optimization for flip chip packaging with Cu/Low-K stack. In Proceedings of the 11th International Conference on Thermal, Mechanical & Multi-Physics Simulation, and Experiments in Microelectronics and Microsystems (EuroSimE), Bordeaux, France, 26–28 April 2010.

48. Chen, K.M.; Lin, T.S. Copper pillar bump design optimization for lead free flip-chip packaging. J. Mater. Sci. Mater. Electron. 2010, 21, 278–284.

49. Garrou, P.; Bower, C.; Ramm, P. Chapter1: Introduction to 3D Integration in Handbook of 3D Integration Volume 1—Technology and Applications of 3D Integrated Circuits; Wiley-VCH: Weinheim, Germany, 2008.

50. Fedeli, J.M.; Di Cioccio, L.; Marris-Morini, D.; Vivien, L.; Orobtchouk, R.; Rojo-Romeo, P.; Seassal, C.; Mandorlo, F. Development of silicon photonics devices using microelec-tronic tools for the integration on top of a CMOS wafer. Adv. Opt. Technol. 2008.

51. Wang, Y.-H.; Howlader, M.R.; Nishida, K.; Kimura, T.; Suga, T. Study on Sn-Ag Oxidation and Feasibility of Room Temperature Bonding of Sn-Ag-Cu Solder. Mater. Trans. 2005, 46, 2431–2436.

52. Multicore MF210 VOC-free No Clean Flux. Available online: http://www.henkel-adhesives.com (accessed on 15 October 2016).

53. Horibe, A.; Lee, K.-W.; Okamoto, K.; Mori, H.; Orii, Y. No Clean Flux Technology for Large Die Flip Chip Packages. In Proceedings of the IEEE Electronic Components & Technology Conference, Las Vegas, NV, USA, 28–31 May 2013.

54. Choon-Mei, S.L.; Marbella, C.; Min, T.A. No-clean Polymer Flux Evaluations and its Impact on BGA Solder Joint Quality and Board Level Reliability. In Proceedings of the 34th International Electronic Manufacturing Technology Conference, Melaka, Malaysia, 30 November–2 December 2010.

55. Baehr-Jones, T.; Pinguet, T.; Guo-Qiang, P.L.; Danziger, S.; Prather, D.; Hochberg, M. Myths and rumours of silicon photonics. Nat. Photonics 2012, 6, 206–208.

56. Kaspar, P.; Brenot, R.; Le liepvre, A.; Accard, A.; Make, D.; Levaufre, G.; Girard, N.; Lelarge, F.; Dan, G.-H.; Pavarelli, N.; et al. Packaged hybrid III-V/silicon SOA. In Proceedings of the European Conference on Optical Communication (ECOC), Cannes, France, 21–25 September 2014; pp. 1–3.

57. FDMA Access by Using Low-Cost Optical Network Units in Silicon Photonics. Available online: http://www.fabulous-project.eu (accessed on 15 October 2016).

58. Lindenmann, N.; Balthasar, G.; Hillerkuss, D.; Schmogrow, R.; Jordan, M.; Leuthold, J.; Freude,W.; Koos, C. Photonic wire bonding: A novel concept for chip-scale interconnections. Opt. Express 2012, 20, 17667–17677. [PubMed]

59. Lindenmann, N.; Dottermusch, S.; Goedecke, M.L.; Hoose, T.; Billah, M.R.; Onanuga, T.; Hofmann, A.; Freude, W.; Koos, C. Connecting silicon photonic circuits to multi-core fibers by photonic wire bonding. J. Lightwave Technol. 2015, 33, 755–760. Appl. Sci. 2016, 6, 426 21 of 21

60. Benedikovic, D.; Cheben, P.; Schmid, J.H.; Xu, D.-X.; Lamontagne, B.; Wang, S.; Lapointe, J.; Halir, R.; Ortega-Monux, A.; Janz, S.; et al. Subwavelength index engineered surface grating coupler with sub-decibel efficiency for 220-nm silicon-on-insulator waveguides. Opt. Express 2015, 23, 22628–22635. [PubMed]

61. Shen, B.; Wang, P.; Polson, R.; Menon, R. Integrated metamaterials for efficient and compact free-spaceto-waveguide coupling. Opt. Express 2014, 22, 27175–27182. [PubMed]

62. Yao, J.; Zheng, X.; Li, G.; Shubin, I.; Luo, Y.; Thacker, H.; Mekis, A.; Pinguet, T.; Sahni, S.; Raj, K.; et al. Grating-coupler-based optical proximity coupling for scalable computing systems. SPIE Proc. 2011.

63. Sodagar, M.; Pourabolghasem, R.; Eftekhar, A.A.; Adibi, A. High-efficiency and wideband interlayer grating couplers in multilayer Si/SiO2/SiN platform for 3D integration of optical functionalities. Opt. Express 2014, 22, 16767–16777. [PubMed]

64. Bernabé, S.; Kopp, C.; Volpert, M.; Harduin, J.; Fédéli, J.-M.; Ribot, H. Chip-to-chip optical interconnections between stacked self-aligned SOI photonic chips. Opt. Express 2012, 20, 7886–7894. [PubMed]

65. PhoeniX Software—Solutions for Micro and Nano Technologies. Available online: http://www.phoenixbv.com (accessed on 15 October 2016).

66. Luceda Photonics—Software and Services for Integrated Photonic Designers. Available online: http://www.lucedaphotonics.com/en (accessed on 15 October 2016).

审核编辑 黄宇

-

先进PIC光子集成工艺2025-09-18 1320

-

集成电路和光子集成技术的发展历程2025-03-12 2386

-

从数据中心到量子计算,光子集成电路引领行业变革2025-01-13 1363

-

凌云光达成战略合作!押注光子集成芯片封装技术发展2024-10-15 1659

-

光子集成芯片和光子集成技术是什么2024-03-25 2855

-

光子集成芯片是什么2024-03-22 2960

-

微波光子集成芯片和硅基光子集成芯片的区别2024-03-20 2518

-

硅光子温度传感器:从光子集成芯片到完整封装微型探针2023-12-25 2687

-

光子集成电路(PIC)加速未来光子芯片的开发周期2023-07-31 6521

-

什么是光子集成芯片(PIC)?2023-01-10 19072

-

电力电子集成模块封装构成与研究重点2018-08-28 6173

-

光子集成又一重大技术突破!光子电路放置纳米线成为现实。2018-07-11 2170

全部0条评论

快来发表一下你的评论吧 !