TPSM6440x双输出功率模块技术解析与应用指南

描述

Texas Instruments TPSM64404/TPSM64406双输出功率模块是一种高度集成的36V输入DC-DC设计,在增强型HotRod™ QFN封装中结合了屏蔽电感器、功率MOSFET和无源器件。该器件采用交错、可堆叠的电流模式控制架构,支持双路或大电流单路输出,具有快速瞬态响应、易于环路补偿、出色的负载和线路调节能力。它还包括精确的电流共享功能,输出时钟支持多达六个相位,电流最大可达18A。模块的VIN 和VOUT 引脚位于封装角落,可优化输出和输入电容器的布局。模块下方的大型散热焊盘便于在生产过程中进行操作和简单布局。

数据手册:*附件:Texas Instruments TPSM64404,TPSM64406双输出功率模块数据手册.pdf

Texas Instruments TPSM64404/TPSM64406输出电压范围为1 V至16 V,设计用于以PCB占位面积实现低EMI设计。整个设计仅需6个外部元件,设计过程中无需选择磁性元件。

特性

- 多功能双输出电压或多相单输出同步降压模块

- 集成MOSFET、电感器和控制器

- 3 V 至 36 V 的宽输入电压范围

- 可调输出电压降为 0.8 V 至 16 V

- 6.5 mm × 7.0 mm × 2 mm包覆成型封装

- -40 °C至+125 °C结温范围

- 负输出电压能力

- 在整个负载范围内具有超高效率

- 峰值效率:93.5%+

- 用于提升效率的外部偏置选项

- 裸露焊盘以实现低热阻抗 (EVM θ

JA= 20°C/W) - 关断静态电流:0.6µA(典型值)

- 超低传导和辐射EMI特性

- 低噪声封装,具有双输入路径和集成电容器,可减少开关振铃

- 符合CISPR 11和32 B类排放标准

- 专为可扩展电源设计

- 固有保护特性可实现稳健设计

- 用于排序、控制和V

INUVLO的精密使能输入和开漏PGOOD指示器 - 过电流和热关断保护

- 用于排序、控制和V

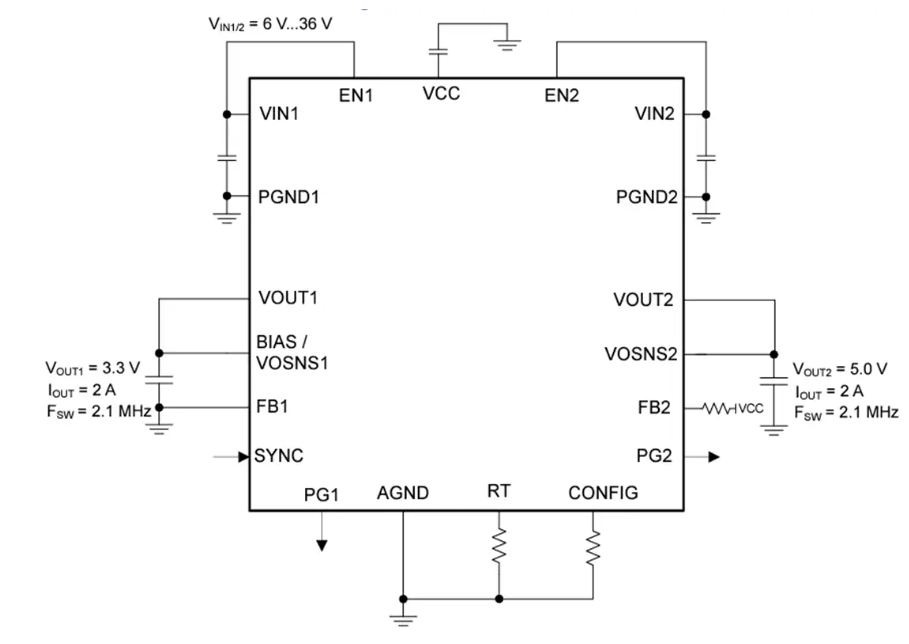

典型原理图

TPSM6440x双输出功率模块技术解析与应用指南

一、产品概述与核心特性

Texas Instruments TPSM64404/TPSM64406是高度集成的双输出DC/DC功率模块,具有以下显著特点:

关键规格参数:

- 输入电压范围:3V至36V(瞬态耐受42V)

- 输出配置:

- 双独立输出模式:2×2A(TPSM64404)或2×3A(TPSM64406)

- 多相单输出模式:最高6相并联(18A输出能力)

- 封装尺寸:6.5mm×7.0mm×2mm增强型HotRod QFN

- 效率特性:峰值效率93.5%,待机静态电流仅0.6μA

创新技术亮点:

- 集成化设计:包含功率MOSFET、屏蔽电感和控制器

- EMI优化:通过双随机展频(DRSS)技术满足CISPR 11/32 Class B标准

- 热管理:20°C/W的低热阻封装设计

- 配置灵活性:支持I2C接口编程和OTP固化配置

二、硬件设计要点

1. 引脚配置与功能

关键引脚说明:

| 引脚名称 | 功能描述 |

|---|---|

| VIN1/VIN2 | 双路独立输入电源,需各配置≥10μF陶瓷电容 |

| EN1/EN2 | 精密使能输入(1.375V阈值) |

| FB1/FB2 | 反馈输入,支持0.8V-16V可调输出 |

| SYNC | 同步/模式选择(支持200kHz-2.2MHz外部时钟) |

| CONFIG | 工作模式配置(通过电阻选择双输出/多相模式) |

2. 典型应用电路

双输出配置方案:

. 电源树设计:

- 输入级:4×10μF陶瓷电容+100μF电解电容

- 输出级:每路2×22μF陶瓷电容(25V)

多相并联方案:

- 4相配置:主从器件SYNC_OUT→SYNC级联,90°相位差

- 6相配置:三级级联实现60°相位差

三、性能优化策略

1. EMI抑制技术

三级降噪方案:

- 布局优化:

- VIN/VOUT对称布局(磁通抵消效应)

- 开关节点面积<5mm²

- 频谱管理:

- DRSS调制(±10%频率展宽)

- 可编程开关频率(300kHz-2.2MHz)

- 滤波器设计:

- 输入级π型滤波(2×10μF+铁氧体磁珠)

2. 热设计指南

散热增强措施:

- PCB要求:

- 2oz铜厚四层板

- 9×150μm热过孔阵列

- 最小15mm²散热铜箔

- 降额曲线:| 环境温度 | 最大输出电流 |

| ---------- | -------------- |

| 85°C | 100%额定值 |

| 105°C | 80%额定值 |

| 125°C | 60%额定值 |

四、典型应用场景

1. 工业自动化系统

供电方案:

- 数字核心:1.2V/3A(BUCK1)

- 接口电源:3.3V/2A(BUCK2)

- 传感器供电:5V/1A(LDO_LS1)

关键设置:

- 固定频率PWM模式(SYNC接VCC)

- 启用输入UVLO(RENT=187kΩ,RENB=49.9kΩ)

2. 测试测量设备

信号链供电:

- ADC基准:5V/0.5A(噪声<10mVpp)

- 模拟前端:±15V(通过逆变拓扑实现)

- 时钟电路:3.3V/1A(单独供电隔离)

五、设计资源

1. 开发工具

- WEBENCH®设计平台:支持在线原理图生成和BOM优化

- TPSM64406EVM评估板:包含双输出和6相配置示例

2. 参考设计

- 多相并联方案:

- 输入:12-24V

- 输出:1V/18A(6相交错)

- 效率:91%@满载

- 负压生成方案:

- 输入:15V

- 输出:-5V/3A

- 拓扑:逆变Buck-Boost

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPSM8291x 低噪声降压电源模块:特性、应用与设计指南2026-03-03 275

-

TPSM6440xx模块:高效、低EMI的电源解决方案2026-03-02 817

-

TPSM8282x电源模块技术解析与应用指南2025-10-06 1538

-

TPSM8290x评估模块技术分析与应用指南2025-09-15 738

-

低噪声Buck电源模块TPSM8291x的技术解析与应用指南2025-09-08 1059

-

Texas Instruments TPSM64406EVM评估模块技术解析与应用指南2025-09-06 1405

-

TPSM82816EVM评估模块技术解析与应用指南2025-08-29 1061

-

德州仪器TPSM86325x系列3A同步降压模块技术解析2025-08-15 1169

-

TPSM64406 高密度、36V、0.8V 至 16V 输出、双 3A 输出功率模块数据手册2025-04-17 1294

-

TPSM84203、TPSM84205、TPSM84212、电源模块 EVM 用户指南2024-12-29 440

-

TPSM8291x降压电源模块评估模块用户指南2024-11-18 455

-

TPSM84x24电源模块评估模块用户指南2024-11-16 545

全部0条评论

快来发表一下你的评论吧 !