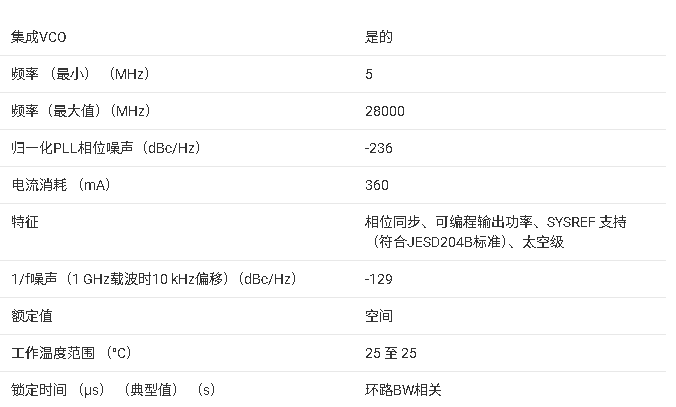

LMX2624-SP 5MHz至28GHz宽带合成器技术文档总结

描述

LMX2624-SP 是一款高性能宽带锁相环 (PLL),集成了压控振荡器 (VCO) 和稳压器,可输出 5MHz 和 28GHz 的任何频率。该器件上的VCO覆盖整个倍频程,因此频率覆盖范围低至5MHz。具有–236dBc/Hz品质因数和高鉴相器频率的高性能PLL可以实现极低的带内噪声和集成抖动。

*附件:lmx2624-sp.pdf

LMX2624-SP 允许用户同步设备多个实例的输出。这意味着可以在用例中从器件获得确定性相位,包括启用了分数引擎或输出分频器的用例。该器件还支持生成或重复 SYSREF(符合 JESD204B/C 标准),使该器件专为高速数据转换器的低噪声时钟源而设计。

该器件采用德州仪器 (TI) 先进的 BiCMOS 工艺制造,采用 64 引脚 QFP 塑料封装。

特性

- 贴片 5962R2321001PXE

- 总电离剂量 100Krad(不含 ELDRS)

- 单事件闩锁 (SEL) 免疫高达 75MeV-cm2/mg

- 单事件功能中断 (SEFI) 免疫高达 75MeV-cm2/mg

- 宽带频率合成器:5MHz至28GHz输出频率

- 100kHz偏移时相位噪声为–101dBc/Hz,24GHz载波

- 24GHz时为60fs RMS抖动(1kHz至300MHz)

- 可编程输出功率

- PLL 主要规格:

- 品质因数:–236dBc/Hz

- 归一化1/f噪声:–129dBc/Hz

- 高达 200MHz 的鉴相器频率

- 跨多个设备同步输出相位

- 用于 RFoutA 和 RFoutB 的独立静音引脚,静音/取消静音时间为 200ns

- 支持具有 9ps 分辨率可编程延迟的 SYSREF

- 3.3V单电源供电

- 引脚模式:引脚可配置的 N 分频器和输出分频器,采用整数 PLL 模式

- 10 × 10mm² 64引脚QFP封装

- 工作温度范围:–55°C 至 +125°C

- 由PLLatinum™模拟器设计工具支持

参数

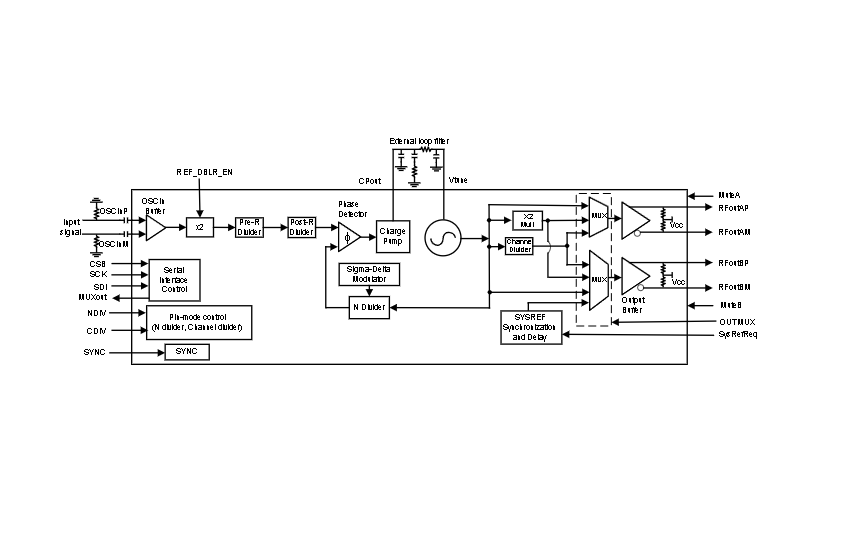

方框图

1. 核心特性

- 频率范围:5MHz至28GHz宽频输出,集成VCO(7500-15000MHz)及倍频/分频器

- 相位噪声:-101dBc/Hz @100kHz偏移(24GHz载波),60fs RMS抖动(1kHz-300MHz)

- 同步功能:支持多设备相位同步及JESD204B/C标准SYSREF生成(9ps可编程延迟)

- 抗辐射设计:100krad总电离剂量(TID),75MeV-cm²/mg抗单粒子锁定(SEL)和功能中断(SEFI)

- 封装:10×10mm² 64引脚QFP,工作温度-55°C至+125°C

2. 关键模块

- PLL性能:

- 相位检测频率达200MHz(分数模式)/250MHz(整数模式)

- 噪声指标:FOM -236dBc/Hz,1/f噪声-129dBc/Hz

- 输出控制:

- 独立可编程功率(-30至+3dBm差分输出)

- 快速静音/解除静音(200ns切换时间)

- 参考路径:支持输入倍频(OSC_2X)、预分频(PLL_R_PRE)和后分频(PLL_R)

3. 应用场景

- 太空通信(Ku/Ka波段)、雷达系统

- 高速数据转换器时钟(JESD204B/C兼容)

- 混频器本地振荡器(至28GHz)

4. 工作模式

- SPI模式:通过寄存器配置频率/功能,支持分数N分频(32位分辨率)

- 引脚模式:通过CDIVx/NDIVx引脚设置固定整数分频比(4电平引脚控制)

- 同步模式:SYNC引脚实现确定性相位,支持MASH_SEED微调(精度达VCO周期/分母值)

5. 设计支持

- 配套PLLatinum Simulator工具用于环路滤波器设计和噪声仿真

- 提供EVK硬件及软件,验证布局/散热建议(如 Rogers 4350B板材优先)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索LMX2820 22.6-GHz宽带PLLatinum™ RF合成器的卓越性能2026-02-08 587

-

LMX2624-SP:高性能宽带频率合成器的深度剖析与设计指南2026-02-06 286

-

LMX2624-SP:高性能宽带频率合成器的深度解析2026-01-26 474

-

LMX2571 低功耗高性能射频合成器技术文档总结2025-09-14 1474

-

LMX2820 22.6 GHz宽带PLLatinum™射频合成器技术文档总结2025-09-12 1537

-

LMX2571-EP 低功耗高性能射频合成器技术文档总结2025-09-11 1001

-

LMX2615EVM-CVAL宽带15GHz合成器2024-11-19 369

-

采用LMX2592低噪宽带RF PLL射频高性能合成器参考设计2022-09-22 2015

全部0条评论

快来发表一下你的评论吧 !