CDCE421A 时钟发生器芯片技术文档总结

描述

CDCE421A是一款高性能、低相位噪声时钟发生器。它有两个完全集成、低噪声、基于 LC 的压控振荡器 (VCO),可在 1.750 GHz 至 2.350 GHz 频率范围。它还具有集成晶体振荡器,与外部AT切割晶体配合使用,以产生稳定的频率 基于锁相环 (PLL) 频率合成器的参考。

输出频率(f 外 )与输入晶体的频率成正比(f XTAL的 ).预分频器分频器、反馈分频器、输出分频器和VCO 选择设置相对于 f 的输出频率 XTAL的 .

*附件:cdce421a.pdf

在CDCE421A中,反馈分频器是相对于预分频器设置自动设置的。如图所示,预分频器和反馈分频器的乘积应在 60 到 64 之间,以保持稳定的控制回路。

该CDCE421A支持一个差分LVDS时钟输出或一个差分LVPECL输出。所有器件设置均可通过专有的简单串行接口 (SSI) 进行编程。

该器件在 LVPECL 和 LVDS 输出的 3.3V 电源环境中工作,工作温度范围为 -40°C 至 +85°C。 该CDCE421A采用QFN-24 4mm×4mm封装。

特性

- 3.3 V单电源,用于LVPECL或LVDS工作

- 高性能时钟乘法器,将晶体振荡器电路与集成频率合成器相结合

- 低输出抖动:380 fs RMS(典型值)(10 kHz 至 20 MHz)

- 高频低相位噪声 (708MHz LVPECL):

- 载波的典型值为-109 kHz时为-109 dBc/Hz,10 MHz时为-146dBc/Hz

- 支持27.35 MHz至38.33 MHz的晶体或LVCMOS输入频率

- 输出频率范围为 10.9 MHz 至 766.7 MHz 和 875.2 MHz 至 1175 MHz

- 低压差分信号 (LVDS) 输出,100

差分片外终端,10.9 MHz 至 400 MHz 频率范围

差分片外终端,10.9 MHz 至 400 MHz 频率范围 - 差分低压正发射极耦合逻辑 (LVPECL) 输出,频率范围为 10.9 MHz 至 1.175 GHz

- 两个完全集成的压控振荡器 (VCO) 支持宽输出频率范围

- 完全集成的可编程环路滤波器

- 3.3 V 时的典型功耗:

- LVDS 模式下为 274 mW

- LVPECL 模式下为 250 mW

- 芯片使能控制引脚

- 简单的串行接口允许在制造后进行编程

- 集成片内非易失性存储器 (EEPROM) 存储设置,无需施加高压

- 采用 4 mm × 4 mm QFN-24 封装

- ESD 保护超过 2 kV (HBM)

- 工业温度范围:-40°C 至 +85°C

- 应用

- 低成本、高频晶体振荡器

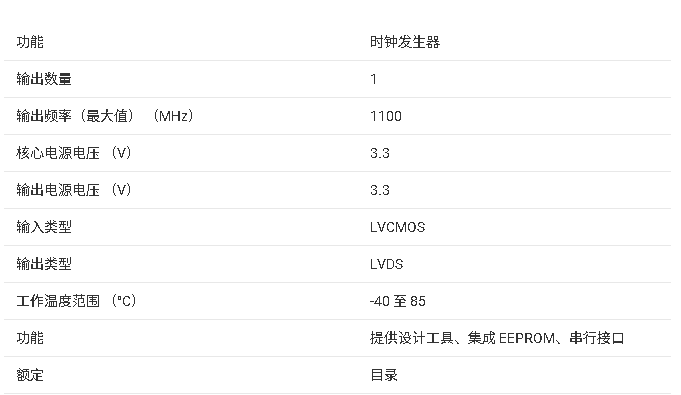

参数

1. 产品概述

CDCE421A是德州仪器(TI)推出的高性能、低相位噪声时钟发生器芯片,主要特点包括:

- 集成设计:内置晶体振荡器电路和频率合成器,支持27.35 MHz至38.33 MHz的晶体或LVCMOS输入频率。

- 低抖动性能:典型RMS抖动为380 fs(10 kHz至20 MHz带宽)。

- 输出类型:支持LVDS(10.9 MHz至400 MHz)和LVPECL(10.9 MHz至1.175 GHz)两种差分输出。

- 双VCO架构:集成两个电压控制振荡器(VCO),覆盖1.750 GHz至2.350 GHz频率范围。

- 可编程性:通过串行接口(SSI)配置分频器、预分频器等参数,并内置EEPROM存储设置。

2. 关键特性

- 电源:单3.3 V供电,工业级温度范围(-40°C至+85°C)。

- 功耗:LVDS模式典型274 mW,LVPECL模式250 mW。

- 封装:4 mm × 4 mm QFN-24封装,ESD保护超过2 kV(HBM)。

3. 应用场景

- 低成本高频晶体振荡器替代方案

- 需要低抖动时钟的通信、数据中心设备

- 工业自动化及测试测量仪器

4. 功能模块

- 晶体振荡器:提供基准频率输入。

- PLL合成器:通过反馈分频器(12/16/20/32)和输出分频器(1/2/4/8/16/32)生成目标频率。

- 控制接口:单线串行编程接口(SDATA),支持实时配置和EEPROM存储。

5. 配置示例

- 频率计算:通过公式 fXTAL=输出分频×fOUT反馈分频fXTAL =反馈分频输出分频**×fOUT** 确定所需晶体频率。

- 寄存器设置:6个控制字(Word0-Word5)配置VCO选择、分频参数、电荷泵电流等。

6. 电气特性

- LVDS输出:差分电压247-454 mV,上升/下降时间≤230 ps。

- LVPECL输出:摆幅≥600 mV,相位噪声典型值-146 dBc/Hz(10 MHz偏移)。

7. 设计注意事项

- 启动时间:受电源斜坡、VCO校准和PLL锁定时间影响,需预留约1 ms。

- 布局建议:裸露焊盘需焊接至PCB以优化散热和机械稳定性。

8. 版本差异

- 相比前代CDCE421,CDCE421A改进了启动电路和LVDS缓冲器性能,需注意寄存器配置差异(如Word0 Bit10必须置1)。

附录

- 提供测试配置图(LVDS/LVPECL的AC/DC端接方案)及相位噪声曲线(如708 MHz输出时典型值-109 dBc/Hz @10 kHz)。

- 封装选项包括卷带(RGE)和小卷带(ARGET)形式,符合RoHS标准。

该文档完整覆盖了芯片功能、配置方法、电气规格及应用设计指南,适用于硬件工程师进行时钟系统设计参考。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深度剖析CDCE62002:高性能时钟发生器的卓越之选2026-02-09 516

-

CDCE421A:高性能低相位噪声时钟发生器的深度解析2026-02-05 397

-

CDCE62005 时钟发生器芯片技术文档总结2025-09-18 972

-

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结2025-09-17 951

-

CDCE6214 超低功耗时钟发生器技术文档总结2025-09-12 930

-

CDCE6214Q1TM 超低功耗时钟发生器技术文档总结2025-09-11 859

-

CDCE421A全集成、宽范围、低抖动晶体振荡器时钟发生器数据表2024-08-23 469

-

CDCE(L)913低功耗LVCMOS时钟发生器数据表2024-08-22 427

全部0条评论

快来发表一下你的评论吧 !