简单认识CoWoP封装技术

描述

以下文章来源于逍遥设计自动化,作者逍遥科技

CoWoP技术基础介绍

半导体行业正面临传统封装方法的性能极限,特别是在满足AI计算需求的爆炸性增长方面。CoWoP(芯片晶圆平台印刷线路板封装)技术的出现,代表了系统级集成方法的根本性转变。这种创新方法通过消除传统中间层结构,为下一代计算系统创造了更高效、更经济的解决方案。

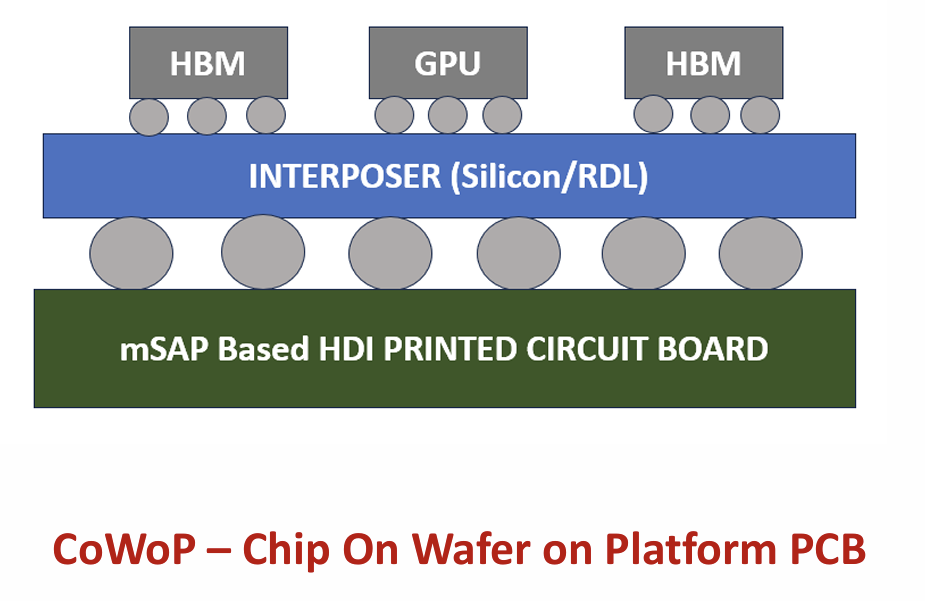

图1:CoWoP的基本架构,显示HBM、GPU和HBM芯片安装在硅Interposer上,直接连接到基于mSAP的HDI印刷线路板。

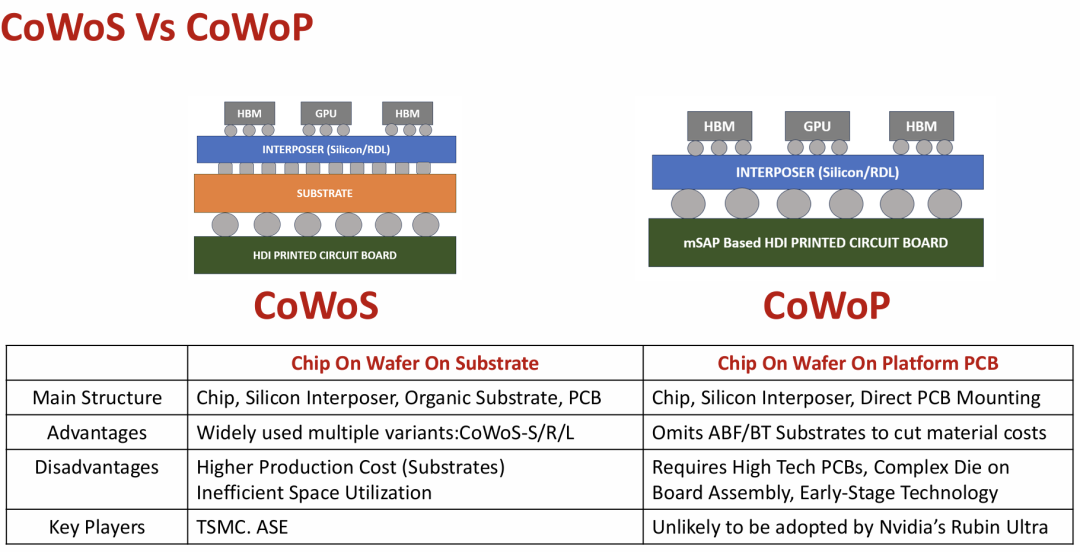

CoWoP代表"芯片晶圆平台PCB",这是一种封装方法,芯片通过硅Interposer以倒装芯片方式直接键合到高密度印刷线路板上。这种方法消除了对传统有机基板(如ABF或BT板)和常规BGA焊球的需求,在芯片和PCB之间创造了更集成的连接。该技术将硅Interposer的高性能互连优势与PCB的成本效益相结合,定位为CoWoS(芯片晶圆基板封装)系统级封装技术的自然演进。

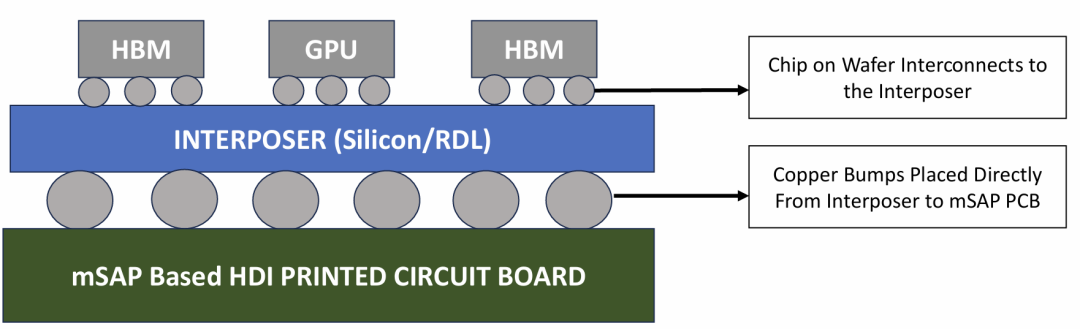

图2:CoWoP结构,说明芯片晶圆如何与Interposer互连,以及铜凸点如何从Interposer直接放置到mSAP PCB上。

CoWoP的技术理念

CoWoP的核心理念体现了一种激进的技术飞跃,从根本上挑战了传统封装智慧。与增加复杂性层面不同,CoWoP采用减法方法,移除所有不必要的中间组件。该技术直接消除了昂贵且厚重的中间封装基板,用技术密集型的"平台PCB"取而代之,允许芯片和Interposer组件直接安装到这个增强的主板上。

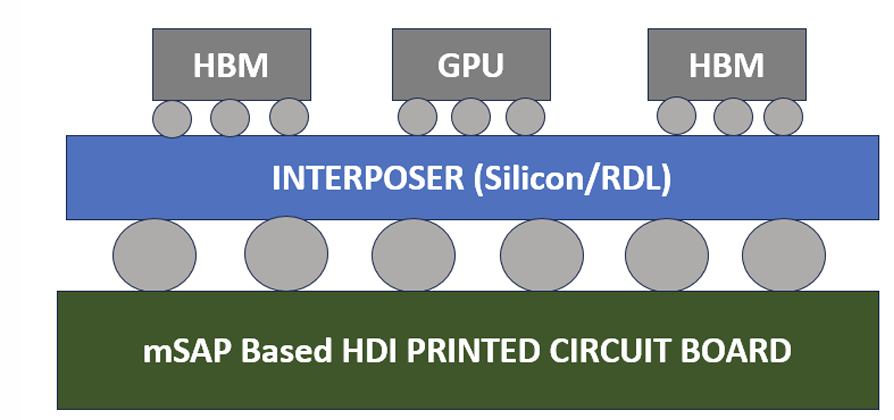

图3:简化的CoWoP架构,演示了封装基板的消除,仅显示基本组件,HBM-GPU-HBM排列在硅Interposer上,直接连接到基于mSAP的HDI印刷线路板。

这个看似简单的减法代表了巨大的技术进步。"CoWoP = CoWoS - 封装基板"这个等式捕捉了这种创新的本质,但其影响远不止于此。主板PCB本身现在必须具备以前由封装基板提供的高精度布线能力。与传统CoWoS技术相比,三个关键组件完全消失:封装基板、BGA焊球和相关的互连复杂性。带有硅Interposer的裸芯片模块现在直接连接到服务器主板,创造了超高的集成效率。

结构组件和Assembly

理解CoWoP需要检查其分层结构,该结构通过精心设计的组件自下而上构建。基础由平台PCB组成,作为最终承载整个系统的通用服务器主板。这块板必须满足极高的制造标准,包括精确的线密度、平整度和公差要求,这些要求以前属于专业封装代工厂。

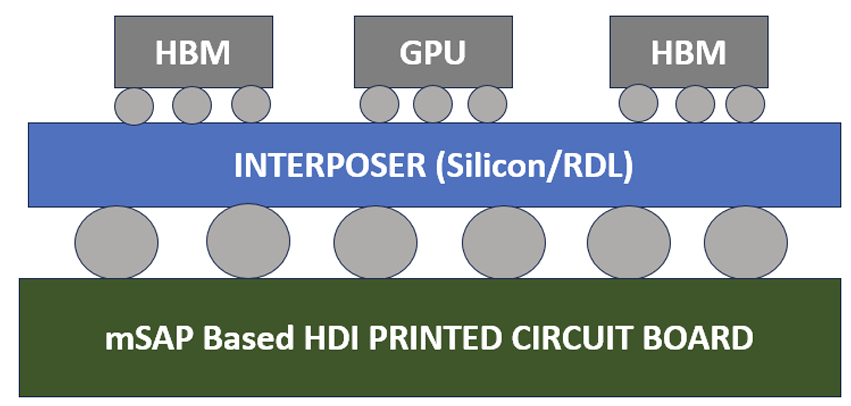

图4:完整的CoWoP结构分解,显示三个主要组件,芯片die(GPU核心和HBM)、作为适配板的硅Interposer,以及平台PCB基础。

平台上方是硅Interposer,这是一个高精度晶圆,功能类似于复杂的适配板。该组件使GPU和HBM模块等小芯片能够紧密放置,实现高速通信。Interposer处理管理数千个微小信号点并将其有效路由到下方PCB上较大连接点的关键任务。

顶层包含实际的计算元素:芯片die本身,包括GPU核心和相邻的高带宽存储器模块。这些组件代表驱动AI工作负载的核心计算单元,通过Interposer的直接集成创造了巨大的性能机会。

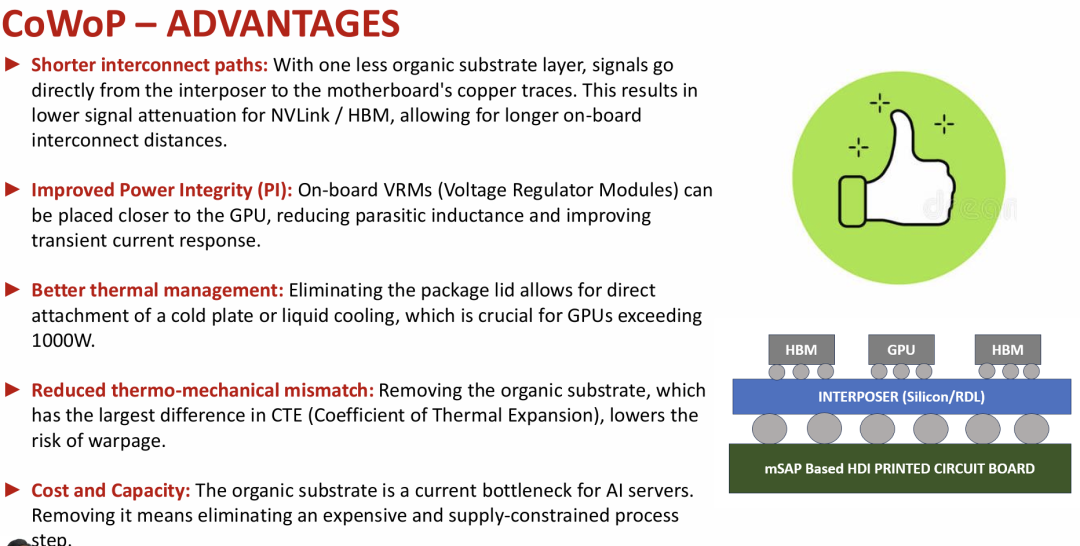

优势和性能收益

CoWoP在多个性能维度上提供显著优势,从根本上改变了高性能计算系统的方法。该技术通过消除一个有机基板层创造了更短的互连路径,允许信号直接从Interposer传输到主板的铜走线。这种直接连接降低了NVLink和HBM接口等关键连接的信号衰减,在不影响性能的情况下实现更长的板载互连距离。

图5:优势概览,显示CoWoP结构以及性能收益,包括改善的电源完整性、热管理和减少的热机械失配。

电源完整性改善代表了另一个重要优势。板载电压调节模块可以更靠近GPU放置,减少寄生电感并显著改善瞬态电流响应。随着GPU功耗超过1000瓦,这种接近性变得越来越重要,需要极其响应迅速的电源传输系统。

热管理收益来自消除封装盖,允许直接安装冷板或液冷解决方案。这种直接热接口对管理高性能AI加速器产生的热量至关重要。此外,移除有机基板消除了热膨胀系数差异最大的组件,显著降低了热循环过程中的翘曲风险。

成本和产能优势解决了当前行业瓶颈。有机基板代表昂贵、供应受限的工艺步骤,限制了AI服务器生产。消除这些组件移除了重要的成本中心,同时解决了目前限制行业增长的制造产能约束。

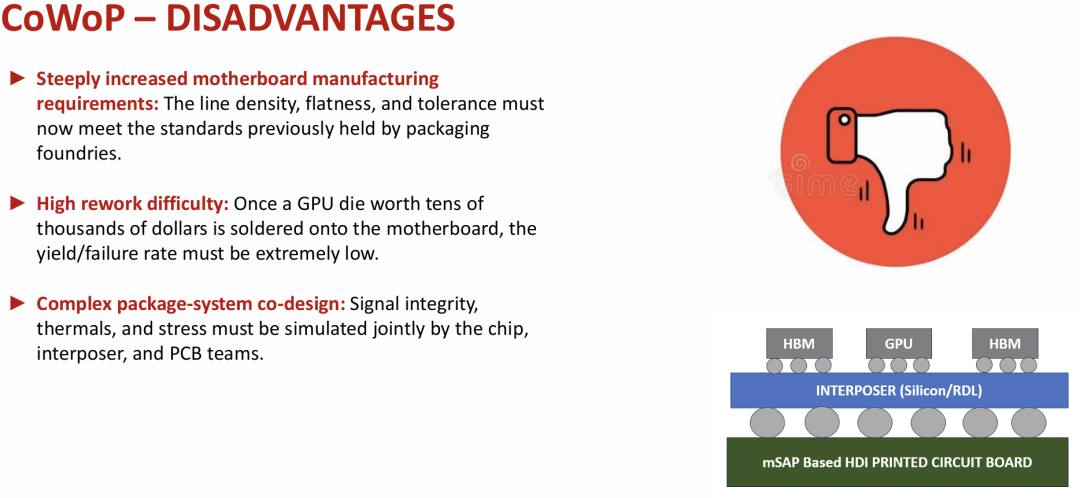

挑战和考虑因素

尽管有优势,CoWoP引入了必须仔细管理的重大技术挑战。主板的制造要求急剧增加,因为PCB制造现在必须达到以前专门为专业封装代工厂保留的标准。线密度、平整度和公差规格必须达到传统PCB制造商从未大规模尝试过的水平。

图6:主要缺点,包括增加的主板制造要求、高返工难度和复杂的封装系统协同设计需求。

返工难度呈现另一个重大挑战。一旦价值数万美元的GPU die直接焊接到主板上,良率和故障率必须保持极低水平。传统封装方法允许组件更换和返工,但CoWoP的直接集成使得这种维修几乎不可能,除非更换整个主板Assembly。

该技术还需要复杂的封装系统协同设计方法。信号完整性、热管理和机械应力必须由芯片设计团队、Interposer专家和PCB工程师联合仿真。这种协调水平需要传统上独立的工程学科之间超高程度的合作。

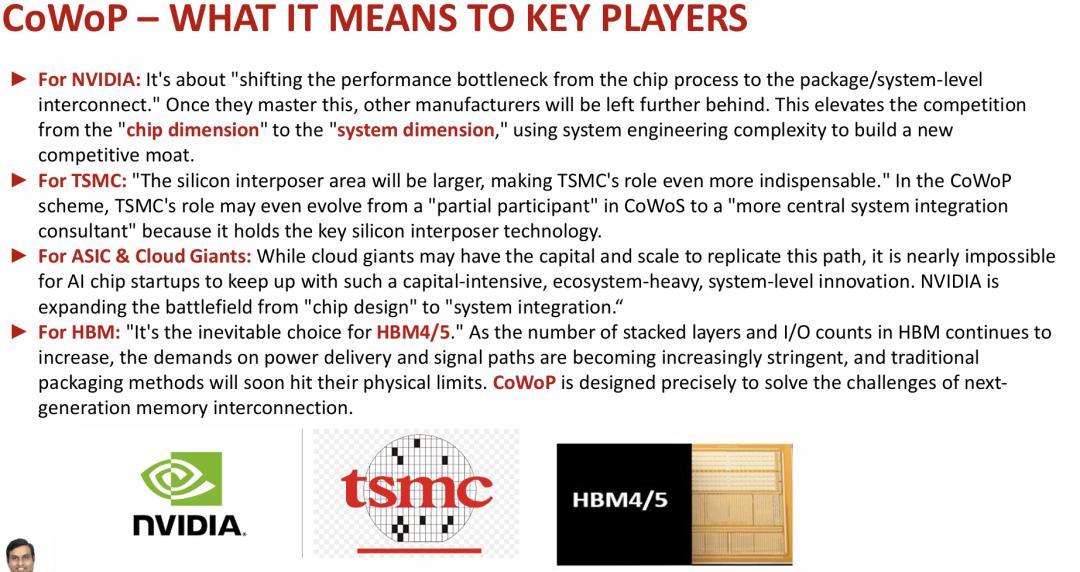

行业影响和战略意义

CoWoP不仅仅是技术进步,还从根本上重塑了整个半导体生态系统的竞争动态。对于NVIDIA来说,该技术将性能瓶颈从芯片处理转移到封装和系统级互连。掌握这种转变创造了巨大的竞争优势,将竞争从芯片级性能提升到系统级集成能力。

图7:行业影响,受CoWoP采用影响的关键参与者。

TSMC的角色在CoWoP实施下发生重大演变。硅Interposer区域变得更大更关键,使TSMC的参与更加不可或缺。公司的地位可能从CoWoS的部分参与者转变为中央系统集成顾问,考虑到控制关键硅Interposer技术。

对于存储器技术,CoWoP对HBM4和HBM5实施变得必不可少。随着堆叠层数和输入输出要求持续增加,传统封装方法接近物理极限。CoWoP专门解决下一代存储器互连挑战,使其对未来高带宽存储器实施几乎不可避免。

图8:CoWoS和CoWoP架构的直接比较,CoWoP中基板层的消除,同时保持上下相同的功能组件。

未来展望和技术演进

从更广阔的角度来看,CoWoP代表NVIDIA试图将服务器主板转变为GPU的最终封装层,有效定义整个AI计算硬件平台。这种策略超越了简单的芯片销售,转向定义包含芯片、封装和主板集成的完整系统级平台。

在这种努力中的成功将触发整个下游半导体供应链的价值重构和技术重组,影响封装公司、基板制造商、PCB制造商和服务器原始设计制造商。该技术代表了向超大规模计算能力迈进的必要步骤,在这种情况下,仅靠芯片制造工艺的进步无法满足AI计算能力的爆炸性增长需求。

行业在过渡期间可能会看到并行技术路线图,传统CoWoS与CoWoP开发并行继续。这种双重方法在新技术成熟期间提供安全网,确保产品迭代和市场供应在技术过渡期间保持稳定。

CoWoP最终代表了半导体行业对基本扩展挑战的响应。随着接近传统封装方法的极限,像CoWoP这样的系统级创新对于AI计算时代的持续性能提升变得必要。

-

简单认识NMOS管2023-11-13 5348

-

简单认识高压CMOS技术2025-04-22 1264

-

最近大火的CoWoP跟CoWoS、CoPoS有什么区别?2025-08-10 5659

-

AD09学习资料系列——画板子不在是难事之封装认识!2013-11-05 10433

-

微电子封装技术2013-12-24 6369

-

常见的元器件封装技术简单介绍2020-03-16 2892

-

认识其本质模拟SPI硬件SPI图片写入函数封装2021-08-03 1137

-

串行通讯简单认识2009-10-17 822

-

简单元件封装2015-12-23 366

-

关于对刷脸支付的简单理解和认识2020-12-28 2585

-

简单认识射频识别技术2024-01-08 2049

-

简单认识无源器件2024-01-12 1119

-

简单认识变压器2024-01-25 1441

-

CoWoP封装的概念、流程与优势2025-08-12 2243

-

CoWoP能否挑战CoWoS的霸主地位2025-09-03 2717

全部0条评论

快来发表一下你的评论吧 !