硅通孔电镀材料在先进封装中的应用

描述

文章来源:学习那些事

原文作者:前路漫漫

本文主要讲述硅通孔电镀材料。

硅通孔(TSV)技术借助硅晶圆内部的垂直金属通孔,达成芯片间的直接电互连。相较于传统引线键合等互连方案,TSV 技术的核心优势在于显著缩短互连路径(较引线键合缩短 60%~90%)与提升互连密度(最高可达 1500 I/O/mm²),因此能实现封装体的轻薄化(厚度可降至 50μm 以下)与高集成度,是三维(3D)集成封装领域不可或缺的关键技术。

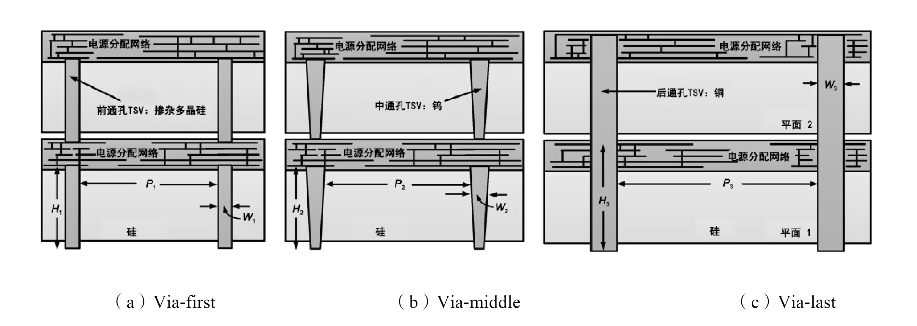

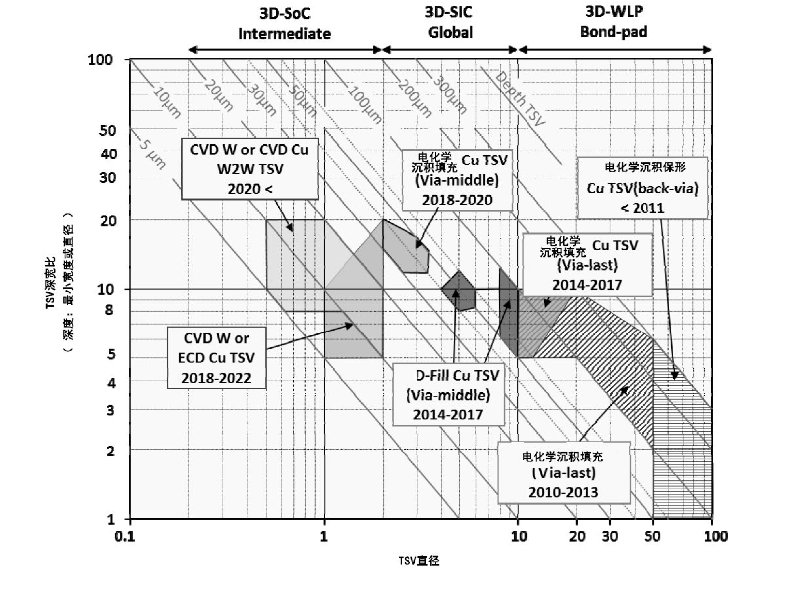

依据 TSV 制造工序在晶圆全流程工艺中的时序顺序,可将其划分为前通孔(Via-first)、中通孔(Via-middle)与后通孔(Via-last)三类技术(如图1所示)。其中,前通孔技术的 TSV 制备需在前道工序(FEOL,主要负责晶体管等核心器件制造)启动前完成,故通孔不会穿透后续形成的金属互连层;中通孔技术的 TSV 制造介于 FEOL 与后道工序(BEOL,侧重金属布线与封装前处理)之间,同样不会破坏金属互连层;后通孔技术的 TSV 形成于 BEOL 之后,因此通孔会完全穿透已成型的金属互连层,适配灵活度更高的芯片集成场景。

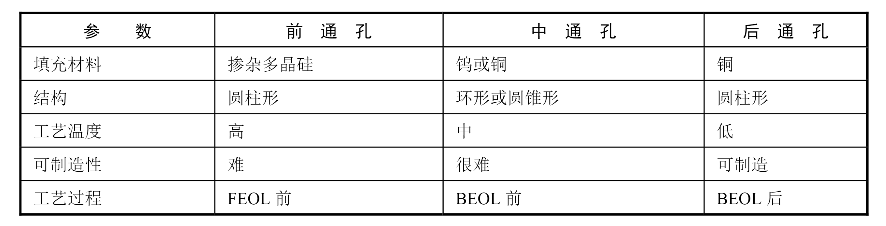

尽管前、中、后通孔技术的制造时序存在差异,但三者的核心工艺环节一致,均包含通孔刻蚀、通孔薄膜沉积、通孔填充、化学机械研磨(CMP)、超薄晶圆减薄等步骤,各工艺的性能指标对比如表 1 所示。TSV 的电互连功能需通过导电材料填充实现,而填充方式与材料的选择,主要取决于 TSV 的制造阶段与尺寸参数(如孔径、深宽比)(如图2所示)。目前主流的 TSV 填充方式分为两类:电镀与化学气相沉积(CVD)。通常而言,若 TSV 孔径较小(2μm 以下),液体电镀液难以渗透至微孔内部,易形成空洞或缝隙,因此需依赖 CVD 技术实现无缺陷填充,常用的 CVD 导电材料包括铜、钨、多晶硅等;而当前先进封装中应用的 TSV 孔径多在 5μm 以上,从工艺效率(电镀填充速率较 CVD 快 3~5 倍)与成本(电镀设备投入较 CVD 低 40% 左右)综合考量,电镀成为主流填充方式。

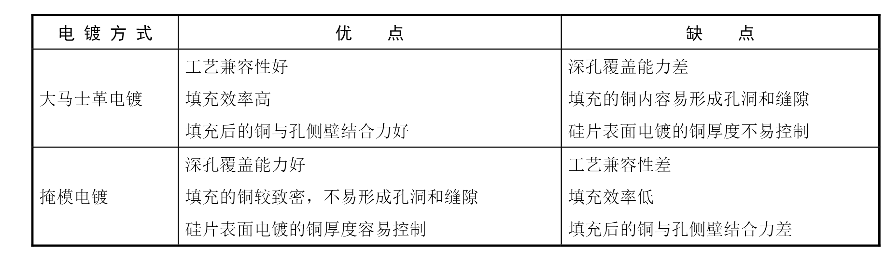

单质金属铜具备优异的电导率(59.6 S/m)与热导率(401 W/(m・K)),且电镀铜工艺具备多重优势:设备结构简单、采购成本较低,可在室温与常压环境下操作;在优化的工艺参数(如电流密度 1~3 A/dm²、pH 值 1.8~2.2)下,能在水溶液体系中形成均匀性偏差 < 5% 的铜沉积层;沉积速率可达 1~5 μm/h,适配产业化大批量生产需求;同时与传统 FEOL、BEOL 工艺兼容性良好,因此电镀铜被视为先进封装中 TSV 填充的最优方案。TSV 电镀铜工艺主要分为大马士革电镀(Damascene Electroplating)与掩模电镀(Through Mask Electroplating)两类。

大马士革电镀的工艺流程为:先在晶圆表面通过光刻工艺制作图形,形成具备特定深宽比(孔深与孔径的比值,通常为 5:1~20:1)的盲孔;随后沉积种子层(多为铜 - 钛复合层,厚度 50~100nm),且种子层覆盖图形表面与盲孔内壁;电镀过程中,盲孔内部与晶圆表面均会沉积金属铜;电镀结束后,需通过化学机械研磨(CMP)工艺去除晶圆表面多余的铜层,仅保留盲孔内的铜填充体。

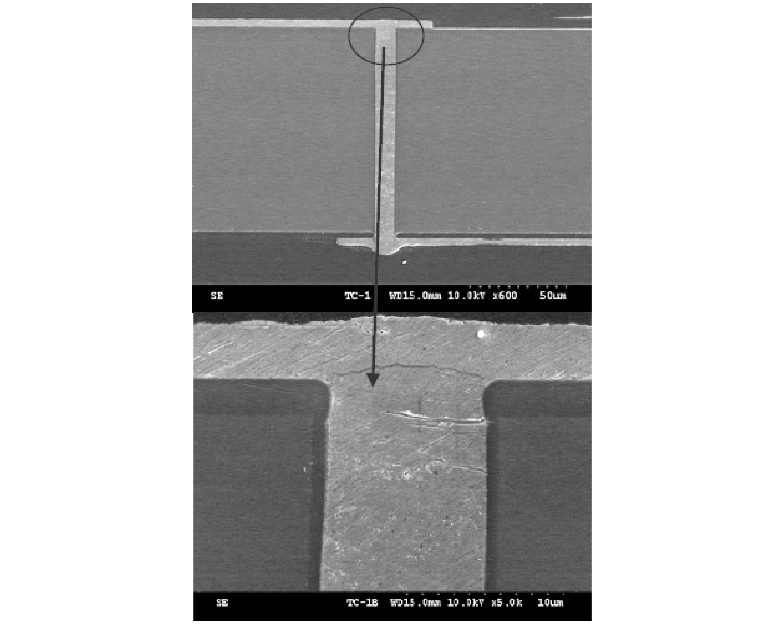

掩模电镀的流程则有所不同:先在晶圆表面沉积种子层,再通过光刻工艺制作图形,此时种子层仅在图形暴露区域可见;电镀过程中,金属铜仅在种子层暴露区域沉积;电镀完成后,需采用蚀刻工艺去除未电镀区域的种子层,避免残留金属引发短路。两类工艺的优缺点对比如表2所示。此外,需注意铜与硅的热膨胀系数差异显著 —— 常温下铜的热膨胀系数为 17.7 ppm/K,而硅仅为 2.5 ppm/K,当 TSV 孔径较大(>15μm)或密度较高(>100 个 /mm²)时,铜填充体与硅基体在温度循环过程中会产生显著热应力,可能导致 TSV 互连结构失效。如图 3所示,TSV 结构经 1000 次热循环(-40℃~125℃)后,其顶部再布线层已出现明显裂纹。

硅通孔电镀材料在先进封装中的应用

TSV 技术通过芯片垂直方向的互连缩短路径长度,从而降低信号传输延迟(可减少至 10ps 以下)、降低寄生电容与电感(电容可降至 0.1pF 以下),最终实现电子元器件与芯片间的低功耗(功耗降低 20%~30%)、高速通信(传输速率提升至 100Gbps 以上)与高带宽,为元器件三维集成提供核心支撑。

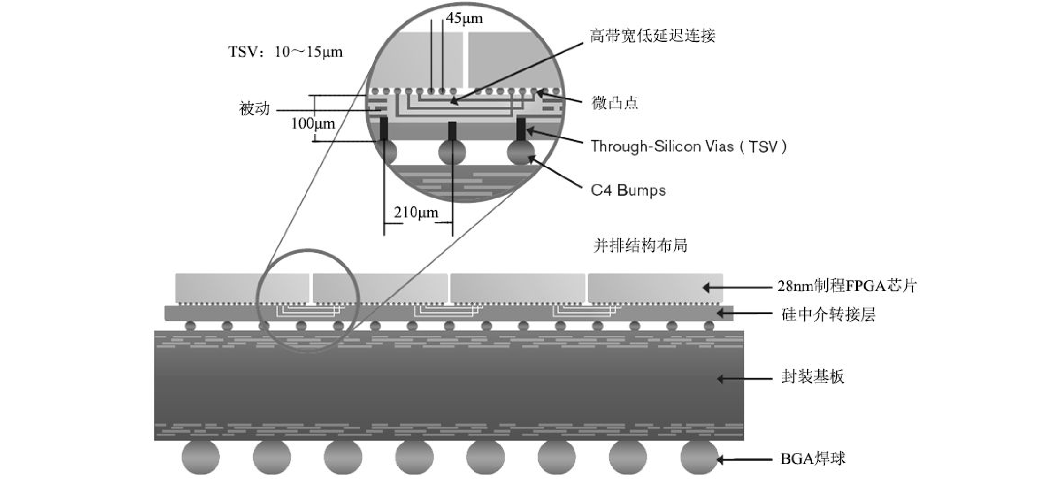

目前,基于 TSV 技术的三维集成已广泛应用于多个领域:存储器三维堆叠(如 3D NAND、DRAM 堆叠)、多芯片集成的硅中介转接层(Silicon Interposer)、射频(RF)模组、微机电系统(MEMS)及图像传感器(CIS)的 2.5D/3D 集成与组装。例如,赛灵思(Xilinx)Virtex 7 系列 FPGA 芯片与三星电子(Samsung Electronics)面向服务器领域的 RDIMM DDR4 SRAM 存储模块,均采用 TSV 技术实现高密度集成;如图 4 所示的 Xilinx Virtex-7 2000T FPGA 组装结构中,硅中介转接层的 TSV 孔径为 10~15μm,深宽比约为 8:1。

-

一种用于先进封装的圆台硅通孔的刻蚀方法2023-04-12 3131

-

硅通孔封装工艺流程与技术2023-05-08 5915

-

陶瓷基板电镀封孔/填孔工艺解析2023-06-05 4383

-

TSV硅通孔填充材料2025-04-14 3087

-

【转帖】影响PCB电镀填孔工艺的几个基本因素2018-10-23 3160

-

宁波材料所在先进气体传感材料与传感器关键技术方面取得进展2019-01-21 1862

-

硅通孔(TSV)电镀2021-01-09 3837

-

先进封装中硅通孔(TSV)铜互连电镀研究进展2023-09-06 2683

-

硅通孔(TVS)技术相关知识 绝缘层在先进封装中的应用2023-11-20 1704

-

面向先进封装的电镀技术新进展2024-04-02 2913

-

晶圆微凸点技术在先进封装中的应用2024-10-16 3524

-

Chiplet在先进封装中的重要性2024-12-10 1534

-

先进封装中的TSV/硅通孔技术介绍2024-12-17 4356

-

通孔电镀填孔工艺研究与优化2025-04-18 2717

-

先进封装的散热材料有哪些?2026-02-27 338

全部0条评论

快来发表一下你的评论吧 !