ADC3910 系列 10 位低延迟低功耗 ADC 技术文档总结

描述

ADC3910Dx 和 ADC3910Sx 是系列超低功耗 10 位 125MSPS 高速单通道和双通道模数转换器。高速控制环路受益于仅 1 个时钟周期的短延迟。ADC在125Msps时仅消耗92mW,功耗随较低采样率而变化。

该器件采用DDR、HDDR、SDR或串行CMOS接口输出+1.8V至+3.3V的数据,以满足各种接收器要求。该器件使用具有可编程高阈值和低阈值、迟滞和事件计数器的数字比较器,通过每个通道的事件触发中断来实现模拟监控功能。该器件是引脚兼容的ADC系列,具有8位和10位分辨率以及不同的速度等级。该器件采用 32 引脚 VQFN 封装,支持 -40 至 +105°C 的工业温度范围。

*附件:adc3910d025.pdf

特性

- 采样率高达 125MSPS

- 延迟:1 个时钟周期

- 低功耗(2 通道):

- 125MSPS 时为 92mW

- 25MSPS 时为 59mW

- PD 模式下为 4mW

- 小尺寸:32-VQFN (4mm x 4mm)

- 单通道或双通道ADC

- 双数字比较器

- 参考:内部或外部

- 无遗漏代码,±1 LSB INL

- 缓冲、差分或单端输入

- 输入带宽:150MHz (3dB)

- 1.8V单电源

- 可选的 3.3VIO 功能

- 工业温度范围:-40 至 105°C

- 片上数字滤波器(可选)

- 抽取 2、4、8、16

- 并行(SDR、DDR)和串行CMOS接口

- 频谱性能 (fIN = 5MHz):

- 信噪比:61dBFS

- SFDR:65dBc

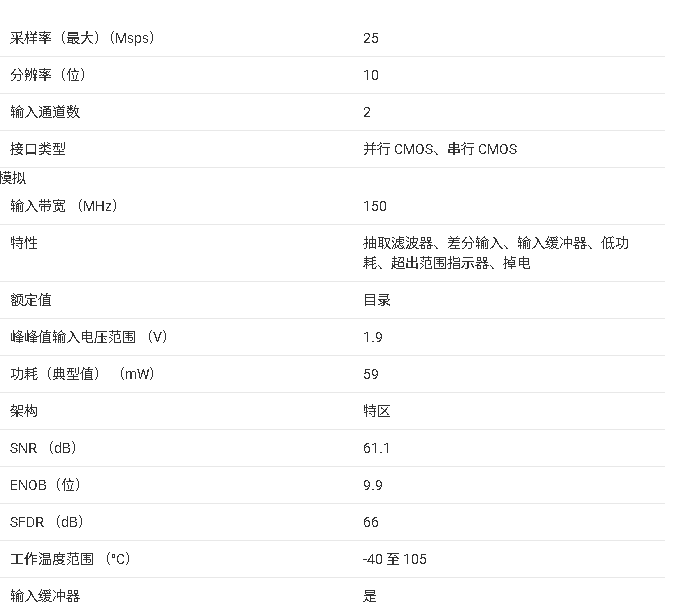

参数

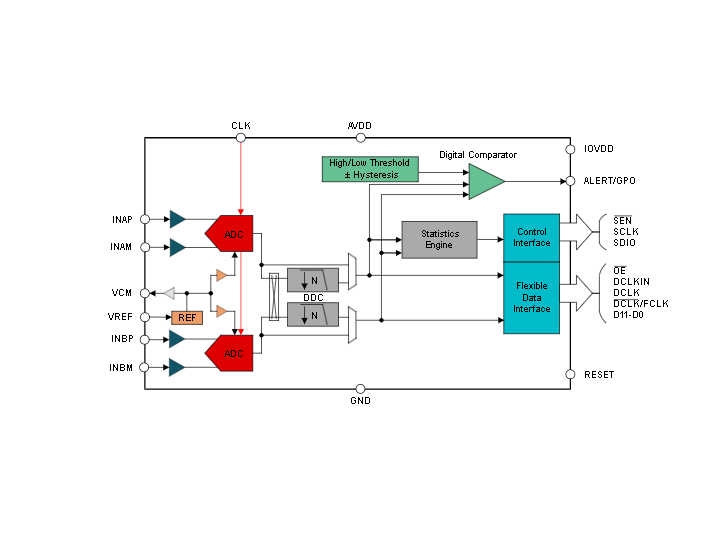

方框图

一、核心特性与器件差异

1. 共性核心特性

- 高速低延迟采样 :

- 采样率覆盖 25MSPS(ADC3910D025/S025)、65MSPS(ADC3910D065/S065)、125MSPS(ADC3910D125/S125),低延迟模式下 数据输出仅需 1 个时钟周期 ,适配实时控制场景;

- 输入带宽(-3dB)达 150MHz,支持差分 / 单端输入,差分输入满量程(FSR)1.9Vpp,单端输入 0.95Vpp,输入共模电压需匹配 VCM 引脚 1.25V 输出。

- 高集成数字功能 :

- 数字下变频器(DDC) :支持 2/4/8/16 倍实抽取,输出数据率随抽取比降低(如 125MSPS 抽取 16 倍后输出 7.8125MSPS),阻带抑制≥70dB,可放松外部抗混叠滤波器要求;

- 双数字比较器 :每通道独立可编程高 / 低阈值与滞回,支持电平比较(超阈值触发)与斜率比较(相邻采样差值触发),通过 ALERT 引脚输出中断,适配信号超限监测;

- 统计引擎 :实时统计指定窗口内采样数据(最小 / 最大值、样本计数、求和、平方和),窗口大小可配置(256~256×2¹⁶样本),支持连续 / 单次采集,适配信号特征分析。

- 灵活电源与接口 :

- 单电源供电:AVDD(模拟 1.8V)与 IOVDD(数字 1.8V~3.3V),电源电流随采样率降低而减小(双路 25MSPS 时 AVDD 电流 29mA,125MSPS 时 39mA),掉电模式功耗仅 4mW;

- 数字接口:支持并行(DDR/HDDR/SDR)与串行 CMOS 输出,数据格式可选二进制补码(默认)或偏移二进制,输出 lanes 可配置(2/4/8 lane),适配不同 FPGA/MCU 接口需求;

- 参考源:内置 1.2V 参考(温度漂移典型 102ppm/°C),支持外部 1.2V 参考输入(需并联 10μF+0.1μF 去耦电容),外部参考时增益误差更低(±0.2% FSR)。

- 可靠性能指标 :

- DC 精度:10 位无失码,微分非线性(DNL)典型 ±0.4LSB(最大 2.1LSB),积分非线性(INL)典型 ±0.5LSB(最大 2.1LSB),增益误差(外部参考)±0.2% FSR,偏移误差典型 ±1LSB;

- AC 性能:5MHz 输入时,信噪比(SNR)典型 60.6dBFS、无杂散动态范围(SFDR)典型 64dBc、总谐波失真(THD)典型 - 63dBc,通道隔离串扰典型 90dBc,满足中高频信号采样需求;

- ESD 防护:全引脚人体放电模型(HBM)±1000V、带电器件模型(CDM)±500V,符合 JEDEC JESD22 标准,工业环境可靠性高。

2. 器件差异(双路 Dx vs 单路 Sx)

| 参数 | 双路 ADC3910Dx(D025/D065/D125) | 单路 ADC3910Sx(S025/S065/S125) |

|---|---|---|

| 通道数 | 2 路同步采样 | 1 路采样(通道 B 引脚悬空) |

| 模拟电源电流(AVDD) | 25MSPS 时 29mA,125MSPS 时 39mA | 25MSPS 时 19mA,125MSPS 时 25mA |

| 数字电源电流(IOVDD) | 25MSPS 时 9mA,125MSPS 时 18.5mA | 25MSPS 时 8mA,125MSPS 时 32mA |

| 功耗(典型值) | 125MSPS 时 97mW,25MSPS 时 59mW | 125MSPS 时 80mW,25MSPS 时 41mW |

| 特殊模式 | 支持交织模式(2 路交织采样,采样率翻倍至 2×CLK) | 不支持交织模式 |

| 引脚功能 | INBP/INBM 为通道 B 输入 | INBP/INBM 为无连接(NC) |

二、封装与引脚功能

1. 封装规格

全系采用 4mm×4mm 32 引脚 VQFN(RSM 封装) ,底部裸露热焊盘(需与 PCB 接地焊盘连接以优化散热),热阻参数:

- 结到环境(RθJA)38.1°C/W,结到板(RθJB)17.9°C/W,结到壳底(RθJC (bot))7.8°C/W,适配高密度 PCB 布局,确保高功率下的散热可靠性。

2. 关键引脚分类与功能

| 引脚类别 | 关键引脚示例 | 类型 | 核心功能 |

|---|---|---|---|

| 模拟输入 | AINAP/AINAM(通道 A)、INBP/INBM(通道 B) | 模拟输入 | 差分 / 单端模拟输入,差分模式下 AINAP/AINBM 为同相端,AINAM/INBM 为反相端;单端模式需将负端接 VCM |

| 电源与地 | AVDD、IOVDD、GND、REFM | 电源输入 | AVDD(1.8V 模拟电源,供电 ADC 核心与输入缓冲)、IOVDD(1.8V~3.3V 数字电源,供电接口与数字功能);REFM 为参考地,需短接至 GND |

| 参考与共模 | VREF、VCM | 模拟 I/O | VREF:内部 1.2V 参考输出 / 外部 1.2V 参考输入(外部参考需并联 10μF+0.1μF 去耦);VCM:共模电压输出(1.25V),用于设置输入共模电压 |

| 时钟与同步 | CLK、SMPL_SYNC | 数字输入 | CLK 为采样时钟(单端,5MHz~125MHz),需低抖动(典型 500fs RMS)以保证 SNR;SMPL_SYNC 用于多器件同步或滤波器复位 |

| 数字接口 | D0~D11、DCLK、DCLK/FCLK | 数字输出 | D0~D11 为数据输出(并行模式),DCLK 为数据时钟(DDR 模式下最高 250MHz),DCLK/FCLK 可配置为帧时钟,需外接匹配电阻 |

| 配置与控制 | SEN、SCLK、SDIO、RESET、OEN/PD | 数字 I/O | SPI 配置接口(SEN 低使能,SCLK 时钟,SDIO 双向数据)、复位(RESET 高有效)、输出使能 / 掉电(OEN/PD,可通过 SPI 配置功能) |

| 中断与状态 | ALERT | 数字输出 | 比较器 / 统计引擎中断输出,可配置为推挽 / 开漏模式,默认监测 ADC 过范围(OVR)事件 |

三、电气规格与工作条件

1. 电源要求

| 电源类型 | 电压范围 | 典型值 | 备注 |

|---|---|---|---|

| AVDD(模拟) | 1.7V~1.9V | 1.8V | 需就近并联 10μF(X7R 陶瓷)+0.1μF(陶瓷)电容去耦,模拟地与数字地单点连接,避免噪声耦合 |

| IOVDD(数字) | 1.7V | 1.8V/3.3V | 独立去耦,与 AVDD 隔离布线,确保数字接口信号完整性 |

| 参考源电压 | 内部 1.2V;外部 1.2V(±1.67%) | 1.2V | 外部参考推荐 TI REF7040(2ppm/°C 温漂),VREF 引脚需并联 10μF+0.1μF 电容 |

2. 关键电气参数(典型值,TA=25°C,AVDD=1.8V,IOVDD=1.8V,内部参考)

| 参数 | 规格范围 | 典型值(125MSPS) | 单位 |

|---|---|---|---|

| 差分输入满量程(FSR) | 1.9Vpp | 1.9 | Vpp |

| 输入偏置电流 | - | 0.1 | nA |

| 孔径抖动(RMS) | - | 500 | fs |

| LVDS 差分输出电压 | 200mV~500mV | 350 | mV |

| 掉电电流(AVDD) | - | 2 | mA |

| SNR(fIN=5MHz) | 57dBFS~60.6dBFS | 60.6 | dBFS |

| SFDR(fIN=5MHz) | 57dBc~64dBc | 64 | dBc |

四、核心功能与工作模式

1. 模拟前端与采样流程

- 信号路径 :差分 / 单端输入→输入缓冲→ADC 采样→数字信号处理(DDC / 比较器 / 统计引擎)→并行 / 串行 CMOS 输出;

- 交织模式(仅双路 Dx) :两通道 180° 相位交织采样,采样率翻倍(如 CLK=62.5MHz 时输出 125MSPS),需通过寄存器(0x84)配置增益 / 偏移校准,抵消通道失配;

- 输入配置 :差分模式下输入信号共模电压需匹配 VCM(1.25V±50mV),AC 耦合时需通过电阻网络拉至 VCM;单端模式需将负端接 VCM,此时 SNR 降低 3dB。

2. 数字功能与接口配置

- 数字下变频器(DDC) :

- 通过寄存器(0x200)配置抽取比,抽取后输出带宽随抽取比降低(如抽取 4 倍时带宽 = 0.8× 采样率 /(4×2)),125MSPS 抽取 16 倍后带宽 3.125MHz;

- NCO(数控振荡器)频率可配置,支持信号下变频至基带,输出 I/Q 复数数据,减少后端处理器算力消耗。

- 数字比较器 :

- 阈值配置:通过寄存器(0xC8~0xD3)设置高阈值(COMP_THRESHOLD_HI)、低阈值(COMP_THRESHOLD_LO)与滞回(COMP_HYSTERESIS),滞回默认 0,斜率比较时需置 0;

- 触发模式:事件触发(单次超阈值即触发 ALERT)或窗口触发(指定窗口内超阈值次数达阈值触发),窗口大小通过寄存器(0x1EA)配置。

- 统计引擎 :

- 统计项:样本计数(超阈值样本数)、极值(最小 / 最大值)、求和、平方和(用于功率计算),支持存储当前窗口(N)及前 3 个窗口(N-1~N-3)数据;

- 窗口配置:通过寄存器(0x1A0

0x1A3)设置窗口大小(256256×2¹⁶样本),支持连续采集或单次采集(1SHOT_CHx 寄存器)。

- 数字接口模式 :

- 并行模式 :支持 DDR(双沿采样,125MSPS 时 DCLK=250MHz)、HDDR(通道 A/B 分 lane 输出)、SDR(单沿采样,需双倍 DCLK 频率);

- 串行模式 :支持 2/4/8/16 倍串行化,减少输出 lane 数(如 125MSPS 8 倍串行化后用 2 lane 输出),适配引脚受限场景;

- 数据格式:二进制补码(默认)或偏移二进制,通过寄存器(0x30A)配置,输出位宽可配置为 8/10/12/16 位。

3. 低功耗与复位模式

- 分级掉电 :

- 全局掉电:通过 OEN/PD 引脚(高有效)或寄存器(0x97)触发,掉电后 AVDD 电流典型 2mA,唤醒时间(内部参考)30μs;

- 模块掉电:可单独关闭通道 A/B、参考源、DLL 等模块(寄存器 0x8C),如关闭通道 B 可降低 12mA AVDD 电流。

- 复位机制 :

- 硬件复位:RESET 引脚高有效,复位后寄存器恢复默认值,需等待 200000 个 CLK 周期后配置;

- 软件复位:通过寄存器(0x00)RESET 位触发,自清除,无需外部引脚操作。

五、寄存器配置

1. 核心寄存器功能

- 配置寄存器(基础功能) :

- 0x00(RESET):软件复位,置 1 后自动清 0,复位所有寄存器;

- 0x84(INTERLEAVE):双路器件交织模式使能(bit2=1),仅 Dx 系列支持;

- 0x98(INTERFACE_CFG_1):接口模式配置,HDDR 使能(bit5)、SDR 使能(bit4)、ALERT 引脚驱动强度(bit3~0);

- 0x30B(DEV_CFG_4):参考源选择(bit6=1 为外部参考)、单端输入使能(bit5=1)、分辨率配置(bit0=1 为 8 位,默认 10 位)。

- 数字功能寄存器 :

- 0x200(DDC_CFG_1):DDC 抽取比配置(bit2

0)、通道数据选择(bit53); - 0xC8

0xD3(COMP 系列):比较器高 / 低阈值、滞回、斜率比较使能(bit54); - 0x1A4(STATS_ENABLE):统计引擎使能(bit5 = 通道 B,bit4 = 通道 A)、单次采集使能(bit1~0);

- 0x1B4~0x1ED(ALERT 系列):ALERT 触发源选择、极性反转、窗口阈值配置。

- 0x200(DDC_CFG_1):DDC 抽取比配置(bit2

2. SPI 配置流程

- 写操作 :SEN 拉低使能→SCLK 上升沿 latch 16 位数据(bit15=0 为写,bit14~0 为地址 + 数据)→SEN 拉高完成;

- 读操作 :SEN 拉低→SCLK 上升沿 latch 16 位读命令(bit15=1)→SEN 拉高前读取 SDIO 输出数据;

- 初始化流程 :上电→AVDD 稳定(2ms)→硬件复位→等待 200000 CLK 周期→配置参考源 / 接口 / 数字功能。

六、应用与设计建议

1. 典型应用场景

- 激光雷达(LiDAR) :125MSPS 采样率 + 150MHz 带宽适配高速激光信号采集,DDC 抽取功能降低后端数据处理压力;

- 低延迟控制环路 :1 时钟周期延迟 + 97mW 低功耗,适配电机控制、工业伺服等实时响应场景;

- 无线电接收机 :双路同步采样 + 高 SFDR(64dBc),支持 I/Q 信号同步采集,简化接收机架构。

2. 设计建议

- 电源与去耦 :

- AVDD 与 IOVDD 独立供电,避免数字噪声耦合至模拟端,AVDD 推荐用 LDO(如 TPS7A4701)二次稳压,降低开关噪声;

- VREF 引脚并联 10μF X5R 陶瓷电容 + 0.1μF 陶瓷电容,距离引脚<2mm,REFM 需短接至 GND,减少参考噪声。

- PCB 布局 :

- 划分模拟区(AINx、VREF、VCM)与数字区(D0~D11、DCLK),模拟地与数字地仅在热焊盘单点连接;

- 模拟输入布线:差分对长度匹配 ±0.5mm,阻抗控制 50Ω,远离数字信号线;CLK 时钟线短路径布线,串联 50Ω 匹配电阻;

- 热焊盘设计:裸露热焊盘需与 PCB 接地铜皮充分焊接,通过过孔连接至内层地,优化散热。

- 输入保护 :

- 模拟输入串联 10Ω 限流电阻 + 22pF 滤波电容,防止浪涌电流损坏输入缓冲;

- 共模匹配:AC 耦合时,通过 1kΩ 电阻网络将输入共模电压拉至 VCM(1.25V),避免通道失配。

七、订购与环境信息

1. 订购型号参数

| 订购型号 | 通道数 | 采样率 | 封装 | 温度范围 | RoHS 合规 | 包装规格 |

|---|---|---|---|---|---|---|

| ADC3910D025IRSMR | 2 | 25MSPS | 32 引脚 VQFN | -40°C~+105°C | 是 | 3000 颗 / 大卷带 |

| ADC3910D065IRSMR | 2 | 65MSPS | 32 引脚 VQFN | -40°C~+105°C | 是 | 3000 颗 / 大卷带 |

| ADC3910D125IRSMR | 2 | 125MSPS | 32 引脚 VQFN | -40°C~+105°C | 是 | 3000 颗 / 大卷带 |

| ADC3910S025IRSMR | 1 | 25MSPS | 32 引脚 VQFN | -40°C~+105°C | 是 | 3000 颗 / 大卷带 |

| ADC3910S125IRSMR | 1 | 125MSPS | 32 引脚 VQFN | -40°C~+105°C | 是 | 3000 颗 / 大卷带 |

2. 可靠性与防护

- ESD 防护 :全引脚 HBM±1000V、CDM±500V,符合 JEDEC JESD22 标准,焊接时需遵循 ESD 防护流程;

- 质量保证 :量产型号通过温度循环(-40°C~+105°C)、湿度偏压(85°C/85% RH)测试,MTBF(平均无故障时间)达 10⁶小时以上,适合长期工业应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC3683 双通道、18位、65MSPS、低噪声、超低功耗、低延迟ADC技术手册2025-11-01 1257

-

ADC3563 单通道、16位、65MSPS、低噪声、超低功耗、低延迟ADC技术手册2025-10-31 924

-

ADC3561/3562/3563 技术文档总结2025-10-30 1000

-

ADC354x 系列技术文档总结2025-10-29 1243

-

ADC3683-SP 技术文档总结2025-10-27 911

-

ADC3910D065 10 位高速低功耗 ADC 技术文档总结2025-10-24 1239

-

德州仪器ADC3910系列:高性能低功耗10位125MSPS ADC技术解析2025-09-05 1552

全部0条评论

快来发表一下你的评论吧 !