Chiplet与异构集成的先进基板技术

描述

以下文章来源于逍遥设计自动化,作者逍遥科技

01现代半导体封装演进基础

半导体产业正处在传统封装边界逐步消解的转型节点,新的集成范式正在涌现。理解从分立元件到复杂异构集成的发展过程,需要审视半导体、封装和载板基板之间的基本关系在过去十五年中的变化。

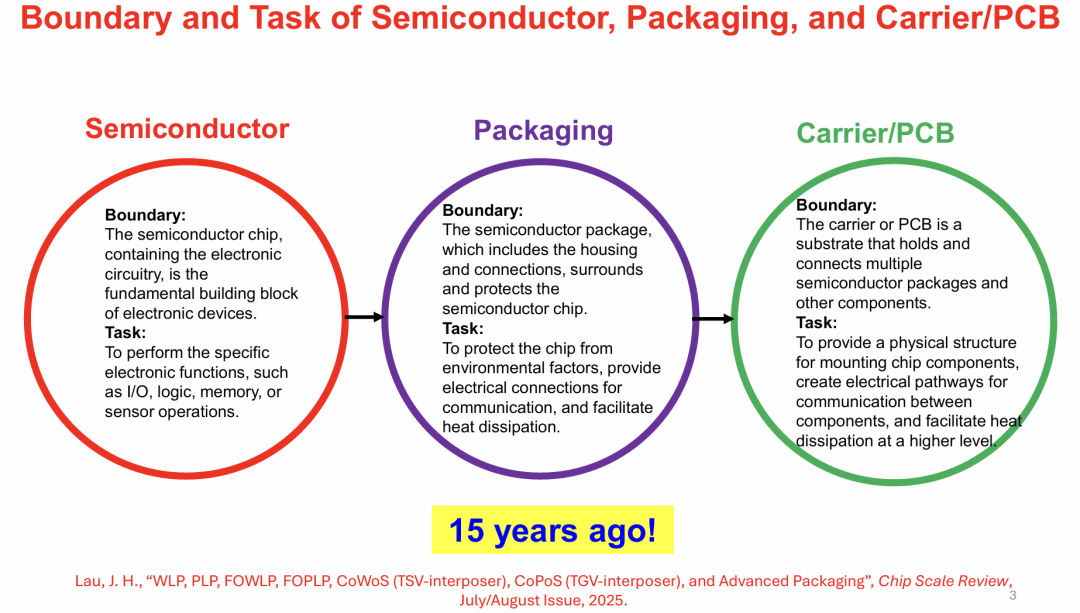

传统上,半导体产业在明确界定的边界内运作,每个组件都承担不同的功能。半导体芯片包含电子线路,执行输入/输出操作、逻辑处理、存储或传感器操作等特定功能。封装层,包括外壳和连接器,围绕并保护芯片,同时提供电气连接和散热功能。载板基板或印刷线路板为元件安装提供物理结构,并在元件之间建立电气通路。

图1:十五年前半导体、封装和载板层之间的传统功能分离,显示各层的明确边界和不同职责

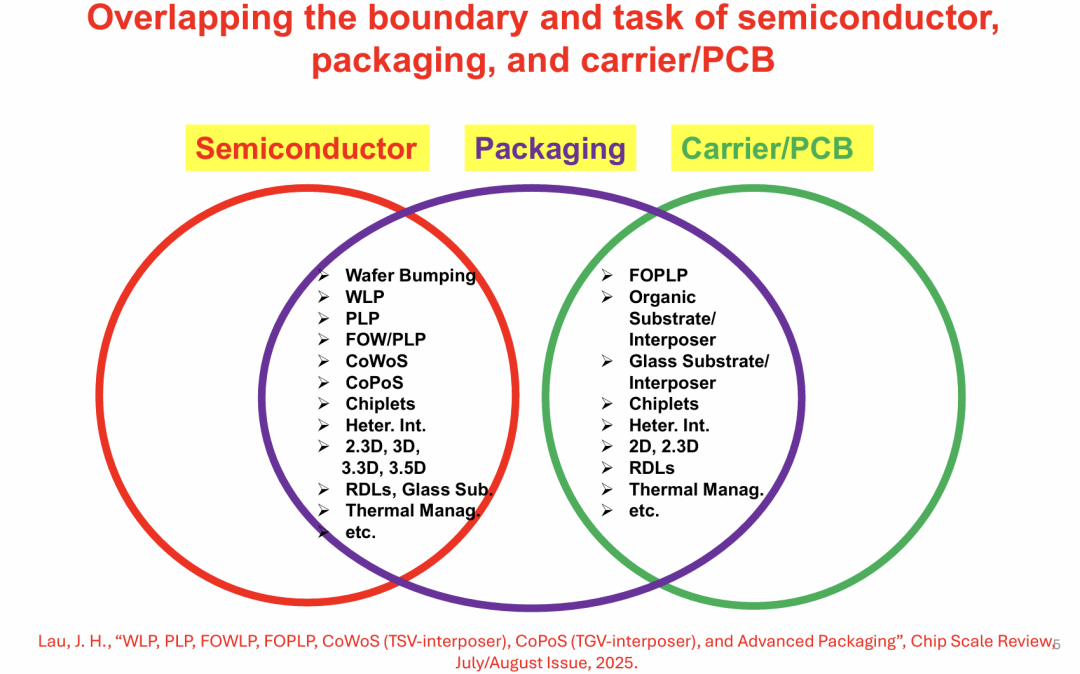

然而,随着产业不断推进先进封装技术的极限,这种清晰的界限已经变得越来越模糊。如今,这些传统边界出现显著重叠,封装技术融合了晶圆凸点、晶圆级封装、面板级封装、扇出晶圆/面板级封装、芯片-晶圆-基板集成、Chiplet以及包括2.3D、3D、3.3D和3.5D配置在内的各种异构集成形式。

图2:现代先进封装如何在传统独立域之间创造显著重叠,展示WLP、PLP、FOWLP、FOPLP、CoWoS、CoPoS和Chiplet等技术跨越多个传统边界

02Chiplet概念及其影响

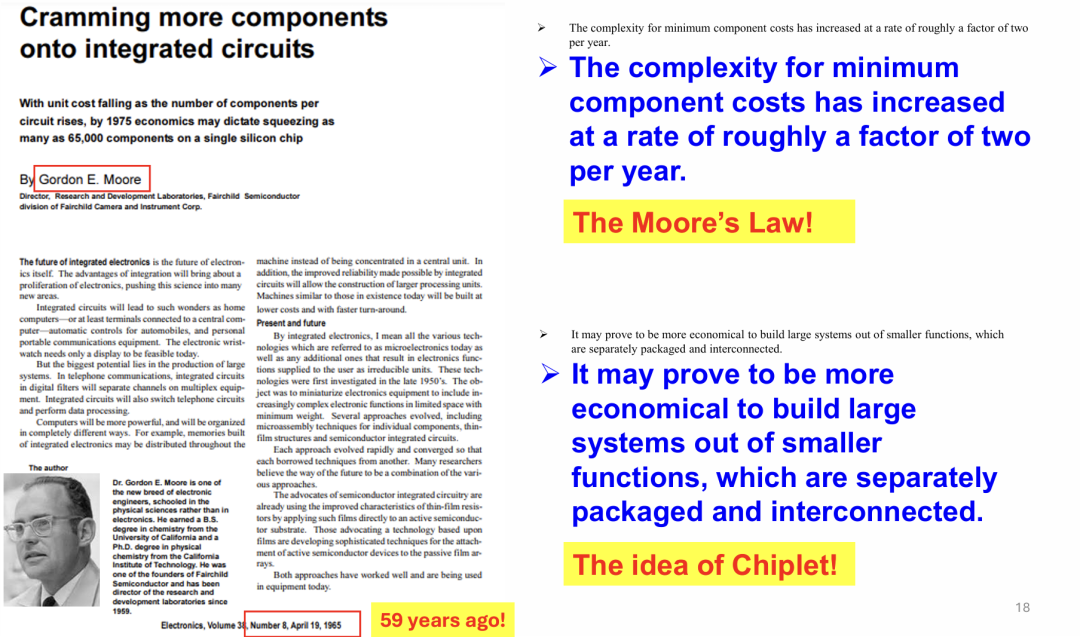

Chiplet概念代表着自集成电路发明以来半导体设计方法学的重大范式转变。值得注意的是,Chiplet的基本思想早在近六十年前就由戈登·摩尔提出,他观察到,由较小的、分别封装并互连的功能模块构建大型系统可能更加经济。这一深刻洞察,结合他关于元件复杂度每两年翻倍的著名观察,为我们现在所认知的摩尔定律和Chiplet革新奠定了基础。

图3:戈登·摩尔在1965年关于从更小的、分别封装的功能模块构建系统的原始见解,证明Chiplet概念比其现代实现早了近六十年

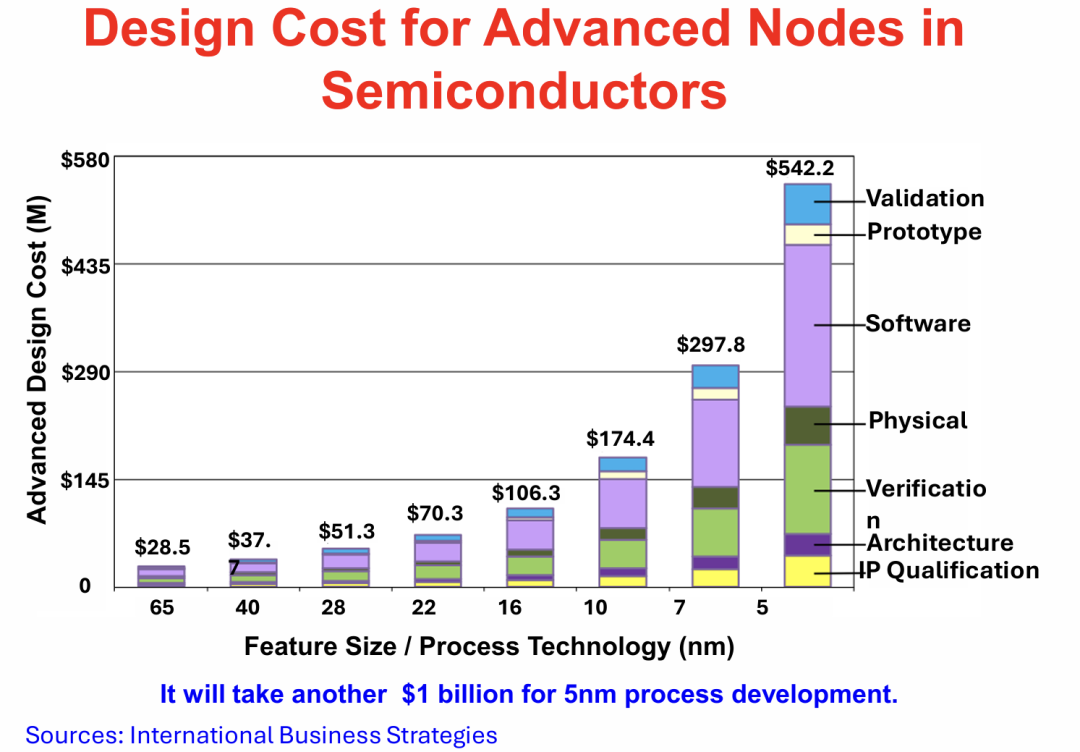

区分Chiplet和异构集成对理解现代半导体架构是关键的。Chiplet代表一种芯片设计方法学,涉及将大型单片系统级芯片设计划分为更小、更易管理的组件。每个Chiplet都可以针对其特定功能进行优化,使用最适合的工艺技术制造,并可能来自不同的代工厂。这种方法解决了半导体产业面临的几个关键挑战,特别是随着特征尺寸继续缩小和制造成本指数级上升。

图4:随着半导体工艺节点的发展,设计成本的急剧增加,显示成本从65nm的2850万美元上升到5nm的超过5.4亿美元,使Chiplet方法从经济角度越来越有吸引力

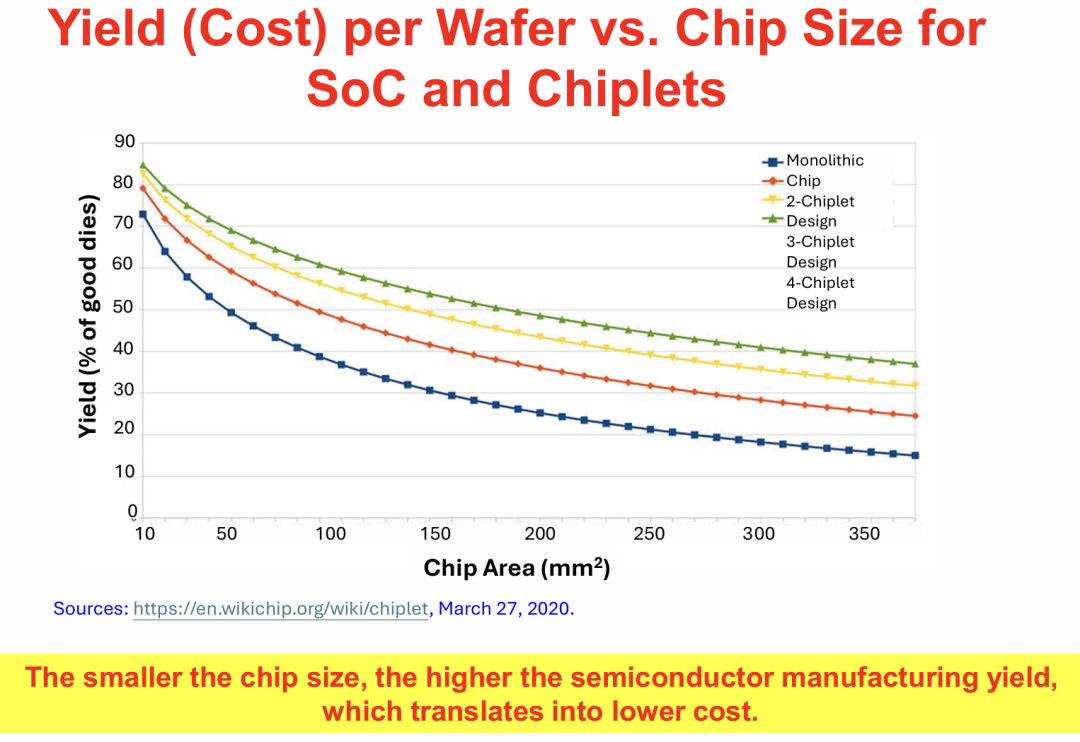

Chiplet采用的经济驱动因素在检查不同芯片尺寸的良率特征时变得明显。较大的单片芯片制造良率较低,因为整个芯片区域内的任何缺陷都会使整个器件无法使用。通过将功能划分为更小的Chiplet,制造商可以为每个单独元件实现更高的良率,从而获得更好的整体成本效率。

图5:随着芯片面积增加,单片设计的良率急剧下降,而基于Chiplet的方法通过使用更小的单独元件保持更高的良率

03集成方法的演进

半导体封装产业已经发展出复杂的分类法来描述不同层次的集成复杂度。这些范围从传统的2D集成方法到日益复杂的3D配置,每种都提供不同的优势并解决特定的应用需求。

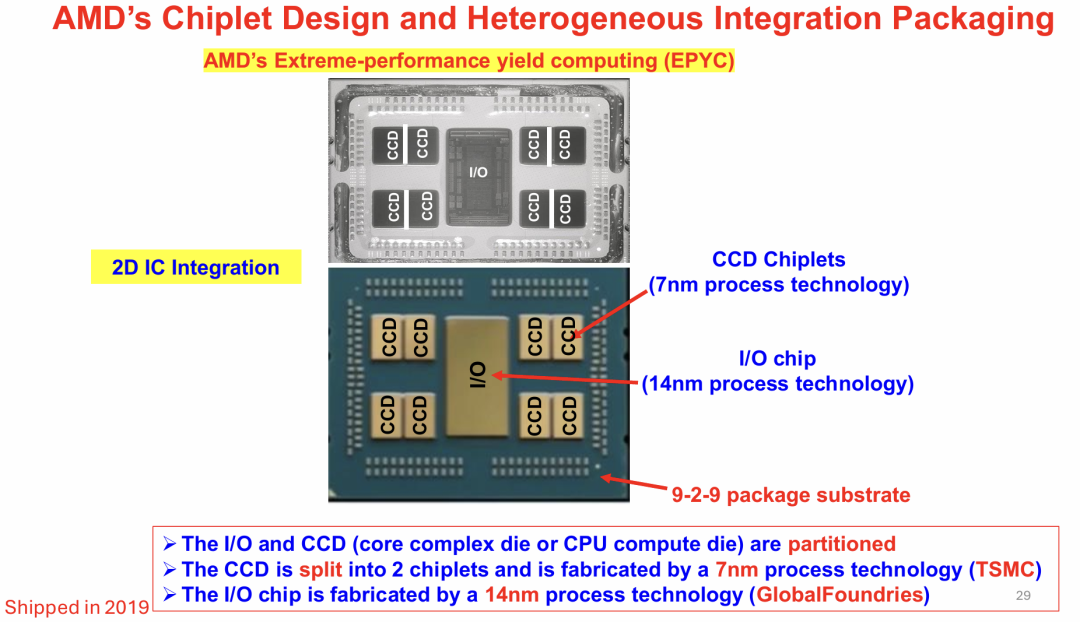

2D集成代表构建更复杂方法的基础。这涉及将多个芯片并排放置在共同基板上,允许增加功能性,同时保持相对简单的制造工艺。先进例子包括AMD的EPYC处理器,展示了复杂的2D Chiplet集成,通过将输入/输出功能与计算核心复合管芯分离。

图6:AMD的2D Chiplet集成方法,其中I/O和核心复合管芯被分离并使用不同的工艺技术制造(I/O使用14nm,计算核心使用7nm),然后在共同基板上集成

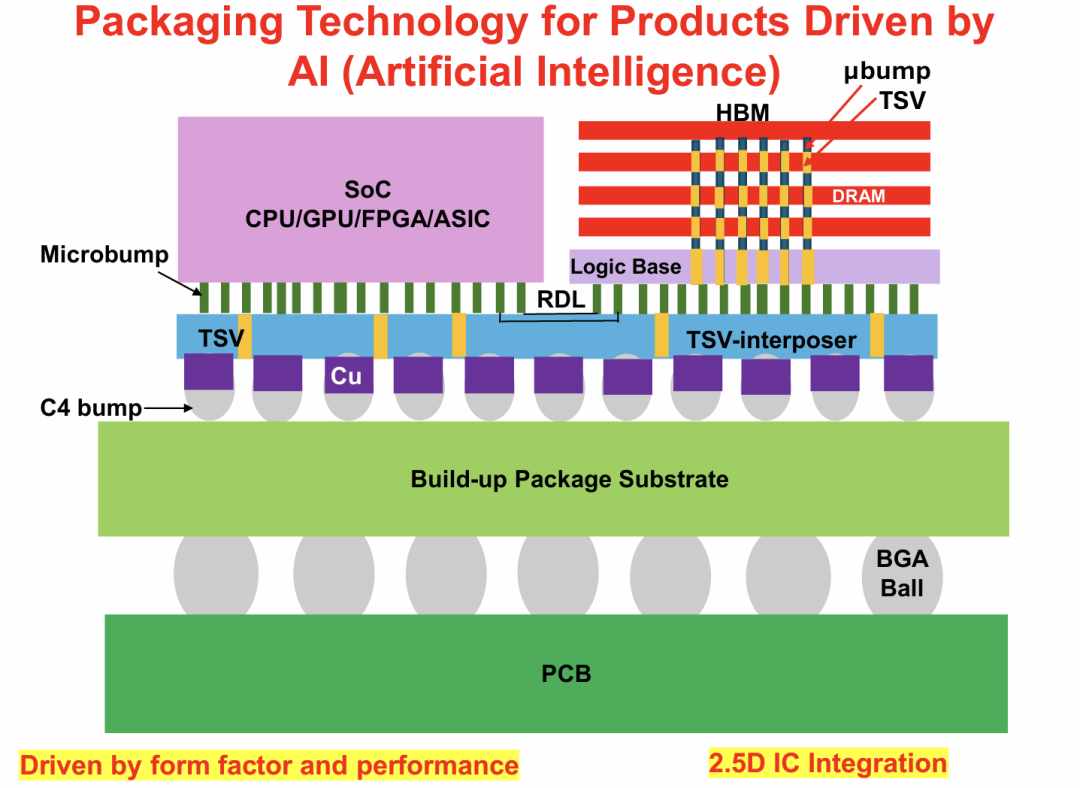

向2.5D集成的进展引入了硅通孔技术和Interposer,允许Chiplet之间更密集的互连,同时保持并排放置的基本概念。这种方法对于人工智能工作负载驱动的高性能计算应用特别有价值,其中处理器和内存之间的带宽要求超过了传统封装方法能够提供的能力。

图7:2.5D集成的关键组件,包括TSV-Interposer、微凸点、C4凸点,以及逻辑和内存元件在共同Interposer基板上的排列

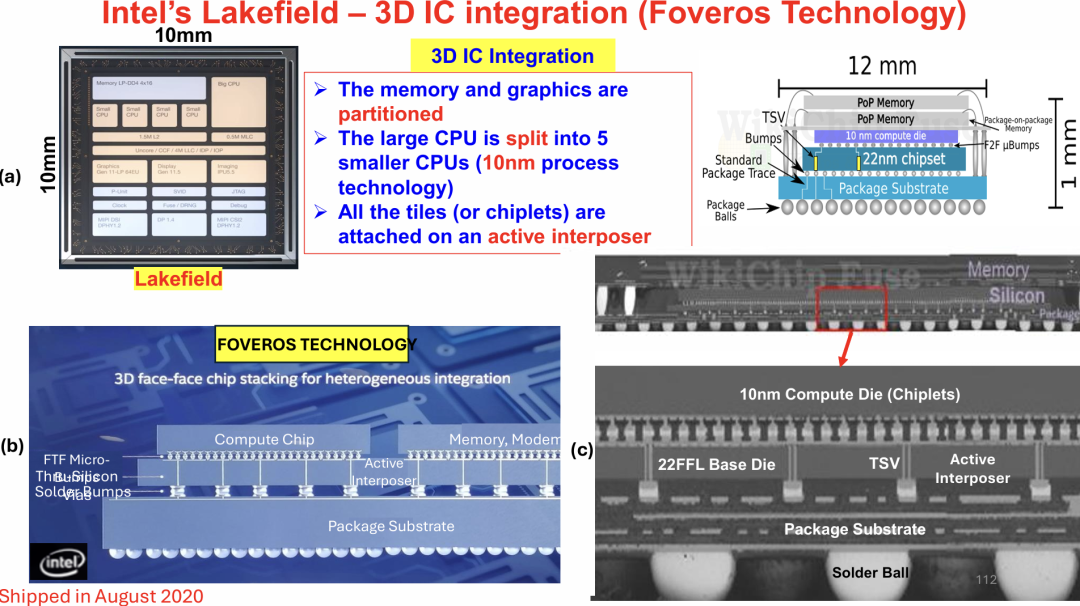

3D集成代表空间高效封装的终极表达,其中Chiplet垂直堆叠以创建真正的三维系统。英特尔的Foveros技术和Lakefield处理器体现了这种方法,展示计算Chiplet如何堆叠在有源Interposer上以创建紧凑的高性能系统。

图8:英特尔使用Foveros技术的3D IC集成方法,其中10nm计算Chiplet使用面对面微凸点和硅通孔堆叠在22FFL基础管芯上

04先进基板技术

支持这些复杂集成方法的基板技术代表电子产业中最先进的制造工艺。这些基板必须不仅提供机械支撑和电气连接,还要提供热管理、信号完整性,以及跨多个电压域和频率范围的功率传输。

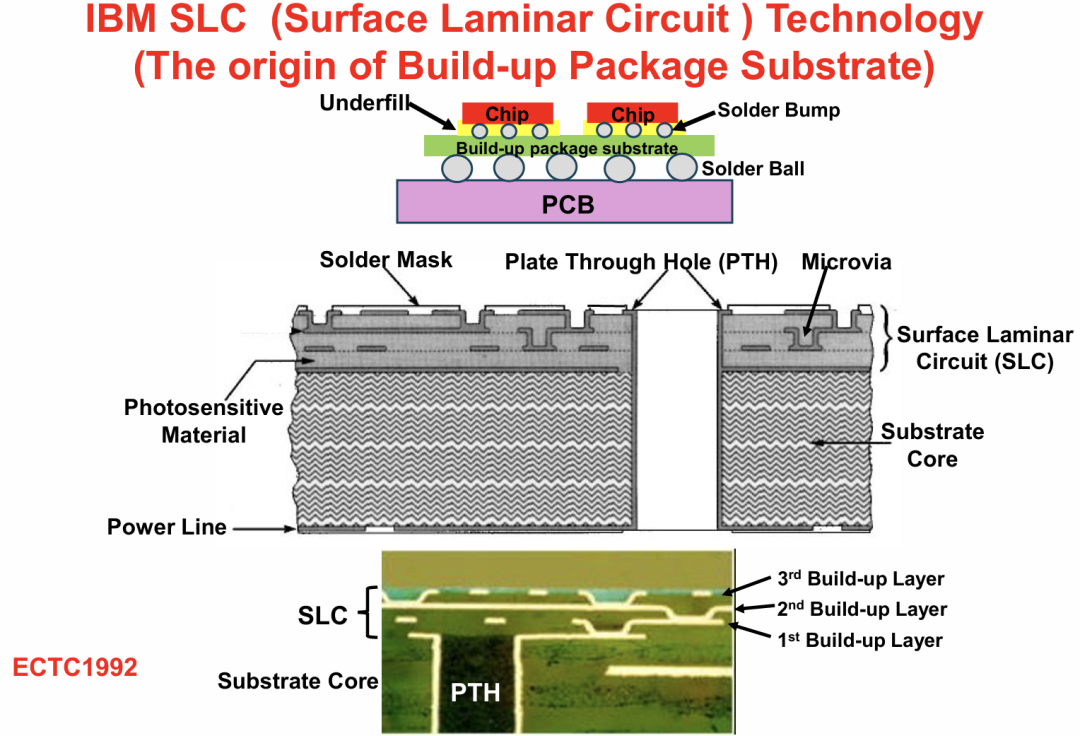

构建封装基板形成许多先进封装应用的基础。这些多层有机基板使用先进材料和制造工艺来实现细间距互连,同时保持可靠运行所需的机械和热性能。从简单印刷线路板到具有多个再分布层的复杂构建基板的演进代表了数十年的材料科学和制造工艺发展。

图9:显示构建封装基板的结构,说明实现高密度封装的多个层、微通孔和通孔互连

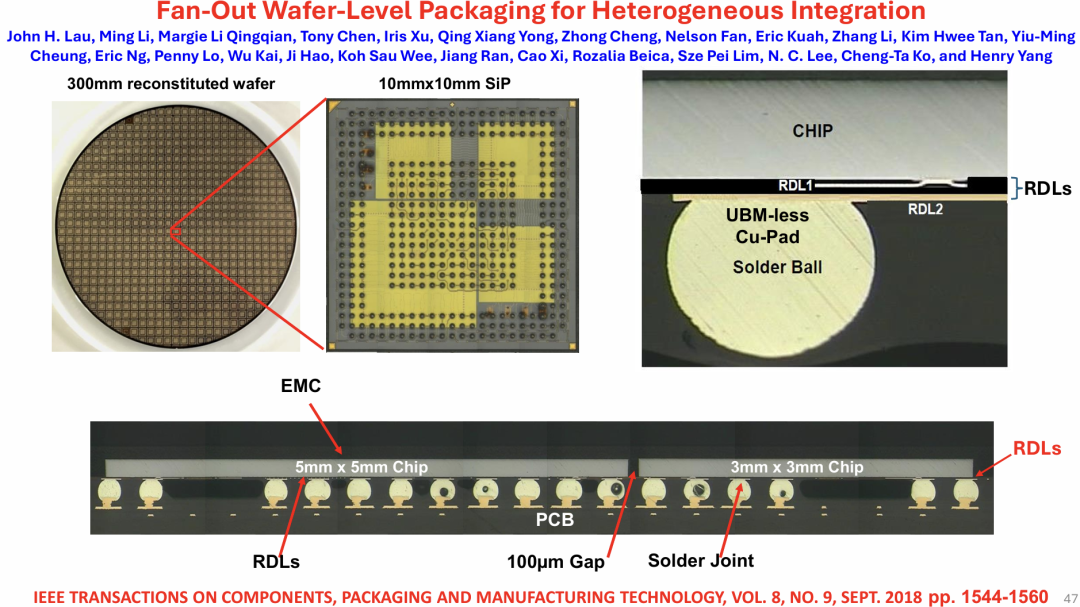

扇出封装技术代表基板技术的另一个关键进展。这些方法使用再分布层将芯片的输入/输出能力扩展到其物理边界之外,实现更高的引脚数和更好的热性能。从晶圆级到面板级扇出封装的进展提高了面积效率并降低了成本,同时保持扇出方法的技术优势。

图10:扇出晶圆级封装集成多个不同尺寸的芯片,通过再分布层连接并封装在环氧模塑化合物中

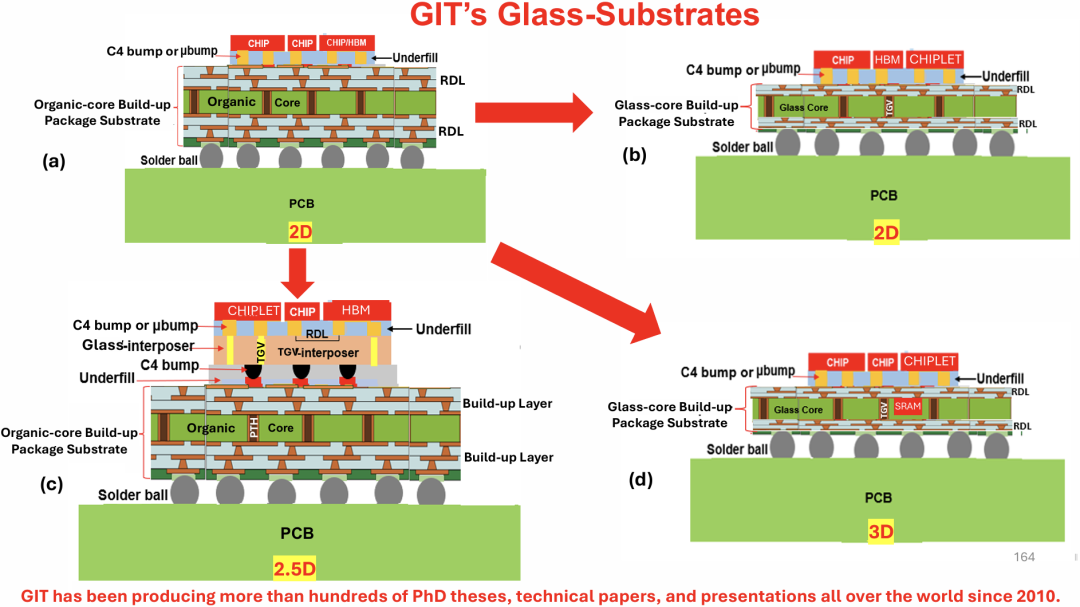

玻璃芯基板代表下一代封装应用最有前景的新兴技术之一。与有机基板相比,这些基板提供卓越的平整度、尺寸稳定性和热性能,实现更精细间距的互连和更大的封装尺寸。通玻璃孔技术和兼容处理方法的发展使玻璃基板对高性能应用越来越可行。

图11:比较玻璃芯和有机芯构建基板,显示玻璃芯如何实现不同的集成方法,包括2.5D TSV-Interposer和直接芯片贴装

05混合键合和先进互连技术

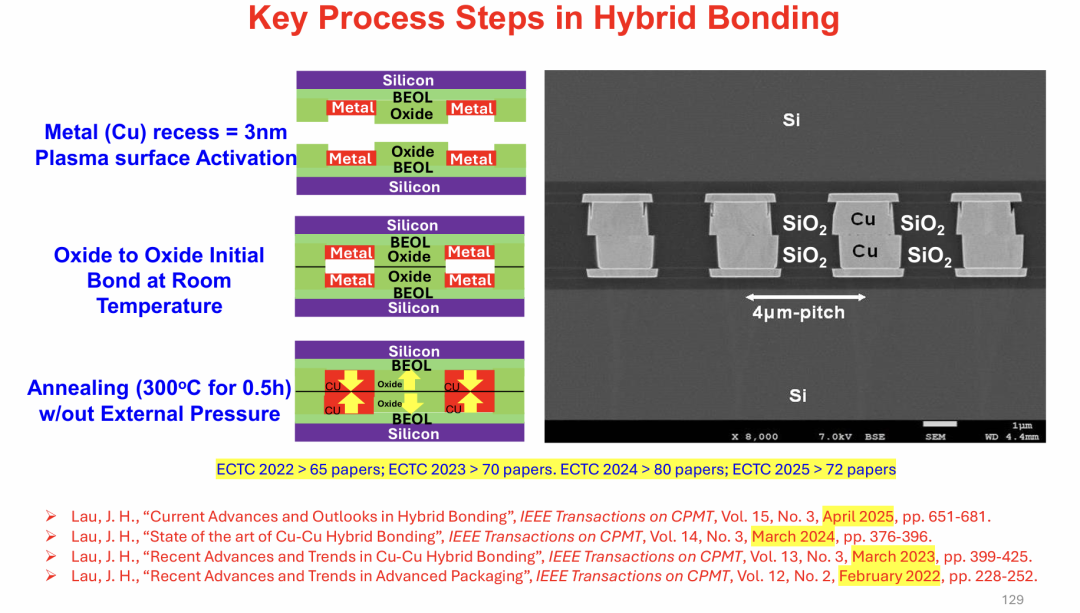

向更精细间距互连的演进推动了混合键合技术的发展,消除了对焊料凸点的需求,转而采用直接金属对金属连接。铜对铜混合键合代表高密度互连技术的当前最高水平,实现以微米为单位测量的连接间距,而不是传统焊料基方法典型的数十或数百微米。

图12:混合键合的关键步骤,包括室温下的氧化物对氧化物初始键合,然后退火以在无外部压力的情况下创建金属对金属连接

混合键合的优势超出了简单的间距缩减。消除焊料凸点减少了寄生电感和电容,改善了高频下的电气性能。直接金属连接还提供卓越的热导率,使高功率Chiplet能够更好地散热。这些优势使混合键合对包括高带宽存储器集成和高性能计算Chiplet在内的先进应用必不可少。

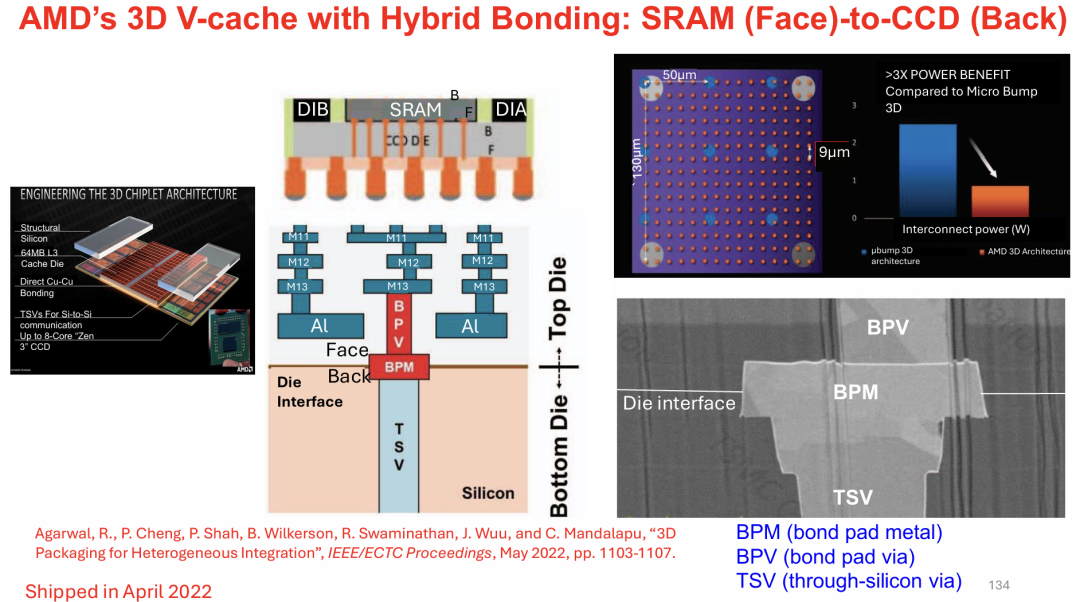

多家公司已成功在生产应用中实施混合键合。索尼的CMOS图像传感器是最早的商业应用之一,展示了堆叠传感器架构的晶圆对晶圆键合。最近,AMD使用台积电的混合键合技术创建了3D V-cache结构,显著改善了某些工作负载的处理器性能。

图13:AMD实施的3D V-cache混合键合,其中SRAM缓存管芯与CPU核心面对背键合,通过直接铜对铜接口连接

06光电共封装和光电子技术集成

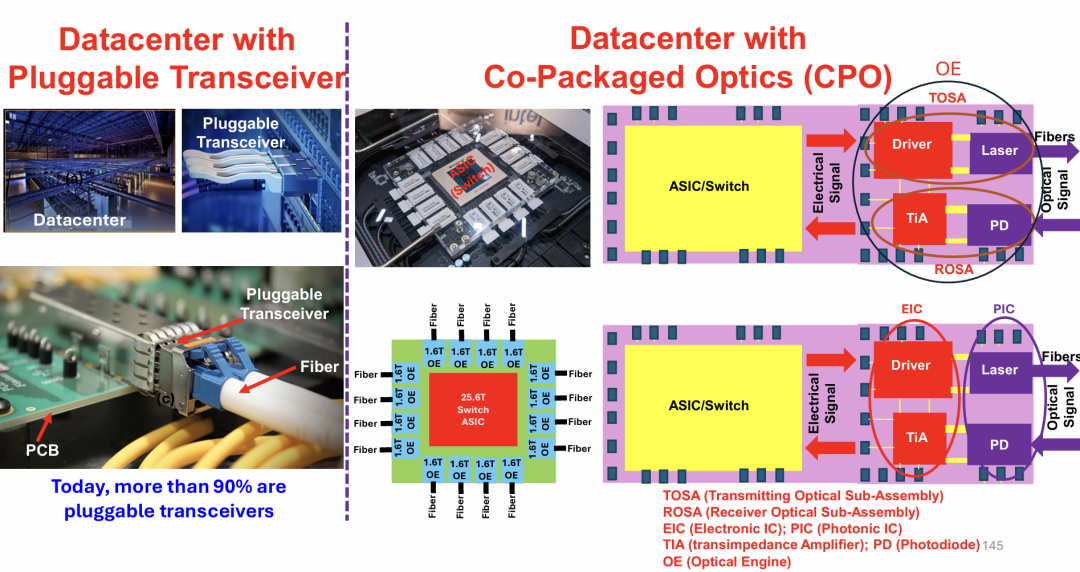

现代数据中心和高性能计算应用不断增长的带宽需求推动了光电共封装技术的发展。这些方法在封装级别集成光电子技术和电子元件,与传统可插拔光收发器相比,降低了功耗并改善了性能。

图14:从可插拔收发器到光电共封装的演进,说明光引擎如何直接与交换机ASIC集成以降低功耗并改善性能

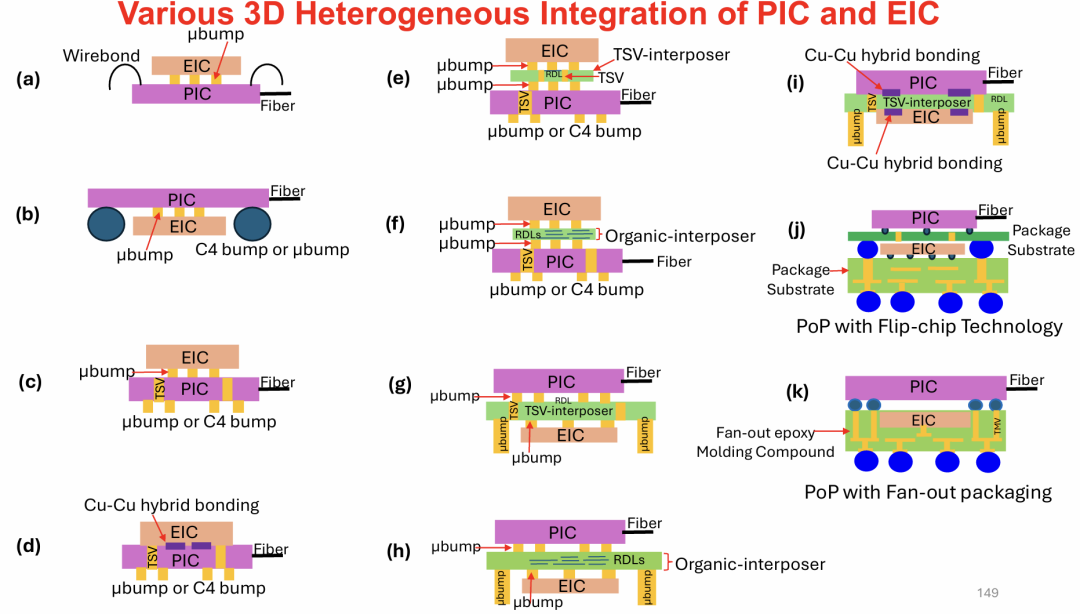

光电子集成芯片和电子集成线路的3D异构集成代表目前产业面临的最复杂封装挑战之一。这些系统必须同时管理高速电信号、光信号、热耗散和机械稳定性,同时保持光耦合和对准所需的精度。

图15:集成光电子集成芯片(PIC)和电子集成线路(EIC)的不同方法,包括各种键合技术、Interposer方法和堆叠配置

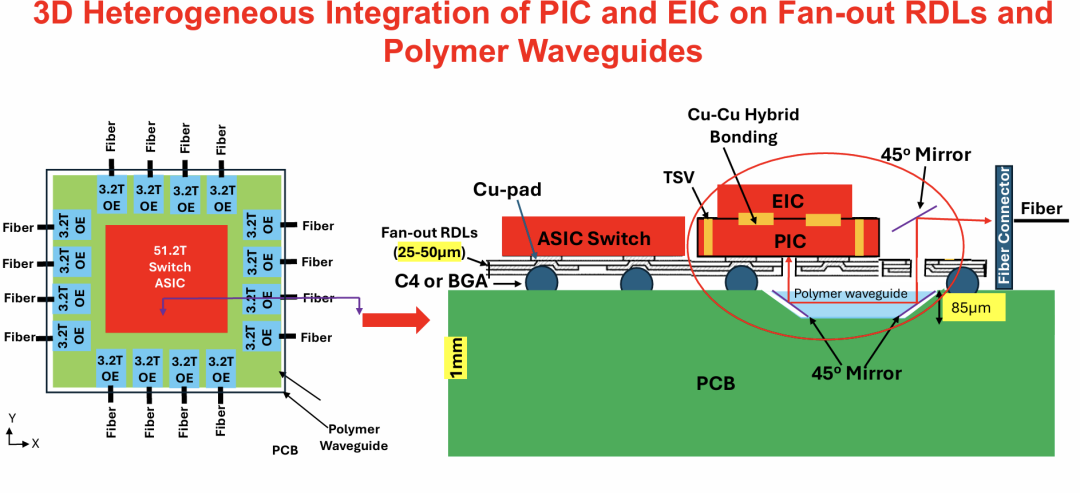

先进的光电共封装实现融合了复杂的基板技术,包括嵌入式聚合物波导、具有集成光路由的玻璃Interposer,以及多个功能模块的3D集成。这些方法能够创建使用分立元件无法实现的系统,同时提供下一代应用所需的性能和功率效率。

图16:使用嵌入式聚合物波导、45度反射镜和光电子技术与电子元件3D集成的先进光电共封装实现

07未来趋势和新兴技术

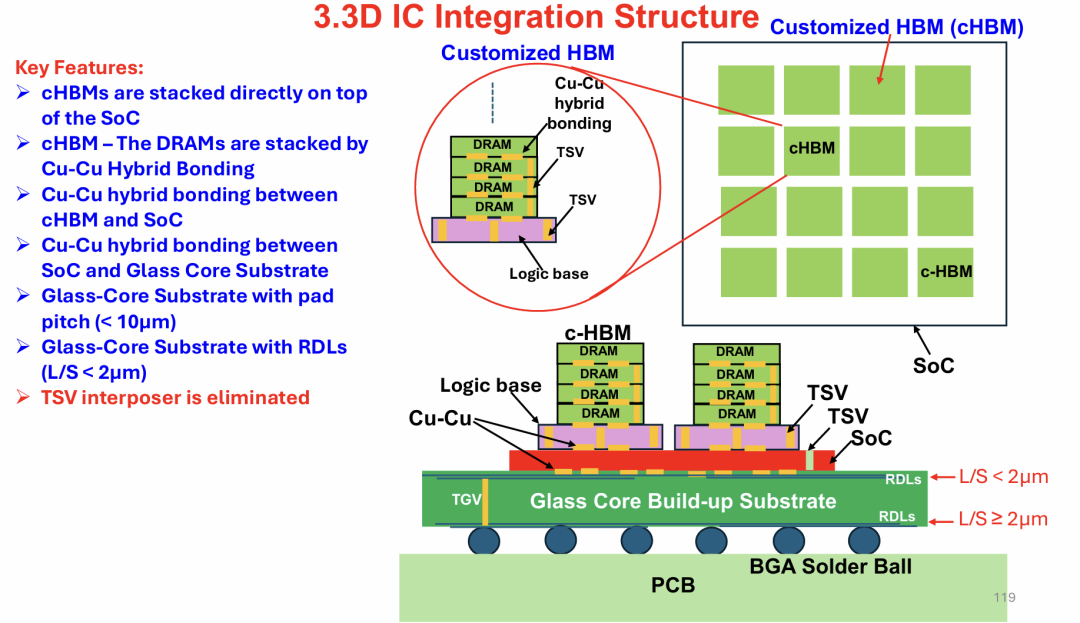

半导体封装产业持续快速演进,几个新兴趋势指向更复杂的集成方法。3.3D和3.5D集成技术的发展代表封装复杂性的下一个前沿,结合Chiplet设计的优势与先进3D堆叠和混合键合技术。

定制高带宽存储器代表先进封装近期最重要的发展之一。这些方法使用混合键合技术将DRAM堆叠直接集成到计算Chiplet上,消除对单独Interposer基板的需求,同时改善性能并降低功耗。

图17:定制HBM集成的结构,显示DRAM堆叠如何使用铜对铜混合键合直接键合到玻璃芯基板上的系统级芯片器件

玻璃基板技术与先进再分布层工艺的集成创造了以前不可能实现的高密度封装新方法。这些基板提供亚二微米线宽和间距几何所需的平整度和尺寸稳定性,同时支持3D路由的通玻璃孔技术。

这些技术的持续演进将创建具有集成和性能水平的系统。产业路线图指向到2030年包含超过一万亿晶体管的封装,这只有通过Chiplet设计方法学、先进基板技术和3D集成方法的复杂结合才能实现。

随着这些技术成熟并得到更广泛采用,将为利用异构集成独特优势的新类别应用和系统创造条件。不同工艺技术、Chiplet架构和先进封装方法的结合为系统设计师提供了在针对特定应用需求优化性能、功耗和成本方面的灵活性。这种灵活性代表Chiplet和先进封装技术的真正价值,使在传统单片芯片设计约束下不可能的创新得以实现。

关于我们:

天府逍遥(成都)科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

-

多Chiplet异构集成的先进互连技术2026-02-02 2726

-

先进封装技术-19 HBM与3D封装仿真2025-01-08 3609

-

先进封装技术-16硅桥技术(上)2024-12-24 3897

-

人工智能应用中的异构集成技术2024-12-10 2070

-

先进封装技术- 6扇出型晶圆级封装(FOWLP)2024-12-06 4240

-

华芯邦科技开创异构集成新纪元,Chiplet异构集成技术衍生HIM异构集成模块赋能孔科微电子新赛道2024-01-18 1666

-

一文解析Chiplet中的先进封装技术2023-07-17 7375

-

Chiplet和异构集成时代芯片测试的挑战与机遇2023-07-12 3081

-

Chiplet和异构集成对先进封装技术的影响2023-06-16 1734

-

先进封装Chiplet的优缺点与应用场景2023-06-13 2296

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1479

-

半导体芯片先进封装——CHIPLET2022-10-06 31102

-

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet2021-01-04 60935

全部0条评论

快来发表一下你的评论吧 !