ADS125H02 宽输入范围高精度 ΔΣ ADC 技术参数与应用总结

描述

该ADS125H02是一款±20V输入、24位、三角积分(ΔΣ)模数转换器(ADC)。该ADC具有低噪声可编程增益放大器(PGA)、内部基准电压源、时钟振荡器以及信号或基准超出范围监视器。

与分立式解决方案相比,将宽输入范围、±18V PGA 和 ADC 集成到单个封装中,可减少高达 50% 的电路板面积。

*附件:ads125h02.pdf

0.125 至 128 的可编程增益(对应于 ±20 V 至 ±20 mV 的等效输入范围),无需外部衰减器或外部增益级。1GΩ 最小输入阻抗可减少传感器负载引起的误差。此外,低噪声和低漂移性能允许直接连接到电桥、电阻温度检测器 (RTD) 和热电偶传感器。

数字滤波器可衰减 50 Hz 和 60 Hz 线路周期噪声,数据速率≤ 50 SPS 或 60 SPS,以减少测量误差。该滤波器还提供无延迟转换数据,以在通道排序期间实现高数据吞吐量。

该ADS125H02采用5mm×5mm VQFN封装,在–40°C至+125°C温度范围内完全额定。

特性

- ±20V 输入、24 位 Δ-Σ ADC

- 可编程数据速率:2.5 SPS至40 kSPS

- 高压、高阻抗 PGA:

- 差分输入范围:高达 ±20 V

- 可编程增益:0.125 至 128

- 共模输入电压:高达 ±15.5 V

- 输入阻抗:1 GΩ(最小值)

- 高性能ADC:

- 输入噪声:45 nV

有效值(20 SPS) - CMRR:105 分贝

- 50 Hz、60 Hz 时的正常模式抑制:95 dB

- 失调漂移:5 nV/°C

- 增益漂移:1 ppm/°C

- INL:2 ppm

- 输入噪声:45 nV

- 集成功能和诊断:

- 2.5V 基准电压源:3 ppm/°C 漂移

- 时钟振荡器:2.5%误差(最大值)

- 励磁电流源

- GPIO 驱动外部多路复用器

- 信号和参考电压监控器

- 循环冗余校验 (CRC)

- 电源:

- AVDD:4.75 V 至 5.25 V

- DVDD:2.7 V 至 5.25 V

- HVDD:±5 V 至 ±18 V

- 工作温度:–40°C 至 +125°C

- 5mm × 5mm VQFN 封装

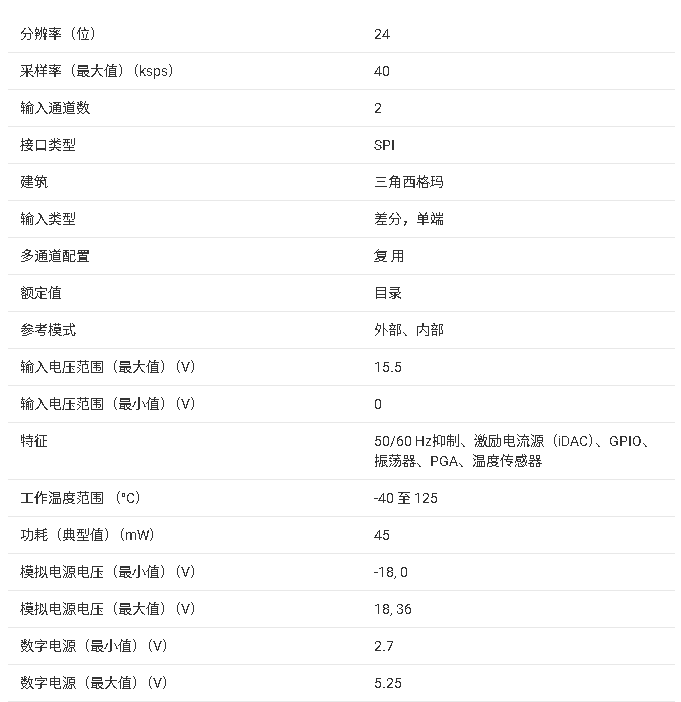

参数

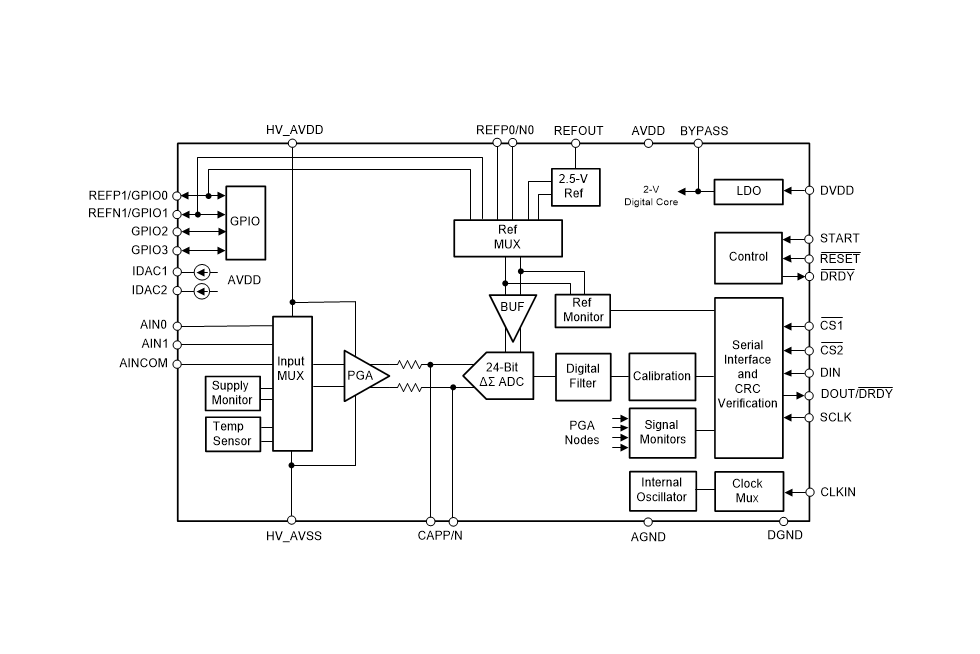

方框图

ADS125H02 是德州仪器推出的 24 位宽输入范围 ΔΣ ADC,核心优势是 ±20V 高压输入、可编程增益及低漂移特性,专为工业 PLC、测试测量及传感器信号采集场景设计。

一、核心参数与性能特性

- 分辨率与精度 :24 位分辨率(无失码),INL 最大 ±4 ppm FSR,偏移漂移低至 5 nV/°C,增益漂移 1 ppm/°C;20 SPS 时输入噪声 45 nVₙₘₛ,CMRR 达 105 dB,50/60 Hz 工频抑制比 95 dB。

- 输入与增益 :支持 ±20V 差分输入、±15.5V 共模输入,输入阻抗≥1 GΩ;可编程增益 0.125-128 倍,对应输入范围 ±20V 至 ±19.5 mV,无需外部衰减 / 放大电路。

- 采样与滤波 :采样率 2.5 SPS-40 kSPS,支持 Sinc1-Sinc5 及 FIR 滤波;FIR 模式可同时抑制 50/60 Hz 干扰,Sinc 滤波可优化延迟与噪声平衡。

- 核心功能 :内置 2.5 V 基准源(温漂 3 ppm/°C)、温度传感器(精度 ±2.5°C);集成两路可编程激励电流源(50 µA-3 mA)、4 路 GPIO(可驱动外部多路器);具备 PGA 过载监测、参考电压监测及 CRC 数据校验功能。

- 供电与接口 :高压电源 ±5V-±18V(或单端 10V-36V),模拟电源 4.75V-5.25V,数字电源 2.7V-5.25V;SPI 兼容接口,支持 CS1/CS2 双片选,DOUT/DRDY 引脚兼具数据输出与就绪指示功能。

二、应用场景

适用于工业 PLC 模拟输入模块(电压 / 电流信号)、热电偶 / RTD 温度测量、电池测试、高端电流检测、高共模电压信号采集等工业及测试测量场景。

三、封装与订购信息

- 采用 5mm×5mm 32 引脚 VQFN 封装,带裸露热焊盘。

- 量产型号包括大卷带(3000 片 / 卷)和小卷带(250 片 / 卷)包装,符合 RoHS 标准,引脚镀层为 NIPDAU。

- MSL 等级 3,峰值回流温度 260°C,工作温度 - 40°C 至 125°C,满足宽温工业环境要求。

四、设计与支持建议

- 硬件设计要点 :电源去耦需在 HV_AVDD/HV_AVSS 引脚就近放置 0.1 µF+1 µF 电容,AVDD/DVDD 引脚搭配 10 µF+0.1 µF 电容;CAPP/CAPN 引脚需外接 1 nF C0G 电容优化抗混叠滤波;参考引脚 REFOUT 需接 10 µF 滤波电容。

- 布局规范 :PCB 需划分模拟与数字区域,数字迹线远离模拟输入及基准引脚;热焊盘需焊接至地平面,降低热阻;模拟地与数字地单点连接,避免串扰。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS125H02通过cs2读写寄存器失败的原因?2024-11-18 381

-

请问ADS125H02支持单电源供电,单端输入吗?2024-11-26 522

-

ADS125H02采样速度很慢怎么解决?2024-11-29 351

-

通过外部多路选择开关来动态切换不同采样目标时,ADS125H02的内部数字滤波器是否会导致采样的结果会相互影响?2024-12-03 351

-

ADS125H02开发板噪声大的原因?怎么解决?2024-12-05 271

-

ADS125H02 具有 ±10V 高电压输入、PGA、2 个 IDAC 和低漂移基准电压的 24 位、40kSPS、2 通道 Δ-Σ ADC2019-01-08 1455

-

ADS125H02 ±20V输入、双通道、40kSPS、24位 Δ-ΣADC数据表2024-07-23 604

-

替换ADS1283/ADS1284,国产ADC用于低速高精度精密测量2024-09-13 2324

-

利用ADS125H02简化±10V PLC模拟输入模块信号链2024-09-23 400

-

ADS125H02评估模块2024-11-25 437

-

ADS125H01 24位、40kSPS、1通道Δ-Sigma ADC技术手册2025-11-01 1089

-

ADS1260-Q1 车规级高精度 ΔΣ ADC 技术参数与应用总结2025-11-04 643

-

ADS1262/ADS1263 32 位高精度 ADC 技术文档总结2025-11-11 2489

-

深度剖析ADS1255/6:24位高精度ADC的卓越之选2025-12-04 1211

-

深度剖析ADS1242和ADS1243:高精度ADC的卓越之选2025-12-10 690

全部0条评论

快来发表一下你的评论吧 !