Vishay SiC658A集成功率级技术解析:打造高效能同步降压解决方案

描述

Vishay SiC658A 50A VRPower ^®^ 集成功率级具备高效率和出色的散热性能,非常适合大电流应用。Vishay SiC658A凭借先进的MOSFET技术,可确保最佳电源转换并降低开关损耗,从而提高服务器和计算系统的可靠性。该模块采用热增强型PowerPAK^®^ MLP55-31L封装,支持高达50A持续电流,工作频率高达1.5MHz。

数据手册:*附件:Vishay SiC658A 50A VRPower®集成功率级数据手册.pdf

特性

- 沟槽场效应晶体管技术

- 低侧MOSFET,集成肖特基二极管

- 零电流检测控制功能,可提高轻负载效率

- 低PWM传播延迟

- 热监控和故障标志

- 欠压闭锁保护

- 过流保护

- 高侧FET短路保护

- 过热保护

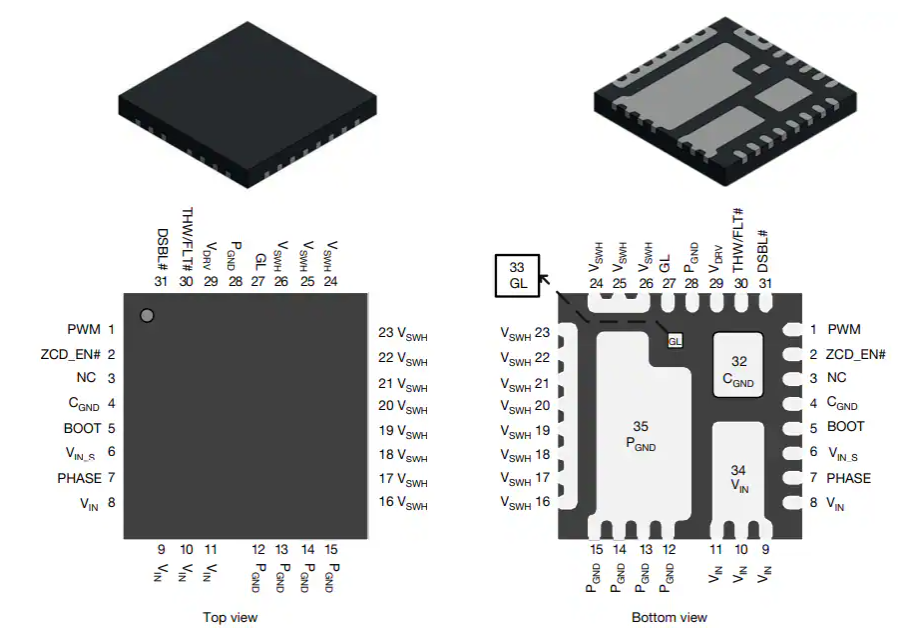

引脚配置

典型应用图

Vishay SiC658A集成功率级技术解析:打造高效能同步降压解决方案

产品概述与技术亮点

Vishay SiC658A是一款集成化的功率级解决方案,专门针对同步降压应用进行优化,可实现高电流、高效率和高功率密度的卓越性能。该器件采用Vishay的5 mm x 5 mm MLP封装,使电压调节器设计能够每相提供高达50 A连续电流。

核心技术特性

先进半导体工艺

- 内部功率MOSFET采用Vishay最先进的TrenchFET技术

- 提供业界标杆性能,显著降低开关和导通损耗

- 支持高达1.5 MHz高频操作

- 针对12 V输入级优化的功率MOSFET

集成驱动保护系统

- 具备高电流驱动能力

- 自适应死区时间控制

- 集成自举开关

- 温度传感器监测结温并提供损坏保护

- 零电流检测改善轻载效率

电气参数深度分析

工作电压范围

- 输入电压(VIN) :4.5 V至24 V

- 驱动电源电压(VDRV) :4.5 V至5.5 V

- 连续电流输出:50 A(持续),80 A峰值(10 ms),100 A峰值(10 μs)

保护功能全集

- 欠压锁定保护 - 确保电源稳定后启动

- 过流保护 - 高侧FET电流限制保护

- 过温保护 - 结温超过160°C时自动关闭

- 高侧FET短路检测 - 逐周期监控开关节点

- 热监视器和故障标志 - 实时温度监控

应用架构设计指南

典型应用电路

该器件兼容多种PWM控制器,支持三态PWM和3.3 V逻辑,典型应用包括:

- 多相VRD用于CPU、GPU和内存

- 高性能计算电源解决方案

- 数据中心电源管理系统

引脚功能详解

关键控制引脚

- PWM(引脚1) :PWM控制输入,兼容标准控制器和先进控制器

- ZCD_EN#(引脚2) :使能或禁用二极管仿真模式

- DSBL#(引脚31) :主动低信号禁用器件

功率连接引脚

- VIN(引脚8-11,34) :功率级输入电压,高侧MOSFET的漏极

- PGND(引脚12-15,28,35) :功率接地

- VSWH(引脚16-26) :功率级开关节点

先进控制特性

PWM输入与三态功能

PWM输入接收来自VR控制器IC的PWM控制信号,支持:

- 双态逻辑(H和L) :传统控制模式

- 三态逻辑:允许MOSFET进入高阻抗状态

三态工作机制:

- 当PWM输入保持在三态区域达到三态保持关闭时间(tTSHO)

- 同时关闭高侧和低侧MOSFET

- 通过迟滞防止误触发

过流保护运行机制

- 高侧FET电流超过限制时立即终止导通

- 开启低侧FET,直到电流降至迟滞阈值以下

- 在过流条件下不会锁存关闭,继续在过流限制下运行

死区时间优化技术

- 内部自适应逻辑避免直通

- 通过专门监控HS和LS栅极电压实现优化

- 自动调整和最小化死区时间,适应负载和温度变化

PCB布局关键推荐

布局策略七步法

第一步:VIN/GND平面和去耦

- 按推荐布局VIN和PGND平面

- 陶瓷电容应直接放置在VIN和PGND之间

- 使用不同值/封装的陶瓷电容覆盖整个去耦频谱

第二步:VSWH平面设计

- 使用大平面连接输出电感,降低电阻

- 如需要缓冲网络,组件应按推荐放置

第三步:VDRV输入滤波器

- 滤波器陶瓷电容应非常靠近IC

- 建议分别连接两个电容

- 使用大平面连接CVDRV模拟接地

第四步:自举组件放置

- 组件需要非常靠近IC

- 使用0402芯片尺寸减小寄生电感

第五步:信号布线

- PWM/ZCD_EN#/DSBL#/THW/FLT#信号走线应从顶行引出

- 避免信号和返回走线靠近任何噪声走线或平面

第六步:热释放过孔

- 在VIN和PGND焊盘上添加热释放过孔

- 实现更好的热性能,将过孔放置在平面和内层

第七步:接地连接优化

- 建议在CGND和PGND之间建立单连接

- 整个内层1(顶层下方)应制作为接地平面

多相架构实现

该器件支持多相VRPower PCB布局,典型实现包括:

- 紧凑的X方向排列:所有VRPower级沿X方向紧凑排列

- 最短的电流路径:电感尽可能靠近SiC658A放置

- 多层铜平面设计:在所有高电流环路使用大铜平面

性能特征总结

电气特性优势

- 在不同开关频率下均保持高效率曲线

- 支持从500 kHz至1 MHz的宽频率范围

- 在不同输出电流下表现出优越的功率损耗特性

热管理能力

- 结到环境热阻:典型值10.6°C/W

- 结到底部外壳热阻:典型值1.6°C/W

- 结到顶部外壳热阻:典型值12.6°C/W

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Vishay SiC544 40A VRPower®集成功率级技术解析与应用指南2025-11-13 325

-

基于Vishay SiC653A数据手册的技术解析与应用指南2025-11-11 338

-

CSD95411同步降压NexFET™功率级技术解析与应用指南2025-08-28 657

-

SQ76115BADE同步降压DC/DC转换器:高效能、宽输入电压解决方案2025-06-26 3671

-

美容与生发产品的高效电源解决方案--禾润HT7166聚能芯半导体协助开发原厂技术支持2025-06-05 1196

-

SILERGY矽力杰集成功率级DrMOS方案2023-06-07 2081

-

求AMD R系列与AMD SOC系列嵌入式高效能解决方案2021-05-10 1985

-

集成功率器件可简化FPGA和SoC设计2017-04-01 2901

-

Vishay推新款VRPower®集成式DrMOS功率级解决方案2016-02-17 1600

-

Fairchild,NXP,ON,TI电源供应解决方案及Vishay周边应用2015-04-23 3880

-

博通发布最新高效能StrataXGS交换解决方案2011-10-04 1470

-

Vishay发布新款集成功率光敏2010-03-26 968

-

microBUCK系列集成同步降压稳压器SiC414(Vis2010-03-23 1336

-

首批商用氮化镓集成功率级器件2010-03-06 1081

全部0条评论

快来发表一下你的评论吧 !