ADS62P19 产品核心信息总结

描述

该ADS62P19是采样率高达250 MSPS的双通道、11位模数转换器(ADC)系列的一部分。该器件在紧凑的QFN-64封装中结合了高动态性能和低功耗。此功能使该器件非常适合多载波、宽带宽通信应用。

该ADS62P19具有增益选项,可用于在较低满量程输入范围内提高无杂散动态范围(SFDR)性能。该器件包括一个直流失调校正环路,可用于消除ADC失调。提供双倍数据速率 (DDR)、低压差分信号 (LVDS) 和并行互补金属氧化物半导体 (CMOS) 数字输出接口。

*附件:ads62p19.pdf

尽管该器件包含内部基准电压源,但取消了传统的基准引脚和相关的去耦电容器。然而,该器件也可以通过外部基准电压源驱动。该器件的额定工作范围为工业温度范围(–40°C 至 +85°C)。

特性

- 最大采样率:250 MSPS

- 11 位分辨率

- 总功率:250 MSPS 时为 1.25 W

- 输出选项:

- DDR LVDS和并行CMOS

- 可编程增益:

- SNR和SFDR权衡高达6 dB

- 直流偏移校正

- 串扰:90 dB

- 支持低至 400 mV 的输入时钟幅度

聚丙烯微分 - 内部和外部基准支持

- 封装:9 毫米× 9 毫米 QFN-64

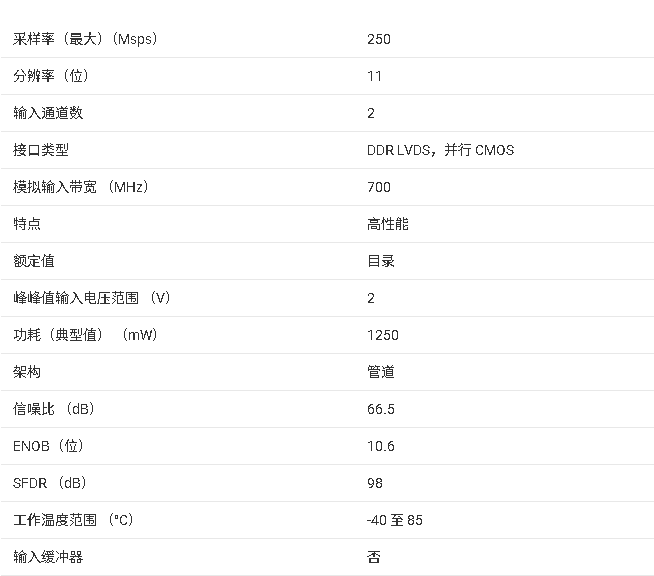

参数

方框图

ADS62P19 是一款双通道 11 位 250 MSPS 模数转换器(ADC),支持 DDR LVDS 与并行 CMOS 双输出接口,具备可编程增益、直流偏移校正及低串扰特性,以高动态性能和紧凑封装适用于多载波宽带通信、测试测量等高速信号采集场景。

核心参数与性能

- 分辨率与线性度 :11 位分辨率,微分非线性(DNL)±0.1 LSB,积分非线性(INL)±2.5 LSB,无丢失码。

- 采样率与输入特性 :最高采样率 250 MSPS(LVDS 接口)、210 MSPS(CMOS 接口);模拟输入带宽 700 MHz,差分输入范围 2 VPP,共模电压 1.5 V。

- 动态性能 :170 MHz 输入时,信噪比(SNR)64 dBFS,无杂散动态范围(SFDR)75 dBc(0 dB 增益)、82 dBc(6 dB 增益);串扰抑制 90 dB,三阶互调失真(IMD3)86.4 dBc。

- 功耗与工作条件 :总功耗 1.25 W(250 MSPS);模拟电源 3.3 V,数字电源 1.8 V;工作温度 -40°C 至 85°C。

封装与引脚

- 采用 9 mm×9 mm 64 引脚 QFN(RGC)封装,底部带热焊盘用于散热,引脚包含模拟 / 数字电源、差分模拟输入(INP_A/INM_A、INP_B/INM_B)、差分时钟输入(CLKP/CLKM)、双路输出接口及配置控制引脚。

- 关键引脚功能:VCM 提供 1.5 V 共模电压,RESET 用于寄存器复位,SEN/SCLK/SDATA 构成串行配置接口,CTRL1-CTRL3 控制掉电模式。

核心功能与特性

- 灵活输出接口 :支持 DDR LVDS(100 Ω 差分终端)与并行 CMOS 输出,数据格式可选二进制补码或偏移二进制,LVDS 模式下单差分对复用两位数据,提升传输效率。

- 增益与偏移校正 :增益 0-6 dB 可编程(0.5 dB 步进),可权衡 SFDR 与 SNR;内置直流偏移校正环路,支持 ±10 mV 偏移补偿,校正时间常数可编程。

- 低功耗与掉电模式 :支持全局掉电(功耗 45 mW)、单通道待机(唤醒时间 1 μs)及低速率自动低功耗模式,适配不同功耗需求场景。

- 配置方式 :支持并行引脚直接配置(接口类型、参考源等)与串行 SPI 配置(增益、偏移、测试模式等),寄存器支持读回验证。

典型应用场景

- 多载波宽带通信系统、软件无线电(SDR)、雷达信号采集、测试测量仪器、有线头端设备。

设计要点

- 电源与去耦 :模拟电源(AVDD)与数字电源(DRVDD)需独立供电,就近配置 0.1 μF 陶瓷去耦电容,敏感电源路径远离数字噪声源。

- 输入与时钟设计 :模拟输入建议串联 5-15 Ω 电阻抑制寄生振荡,采用差分驱动提升抗干扰性;时钟输入支持 LVPECL/LVDS/CMOS 电平,需选用低抖动时钟源(如 CDCE62005),推荐差分驱动。

- 布局规范 :PCB 划分模拟区、数字区与时钟区,单点接地;LVDS 信号线按 100 Ω 阻抗控制、等长差分布线;热焊盘通过过孔充分接地,减少散热瓶颈。

- 配置要点 :上电后需通过 RESET 引脚复位初始化寄存器;串行接口最高 20 MHz 时钟,可配置增益、偏移校正时间常数及输出测试模式(全 0 / 全 1/.toggle 等)。

产品型号与供货

- 在售型号为 ADS62P19IRGCR(2000 片 / 大卷带)与 ADS62P19IRGCT(250 片 / 小卷带),均符合 RoHS 标准,MSL 等级 3(260°C 回流焊,168 小时湿度敏感)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS62PF49 双通道反馈接收器产品总结2025-11-19 807

-

ADS8881 产品核心信息总结2025-11-14 1110

-

ADS1262/ADS1263 产品核心信息总结2025-11-12 1156

-

ADS7046 产品核心信息总结2025-11-06 726

-

更改ads62p49的采样率设置,是只改AD9516给ads62p49的输出时钟就行还是ads62p49的设置也要同步改变?2025-01-10 389

-

ADS62P19输出LVDS数据的疑问求解2025-01-08 374

-

请问ADS62P42IRGCR的IRGCR分别代表什么意思?2024-12-27 308

-

ADS62P19模数转换器(ADC)数据表2024-07-30 469

-

请问ADS62P49EVM是停产了吗?2019-03-04 1424

-

ADS62P49 / ADS62P29/ADS62P48 /2010-06-04 744

全部0条评论

快来发表一下你的评论吧 !