ADS62C17 双通道 11 位 200MSPS 高速模数转换器(ADC)产品手册总结

描述

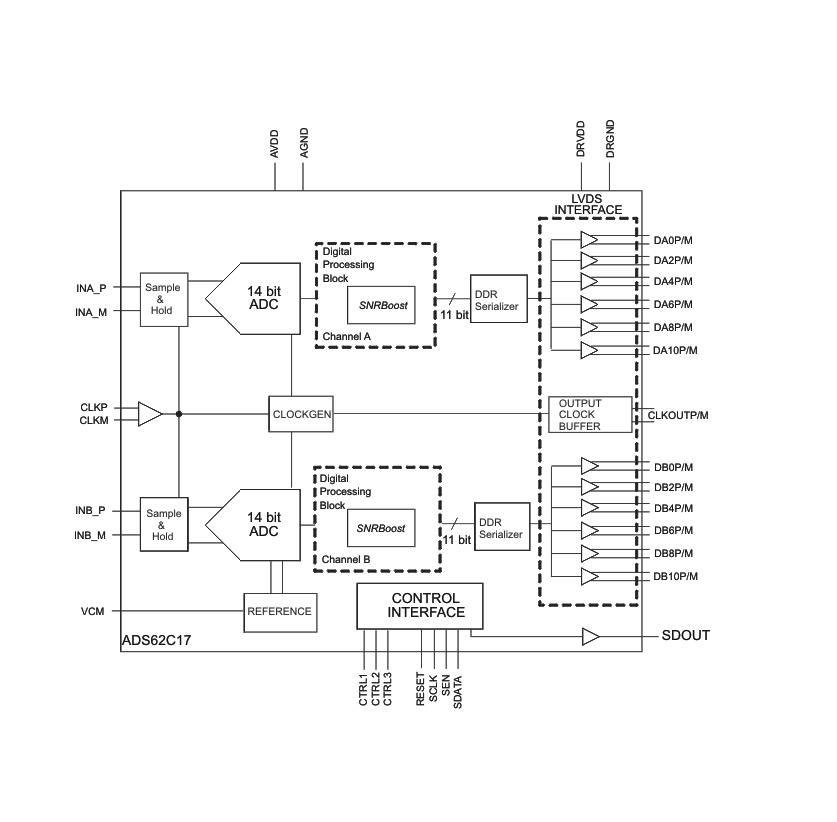

ADS62C17 是一款双通道 11 位、200 MSPS 的 A/D 转换器,结合了高动态性能和低功耗,采用紧凑的 64 QFN 封装。这使得它非常适合多载波宽带通信应用。

ADS62C17采用TI专有的SNRBoost技术,可用于克服因带宽低于奈奎斯特(Fs/2)而产生的量化噪声限制。它包含若干实用且常用的数字功能,如ADC偏移校正、增益(0至6 dB,每步0.5 dB)和增益调谐(以0.001 dB为细步)。

*附件:ads62c17.pdf

增益选项可用于提升SFDR在较低全刻度输入范围的性能。利用增益调谐功能,每个信道的增益可以独立设置,以改善信道间增益匹配。设备还包含直流偏移校正环路,可用于抵消ADC偏移。

同时提供DDR LVDS(双倍数据速率)和并行CMOS数字输出接口。它包含内部参考,而传统的参考引脚和相关的解耦电容已被取消。不过,设备也可以用外部参考驱动。

该装置在工业温度范围内(–40°C至85°C)内规范。

特性

- 最大采样率:200 MSPS

- 11位分辨率且无缺失码

- 在Fin=10 MHz时,90 dBc SFDR

- 采用TI专有SNRBoost技术,实现79.8 dBFS SNR,125 MHz中频,20 MHz BW

频段 - 总功率:1.1瓦,功率200 MSPS

- 90 dB 串扰

- 双数据速率(DDR)LVDS和并行

CMOS输出选项 - 可编程增益最高可达6dB,用于信噪比/SFDR权衡

- 直流偏移校正

- 增益调谐能力以细步(0.001 dB)

实现信道间增益匹配 - 支持输入时钟幅度,最低可达

400 mV p-p差动 - 内部与外部参考支持

- 64-QFN封装(9毫米×9毫米)

参数

方框图

一、产品核心概述

ADS62C17 是德州仪器推出的高速高精度双通道 ADC,核心优势为高采样率、低功耗与灵活信号调理能力。产品分辨率达 11 位无丢失码,最高采样率 200MSPS,工作温度范围 -40°C85°C,采用 64-QFN 封装(9mm×9mm),模拟供电 3.15V3.8V、数字供电 1.7V~1.9V,集成 SNRBoost 降噪技术、可编程增益与偏移校正功能,适用于多载波通信、宽带信号采集、工业控制等高速数据采集场景。

二、关键特性与规格

1. 核心性能参数

- 分辨率与线性度 :11 位无丢失码,微分非线性(DNL)±0.6LSB,积分非线性(INL)±2.5LSB;偏移误差 ±20mV,偏移漂移 0.02mV/°C,增益漂移 0.002%/°C。

- 动态性能:10MHz 输入时无杂散动态范围(SFDR)90dBc,125MHz 中频(20MHz 带宽)下 SNR 79.8dBFS;交叉串扰 90dB,互调失真(IMD3)87dBFS,孔径抖动 145fs rms。

- 输入与参考:双通道差分输入,满量程输入范围 2Vpp(0dB 增益),模拟输入带宽 700MHz;支持内部 / 外部参考,内部参考无需外接解耦电容,外部参考通过 VCM 引脚配置。

- 功耗与输出:200MSPS 时总功耗 1.1W,掉电模式功耗 45~75mW;支持 DDR LVDS 与并行 CMOS 输出,数据格式为偏移二进制或二进制补码。

2. 核心功能

- SNRBoost 降噪技术:针对亚奈奎斯特带宽优化,可提升 SNR 最高 12dB(5MHz 带宽时),通过编程系数定位降噪频段,不影响谐波性能。

- 可编程增益与增益匹配:增益 0~6dB 可调(0.5dB 步进),支持 0.001dB 精细增益调整,实现通道间增益匹配,适配 SNR 与 SFDR 权衡需求。

- 偏移校正:内置直流偏移校正环路,可校正 ±10mV 偏移,校正时间常数 256k~512M 时钟周期可编程,不影响信号相位。

- 多工作模式:支持全局掉电、通道待机、输出缓冲禁用等低功耗模式;支持通道独立控制与数据多路复用(MUX)模式,灵活适配单 / 双通道应用。

三、封装与引脚

1. 封装信息

- 64-QFN 封装:引脚间距 0.5mm,外露热焊盘接 DRGND 优化散热;MSL 等级 3,支持 260°C 回流焊,符合 RoHS 标准,ESD 防护等级 2kV(人体模型)。

2. 关键引脚功能

- 电源与地:AVDD/AGND(模拟供电 / 地)、DRVDD/DRGND(数字供电 / 地),需就近并联 0.1μF 陶瓷电容去耦。

- 输入与参考:INP_A/INM_A、INP_B/INM_B(双通道差分输入);VCM(内部参考模式下为共模电压输出,外部参考模式下为参考输入)。

- 控制与输出:CLKP/CLKM(差分时钟输入)、CLKOUTP/CLKOUTM(输出时钟);DAxP/DAxM、DBxP/DBxM(LVDS 数据输出)或 DA0

DA10、DB0DB10(CMOS 数据输出)。 - 配置引脚:RESET(复位)、SCLK/SDATA/SEN(串行配置接口)、CTRL1~CTRL3(并行控制 SNRBoost 与功耗模式)。

四、工作模式与核心功能

1. 核心工作模式

- 采样模式:双通道同步采样,采样率 1MSPS~200MSPS 可调,支持低速模式(≤100MSPS)优化时序。

- 输出模式:DDR LVDS 模式下每对差分引脚传输 2 位数据(时钟上升 / 下降沿采样),并行 CMOS 模式支持 150MSPS 以下时钟同步采样,150MSPS 以上建议外部时钟捕获。

- 低功耗模式:全局掉电(核心与参考均关闭)、通道待机(参考保持激活,唤醒时间 1μs)、输出缓冲禁用(唤醒时间 100ns)。

2. 关键功能

- 灵活信号调理:通过编程增益(0~6dB) trade-off SNR 与 SFDR,高增益模式可提升高频输入时的 SFDR 性能;偏移校正功能可动态抵消系统偏移,支持添加 ±32LSB 偏移基座。

- 时钟与输入驱动:支持差分(正弦波、LVPECL、LVDS)或单端(LVCMOS)时钟输入,时钟幅度最低 400mVpp;模拟输入需偏置在 1.5V 共模电压,建议差分驱动以提升抗干扰能力。

- 串行 / 并行配置:支持串行寄存器编程(20MHz 最高时钟)与并行引脚控制,可独立配置通道增益、降噪模式、输出格式等参数,寄存器支持读回验证。

五、应用场景与设计支持

1. 典型应用

- 高速信号采集:宽带射频(RF)信号采集、雷达与卫星通信接收端、示波器等测试仪器。

- 工业与通信:多载波通信系统、电力线监测、高速数据采集卡(DAQ)、工业自动化高速传感。

2. 设计资源

- 电源与去耦:模拟与数字电源独立布线,电源引脚就近放置 0.1μF 陶瓷电容,嘈杂环境可添加 10μF 钽电容;模拟地与数字地单点共地,外露热焊盘必须接地。

- 布局要点:模拟输入走线短且远离数字信号线,输入引脚串联 5~15Ω 电阻抑制寄生振荡;LVDS 输出建议 100Ω 差分端接,CMOS 输出控制负载电容 ≤5pF。

- 输入驱动:低带宽场景(<100MHz)采用 R-C-R 滤波电路吸收采样毛刺,高带宽场景(>300MHz)使用传输线变压器驱动,确保输入阻抗匹配。

- 参考设计:内部参考模式下 VCM 引脚输出 1.5V 共模电压,需并联 0.1μF 滤波电容;外部参考模式下通过 VCM 引脚设定参考电压,满量程输入范围为 VCM×1.33。

六、可靠性与订单信息

- 可靠性保障:绝对最大额定值:AVDD 3.9V,引脚电压 -0.3V~AVDD+0.3V,结温 125°C,符合工业级可靠性标准。

- 可订购型号:ADS62C17IRGCR(卷盘装 2000 片)、ADS62C17IRGCT(小卷盘装 250 片),引脚镀层 NIPDAU,MSL 等级 3(260°C 回流焊,168 小时防潮)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS62C15:高性能双通道11位ADC的深度解析2025-11-26 525

-

ADS5296A、4通道200MSPS和8通道80MSPS模数转换器2024-12-10 375

-

ADS8363双通道、16位、1 MSPS模数转换器(ADC)数据表2024-07-30 945

-

ADS5553高性能、双通道、14位、65 MSPS模数转换器(ADC)数据表2024-07-27 631

-

ADS62P15双通道11位模数转换器数据表2024-07-19 405

-

ADS58C28双通道、11位模数转换器(ADC)数据表2024-07-17 519

-

AD9608:10位、125/105 MSPS、1.8 V双通道模数转换器(ADC)2021-03-22 1206

-

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V双通道模数转换器(ADC)2021-03-21 1324

-

了解 ADS62C17 数据转换器的转换过程2018-06-13 4017

-

具有SNRBOST的双通道11位200MSPS模数转换器的详细资料免费下载2018-05-16 885

-

ADS5485 采样率200MSPS 16位单通道模数转换器2008-09-25 2175

全部0条评论

快来发表一下你的评论吧 !