Cadence工具如何解决芯粒设计中的信号完整性挑战

描述

本文翻译转载于:Cadence Blog

作者:Sigrity

在芯粒设计中,维持良好的信号完整性是最关键的考量因素之一。随着芯片制造商不断突破性能与微型化的极限,确保组件间信号的纯净性与可靠性面临着前所未有的巨大挑战。对于需要应对信号完整性与电源完整性复杂问题的工程师而言,深入理解这些挑战的细微差异,是设计出高效、可靠芯粒方案的核心前提。

阅读全文,可详细了解芯粒中的信号完整性及其在芯片设计中的关键作用、芯粒技术带来的独特挑战,以及 Cadence 的先进工具如何为工程师重新定义设计可能性。

理解芯粒中的信号完整性

信号完整性指的是电信号在系统组件间传输时的质量。对于集成电路封装设计和印刷电路板而言,维持信号完整性意味着确保信号不受噪声、反射、串扰和损耗的影响而发生劣化。

芯粒使这一过程变得更为复杂。传统的单芯片将所有组件集成在单一裸片上,而芯粒则是尺寸更小、单独制造的组件,通过互联形成集成系统。尽管这种模块化方案具有显著的可扩展性和灵活性,但也带来了新的信号完整性问题。

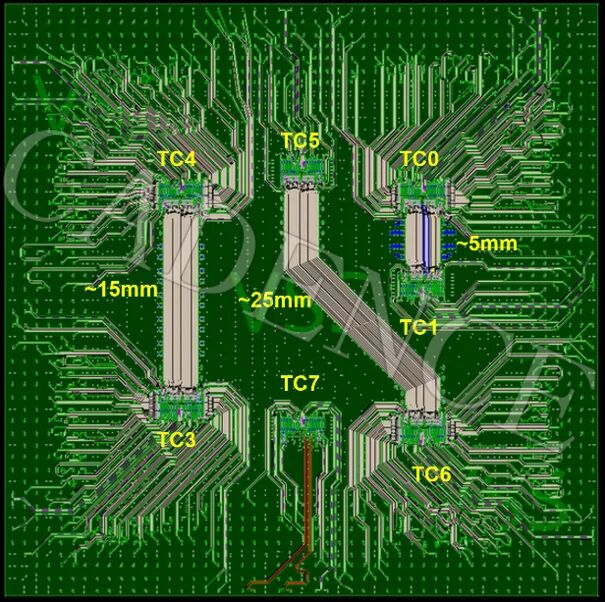

图 1:包含三条不同长度芯粒间链路的 UCIe 测试封装

为什么信号完整性至关重要

保持可靠的信号传输是芯片性能的关键要素,因为即便信号质量出现微小偏差,都可能影响性能、增加功耗并降低可靠性。确保信号完整性不仅能保证高性能,还能保障芯片设计的可靠性与能效。

芯粒设计中的信号完整性挑战

热与电耦合:鉴于芯粒的高度集成特性,组件间的热电交互成为维持电源完整性和信号完整性的重要考量因素。

高速数据传输:现代应用(如 AI 工作负载或高带宽数据中心运算)的复杂性日益提升,对数据传输速率提出了更高要求。尤其在高频场景下,信号路径中的损耗与反射问题会更为显著。

互连密度:为优化性能,芯粒间的互连必须高度密集排列,这会增加串扰(相邻线路的信号干扰)和电磁耦合的风险。

复杂封装:芯粒通常需要 2.5D 或 3D 集成等先进封装技术,这类封装方案的设计更为紧凑,进一步加剧了信号劣化的风险。

电源传输噪声:芯粒复杂的电源传输网络(PDN)可能向系统引入噪声,影响信号完整性与电源完整性。确保低阻抗的电源传输路径,是避免干扰的关键。

应对信号完整性问题的解决工具

应对这些挑战需要借助能够进行全面信号完整性分析的先进技术与工具。因此,工程师们常选用行业领先的解决方案,例如 Cadence 的 Sigrity X 和 Clarity 3D Solver 平台。

Sigrity X

Cadence 的 Sigrity X 信号完整性分析技术采用集成化的强大方案,可应对信号完整性与电源完整性挑战,其核心功能包括:

端到端的信号完整性与电源完整性(SI/PI)分析,能在印刷电路板和集成电路封装设计中实现精细化、电源感知的信号完整性及电源传输网络分析。该功能有助于及早识别潜在问题,确保达成成本、性能与可靠性目标。

先进的设计内互连建模,可模拟信号路径并优化阻抗,从而减少反射与损耗,对于芯粒特有的高密度布局设计也同样适用。

串扰分析功能,通过评估和抑制高密度互连中的串扰,最大限度降低干扰风险。

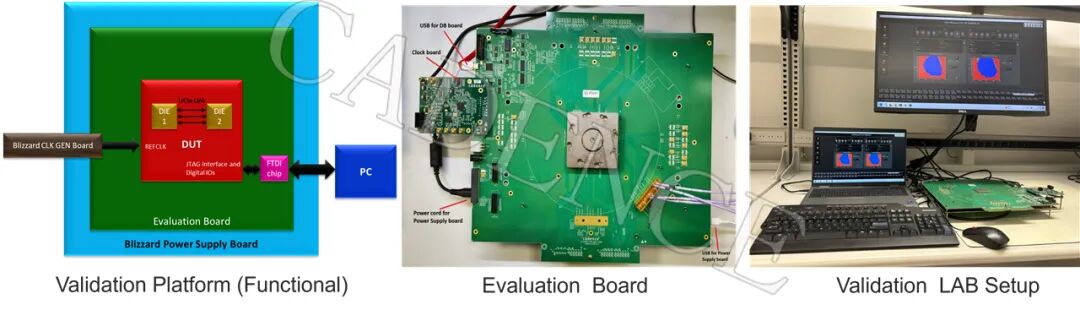

图 2:Cadence UCIe-Link【IP + 封装】芯粒间验证平台,用于关联 Sigrity X 信号完整性仿真结果

Clarity 3D Solver

Cadence 的 Clarity 3D Solver 专为高保真度分析设计,通过提供针对硅片、封装和印刷电路板的 3D 电磁提取能力,与 Sigrity X 的信号完整性/电源完整性(SI/PI)分析形成互补。其优势包括:

可分析堆叠封装或 2.5D/3D 设计中的耦合效应、热问题及电磁场(EM)行为。

Clarity 3D Solver 与 Cadence 设计生态系统的无缝集成,使团队能在统一高效的环境中协作。该工具提供宏观与微观双重视角以应对信号相关挑战,助力在紧张的进度内完成高性能设计。

增强芯粒信号完整性强化技巧

除工具外,采用最佳实践也能显著提升信号完整性的维持能力。以下是可采取的具体措施:

采用电源感知设计:利用电源感知型信号完整性分析,考量同步开关噪声(SSN),确保电源传输网络的稳健性。

优化互连阻抗:在整个信号路径中保持受控阻抗,以减少反射并将信号损耗降至最低。

注重布局与布线技巧:遵循印刷电路板(PCB)布局的最佳实践,例如缩短 stub 长度、合理使用去耦元件、将敏感走线与强干扰信号分离,从而抑制串扰并减少噪声传播。

尽早且频繁仿真:在设计流程的每个阶段对潜在的信号完整性与电源完整性问题进行仿真,以便及早发现并解决问题。

采用先进封装技术:扇出型晶圆级封装(FOWLP)、具有严格控制设计参数的中介层等解决方案,有助于确保电热稳定性。

信号完整性带来的竞争优势

芯粒的信号完整性不仅是一项技术挑战,更蕴藏着发展机遇。通过主动掌控这些复杂性,你能够实现系统的更高性能、更快上市速度和更强可扩展性。 Cadence 的 Sigrity X 与 Clarity 等工具为你提供有力支持,助你从容应对芯粒设计的复杂难题,同时确保方案的稳健性与可靠性。

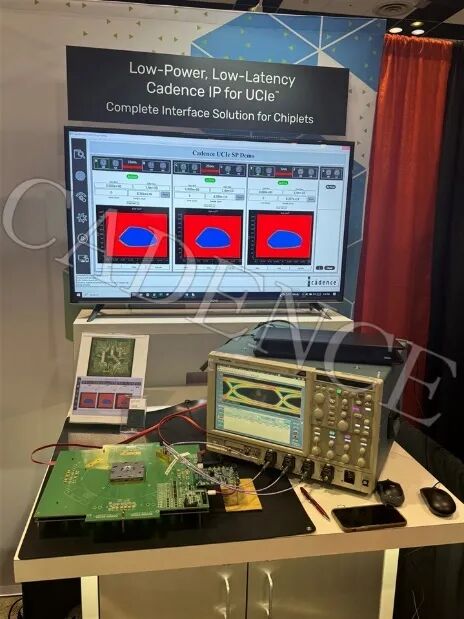

图 3:Cadence UCIe-Link【IP + 封装】芯粒间信号质量演示

了解更多关于信号完整性的信息

如需深入了解 Cadence 如何帮助工程师解决最复杂的信号完整性挑战,可访问 Cadence 官网网站浏览。Cadence Sigrity X 信号与电源完整性页面请点击“阅读原文”进行了解。

© 2025 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。

-

如何解決信号完整性问题2024-12-25 3339

-

听懂什么是信号完整性2024-12-15 1385

-

高速电路中的信号完整性和电源完整性研究2024-09-25 489

-

何为信号完整性?信号完整性包含哪些2021-12-30 2874

-

信号完整性对EMC的影响有哪些2020-07-09 4445

-

如何在不知情的情况下解决信号完整性设计问题2019-10-29 3501

-

基于Cadence的信号和电源完整性设计与分析2019-09-01 7091

-

利用Cadence Allegro进行PCB级的信号完整性仿真2017-01-12 1818

-

关于信号完整性的问题2016-08-12 2172

-

利用Cadence工具进行板级电路信号完整性仿真2016-02-22 1100

-

信号完整性分析2015-11-10 1069

-

在高速设计中,如何解决信号的完整性问题?2010-01-02 1385

-

信号完整性原理分析2009-11-04 1287

-

信号完整性分析与设计2009-09-12 58812

全部0条评论

快来发表一下你的评论吧 !