AI算力机架电源架构、拓扑演进与碳化硅MOSFET的应用价值深度研究报告

电子说

描述

AI算力基础设施的能源变革:高功率密度集成机架电源架构、拓扑演进与碳化硅MOSFET的应用价值深度研究报告

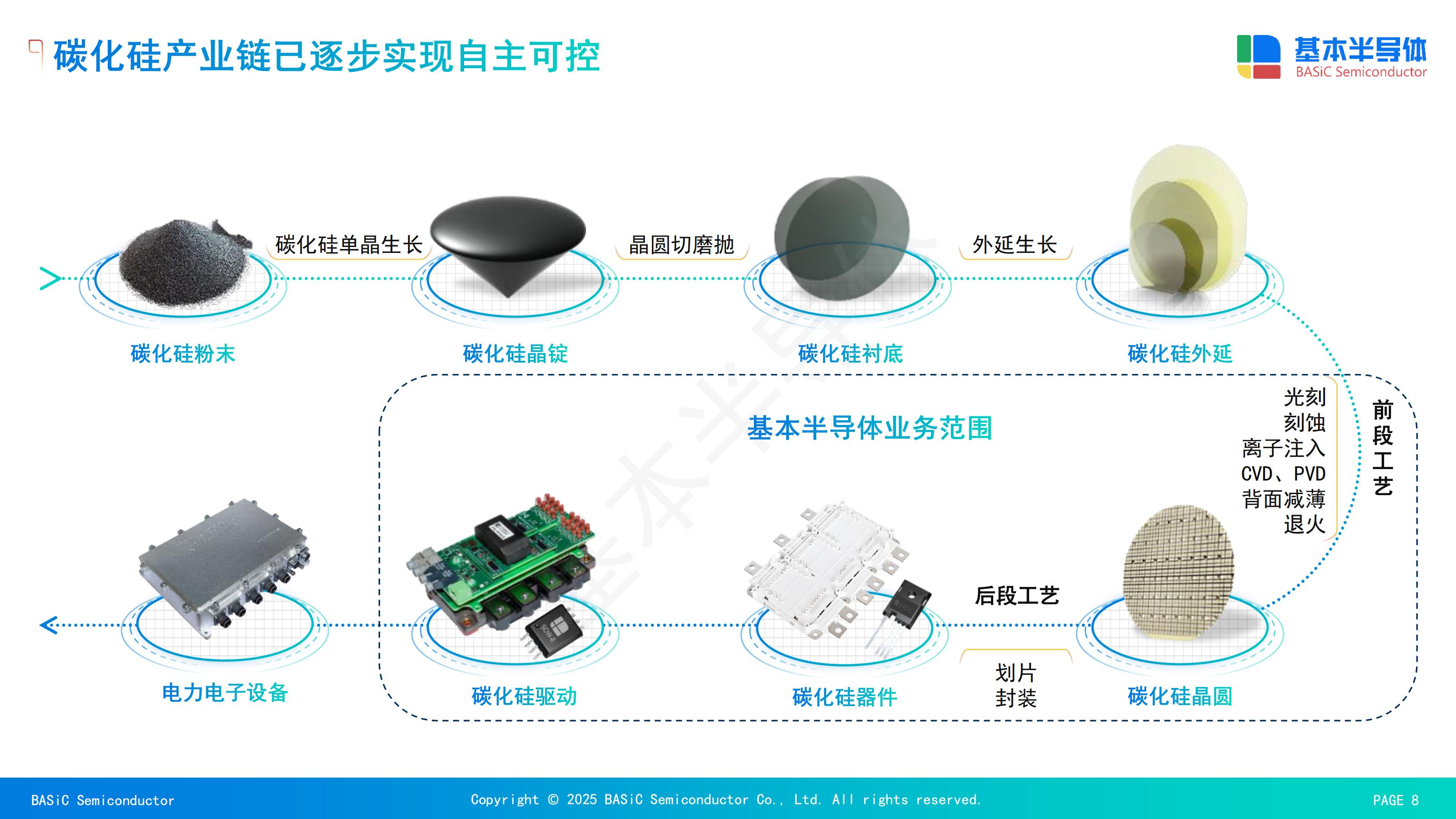

BASiC Semiconductor基本半导体一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 执行摘要

随着以ChatGPT、Sora为代表的生成式人工智能(Generative AI)和大语言模型(LLM)的爆发式增长,全球数据中心的算力需求正经历着前所未有的指数级跃升。这一趋势不仅重塑了计算芯片的设计逻辑,更对底层能源基础设施提出了严苛的物理挑战。当单颗GPU加速器的热设计功耗(TDP)突破1000瓦,单机架功率密度从传统的10kW飙升至120kW甚至更高时,传统的分布式电源架构已难以为继。

倾佳电子全面剖析面向AI算力服务器的高功率密度电源系统——特别是符合Open Compute Project (OCP) Open Rack v3 (ORv3) 标准的集成机架式电源架构。我们将深入探讨从传统的12V分布式供电向48V集中式母线架构的范式转移,并解析支撑这一变革的核心电路拓扑:无桥图腾柱功率因数校正(Totem-Pole PFC)与高频LLC谐振变换器。

在这一技术演进中,宽禁带(WBG)半导体,尤其是碳化硅(SiC)MOSFET,扮演了决定性的赋能者角色。基于基本半导体(BASIC Semiconductor)等厂商的最新器件规格,本报告将量化分析SiC MOSFET在降低开关损耗、提升热管理效率以及应对高压直流(HVDC)趋势中的独特价值。结合先进的顶部散热(Top-Side Cooling, TSC)封装技术与液冷生态系统的融合,我们描绘了一幅通往每立方英寸100瓦(100 W/in³)以上超高功率密度电源的演进路线图。

2. AI算力时代的能源挑战与架构重构

2.1 算力摩尔定律的失效与功率密度的爆发

在过去十年中,摩尔定律主要关注晶体管密度的增加,但在AI时代,"黄氏定律"(Huang’s Law)即GPU性能的提升速度已远远超过通用CPU。NVIDIA DGX H100系统的发布标志着单节点功耗正式迈入10kW量级,而随后的GB200 NVL72机架级系统更是将这一数字推向了120kW的惊人高度 。

这种数量级的跨越导致了传统数据中心供电设计的全面失效。在传统的12V供电架构下,若要为一个120kW的机架供电,其总线电流将高达10,000安培。这不仅需要如同手臂般粗细的铜排来承载电流,其产生的I2R传输损耗也将达到不可接受的程度 。因此,行业正经历一场从服务器级电源向机架级电源(Power Shelf)的彻底转型,电压等级也无可挽回地从12V转向48V/54V,并正在向800V HVDC演进。

2.2 Open Rack v3 (ORv3):高密度供电的标准化基石

为了应对超大规模计算的能效挑战,Open Compute Project (OCP) 制定了Open Rack v3标准,重新定义了机架内的电力分配方式。ORv3摒弃了传统的内置于服务器机箱内的CRPS(Common Redundant Power Supply)电源,转而采用集中式的电源架(Power Shelf) 。

2.2.1 集中式电源架架构优势

ORv3电源架设计为1OU高度,通常包含6个热插拔整流模块(PSU),通过背部的汇流排(Busbar)直接向整个机架输送48V/50V直流电。这种架构带来了多重优势:

空间优化: 将AC/DC转换从计算节点中剥离,使得服务器机箱(Compute Tray)能容纳更多的GPU和散热组件 。

转换效率提升: 48V母线相比12V母线,电流减少了4倍,传输损耗理论上降低了16倍(Ploss∝I2)。这使得整个机架的端到端效率提升了10%至15% 。

弹性的冗余配置: 集中式电源允许在机架层面实现N+1或N+N冗余,相比于每台服务器都要配置1+1冗余电源,大幅减少了闲置的电源容量,提高了电源利用率(Stranded Capacity) 。

2.2.2 严苛的能效与动态响应指标

ORv3标准对电源模块的效率提出了极高要求,通常要求满足或超越80 PLUS Titanium标准:

峰值效率: 在50%负载下必须超过97.5%。

满载效率: 在100%负载下必须超过96.5%。

轻载效率: 即便在10%的低负载下,也要求效率高于94% 7。

此外,AI训练负载具有极端的动态特性。GPU在进行大规模矩阵运算时,会在微秒级时间内产生巨大的电流瞬变(di/dt)。ORv3电源必须具备极快的动态响应能力,以维持48V母线的电压稳定,防止系统掉电或重启。这对电源内部的控制环路带宽和功率器件的开关速度提出了严峻考验。

2.3 集成电池备份单元(BBU)的兴起

为了应对电网波动和削峰填谷(Peak Shaving)的需求,ORv3架构引入了集成的电池备份单元(BBU)架。这些BBU模块直接挂载在48V母线上,当AC输入中断或瞬时负载超过电源架能力时,BBU会无缝介入供电 。

这引入了双向DC-DC变换的需求。在正常运行时,电源架为BBU充电(Buck模式);在掉电时,BBU向母线放电(Boost模式)。这种双向能量流动的需求,使得具备低导通电阻和双向导通特性的同步整流MOSFET成为了唯一选择。

3. 高功率密度电源拓扑架构的演进

要实现ORv3所要求的97.5%以上效率和100 W/in³以上的功率密度,传统的电路拓扑已经触及了物理天花板。基于硅(Si)器件的传统PFC(如交错并联Boost PFC)受限于二极管整流桥的导通损耗和硅MOSFET的反向恢复损耗,已无法满足AI服务器电源的需求。

3.1 AC/DC级:图腾柱PFC(Totem-Pole PFC)的统治地位

图腾柱PFC拓扑消除了传统Boost PFC前端的整流二极管桥,从而消除了两个二极管压降带来的显著导通损耗。在3kW以上的应用中,这部分损耗可占总损耗的20%以上。

3.1.1 连续导通模式(CCM)的关键挑战

图腾柱PFC分为慢速桥臂(Line Frequency Leg)和快速桥臂(High Frequency Leg)。慢速桥臂以工频(50/60Hz)切换,负责整流;快速桥臂以高频(65kHz-150kHz)切换,负责功率因数校正。

在**连续导通模式(CCM)**下,当主开关管开通时,续流管的体二极管会被强制反向恢复。对于传统的硅超结(Superjunction)MOSFET,其体二极管的反向恢复电荷(Qrr)非常大,导致巨大的反向恢复电流和开关损耗,甚至可能导致器件失效。这使得硅MOSFET几乎无法用于CCM模式的图腾柱PFC 。

3.1.2 碳化硅(SiC)的破局

SiC MOSFET的体二极管具有极低的反向恢复电荷(Qrr),通常仅为同规格硅器件的1/10甚至更低。例如,基本半导体(BASIC Semiconductor) 的 B3M025075Z(750V SiC MOSFET)在测试条件下表现出优异的反向恢复特性,能够承受硬开关(Hard Switching)带来的应力 。这使得图腾柱PFC能够工作在CCM模式下,从而在保持低纹波电流的同时,大幅提升效率并减小电感体积。

3.1.3 交错并联技术的应用

为了进一步提升功率密度并分散热量,5.5kW及以上的电源模块通常采用**交错并联(Interleaved)**的图腾柱PFC架构。通过将两个或多个快速桥臂并联并错相运行(如180度相位差),可以大幅抵消输入电流纹波,减小EMI滤波器的体积,并分散功率器件的热应力 。基本半导体的 B3M040065B(650V, 40mΩ)等器件非常适合此类应用,其紧凑的TOLT封装允许在PCB上高密度布置多个并联支路 。

3.2 DC/DC级:LLC谐振变换器的高频化

在PFC之后,DC/DC级负责将400V直流母线电压隔离降压至48V。全桥LLC谐振变换器因其能在全负载范围内实现原边零电压开通(ZVS)和副边零电流关断(ZCS)而成为主流选择。

3.2.1 开关频率与功率密度的博弈

为了缩小变压器和谐振电容的体积,设计者不断推高开关频率(从100kHz向500kHz甚至更高迈进)。然而,频率的提升受到MOSFET输出电容(Coss)和关断损耗(Eoff)的制约。

SiC MOSFET相比硅基器件,具有更低的Coss及更线性的电容特性,这使得实现ZVS所需的死区时间更短,励磁电流更小,从而提升了循环效率。基本半导体的 B3M040065L 在400V时的Eoss仅为12 μJ ,这对于提升轻载效率至关重要,有助于满足ORv3对轻载效率的严苛要求。

3.2.2 三相交错LLC架构

针对8kW及以上的高功率模块,单路LLC的电流应力过大。三相交错LLC架构(3-Phase Interleaved LLC)通过三个错相120度的LLC单元并联,不仅分摊了电流,还使得输出纹波频率提高至开关频率的6倍,极大地减小了输出滤波电容的体积,这对于空间受限的1OU电源架至关重要 。

3.3 混合控制策略:TCM与CCM的融合

为了追求极致效率(>98%),控制策略也在进化。三角电流模式(TCM)可以实现软开关(ZVS),消除开通损耗,但其变频特性导致EMI滤波器设计困难且峰值电流大。最新的AI服务器电源设计倾向于采用混合控制策略:在轻载时采用TCM以消除开关损耗,在重载时切换至CCM以降低导通损耗和电流应力。SiC MOSFET凭借其在宽频率和宽电流范围内的稳健性,完美适配这种复杂的混合控制模式 。

4. 碳化硅MOSFET在AI电源中的核心应用价值

在AI服务器电源这场追求极致效率与密度的竞赛中,碳化硅(SiC)MOSFET并非仅仅是硅的替代品,它是实现下一代架构的物理基础。

4.1 材料物理特性的降维打击

SiC作为第三代宽禁带半导体,其带隙宽度(~3.26 eV)是硅(1.12 eV)的3倍,临界击穿电场是硅的10倍 。这些物理特性转化为具体的器件优势:

更薄的漂移层: 在相同的耐压等级下,SiC的漂移层厚度仅为硅的1/10,从而大幅降低了比导通电阻(Ron,sp)。这意味着在相同的芯片面积下,SiC MOSFET拥有更低的导通损耗。

更高的热导率: SiC的热导率(~3.7 W/cm·K)是硅的3倍,使得器件在相同损耗下结温更低,或者在相同结温下能承受更大的功率密度 。

4.2 针对AI负载特性的性能优势

4.2.1 高温下的导通电阻稳定性

AI服务器通常运行在高负荷状态,电源模块内部环境温度极高。硅超结MOSFET的导通电阻(RDS(on))具有很高的正温度系数,在150°C时,其阻值通常会翻倍(增加约2.5-3倍)。这会导致热失控的风险,迫使设计者大幅降额使用。

相比之下,SiC MOSFET的RDS(on)随温度变化非常平缓。以 基本半导体 B3M025065Z 为例,其RDS(on)在高温下的增幅远小于硅器件 。这意味着在高温满载工况下,SiC的实际导通损耗远低于硅,从而提升了系统的热稳定性及实际可用容量。

4.2.2 极低的反向恢复电荷(Qrr)

如前所述,图腾柱PFC的高效运行依赖于开关管体二极管的性能。基本半导体 B3M011C120Z(1200V SiC MOSFET)具有极低的反向恢复电荷 14,这在380V/400V高压直流或三相交流输入的应用中至关重要。低Qrr直接消除了硬开关过程中的巨大电流尖峰,不仅降低了损耗,更大幅减少了高频噪声(EMI),简化了滤波电路设计。

4.2.3 提升开关频率,缩小体积

SiC MOSFET能够以数倍于硅IGBT或MOSFET的频率开关而不会产生过热。在AI服务器电源中,这意味着可以将开关频率从传统的65kHz提升至140kHz-300kHz 。频率的提升直接导致了磁性元件(PFC电感、LLC变压器)体积的显著缩小,这是实现ORv3电源架33kW高功率密度的关键因素。

4.3 电压等级的选择与可靠性裕量

4.3.1 650V vs 750V:可靠性的博弈

在400V直流母线应用中,传统的650V器件虽然理论上够用,但在电网波动或雷击浪涌等极端工况下,电压裕量(Headroom)较小。此外,宇宙射线(Cosmic Ray)诱发的单粒子烧毁(SEB)效应在高压偏置下会显著增加故障率(FIT Rate)。

为了提高超大规模数据中心的可靠性,行业趋势正在向750V器件迁移。基本半导体 B3M010C075Z(750V, 10mΩ)提供了额外的100V耐压裕量 。这不仅增强了抗浪涌能力,更重要的是,在相同的400V工作电压下,750V器件对宇宙射线的免疫力呈指数级提升,极大地降低了随机失效的概率 。

4.3.2 1200V:面向未来的800V架构

随着NVIDIA等厂商推动800V HVDC架构,1200V SiC MOSFET成为必须。B3M011C120Z 提供了1200V的耐压和223A的通流能力 ,使其成为三相480V输入PFC或直接800V母线转换器的理想选择。在这些高压应用中,SiC相比于1200V硅IGBT,完全消除了拖尾电流(Tail Current),将开关损耗降低了80%以上。

5. 封装技术的革新与热管理

仅仅依靠芯片层面的改进不足以解决100kW+机架的散热问题。封装技术的创新是释放SiC潜能、实现高功率密度的最后一块拼图。

5.1 顶部散热(Top-Side Cooling, TSC)的崛起

传统的SMD封装(如D2PAK)将热量通过底部焊盘传导至PCB。然而,FR4 PCB的热导率极低(~0.3 W/m·K),即使添加大量热过孔,PCB本身也成为了散热瓶颈。

为了打破这一瓶颈,基本半导体推出了采用 QDPAK 和 TOLT 封装的SiC MOSFET,如 AB3M025065CQ和 B3M025065B 。

结构原理: TSC封装将散热焊盘(Drain Pad)置于器件顶部,直接暴露于空气中。

热路径优化: 散热器或冷板可以直接压在器件表面,热量无需经过PCB,热阻(RthJC)大幅降低。例如,AB3M025065CQ的结到壳热阻极低,仅为0.35 K/W 。

电气优势: 由于底部不再需要散热焊盘,PCB底部的空间被释放出来用于布线或放置其他器件,进一步提升了板级功率密度。此外,TSC封装通常配备Kelvin Source引脚,解耦了栅极驱动回路与功率回路,消除了源极电感对开关速度的限制。

5.2 液冷技术的深度融合

GB200 NVL72等AI机架已经全面拥抱液冷技术。ORv3电源架的设计也必须融入这一生态。

冷板集成: 采用QDPAK/TOLT封装的SiC MOSFET提供了平整的顶部表面,非常适合与液冷冷板(Cold Plate)贴合。通过高性能导热界面材料(TIM),冷板可以直接带走功率器件产生的热量。

去风扇化: 液冷的高效散热使得电源模块内部的风扇可以被移除或减小,这不仅消除了风扇带来的寄生功耗(可占电源总功耗的3-5%)和振动(对机械硬盘有害),还大幅提升了系统的平均无故障时间(MTBF)。

盲插流体连接器: 电源模块与机架流体分配单元(Manifold)之间采用盲插、无滴漏的快速连接器(Quick Disconnects),实现了电源模块的液冷热插拔维护 。

6. 集成机架式电源系统架构详解

6.1 NVIDIA GB200 NVL72 供电架构案例

以目前最先进的NVIDIA GB200 NVL72为例,其供电架构代表了未来的主流方向 :

总功耗: 单机架约120kW。

电源架配置: 一个机架包含6到8个电源架(Power Shelf),每个电源架额定功率33kW。

电源模块(PSU): 每个电源架容纳6个5.5kW的整流模块,采用N+N或N+1冗余配置。这意味着整个机架可能包含多达48个高功率SiC电源模块。

输入电源: 采用三相415 VAC直接输入到电源架,消除了机架级PDU的中间环节。

直流母线: 电源架输出48V/50V直流电,通过巨大的铜排(Busbar)传输至后方的计算托盘(Compute Tray)。

6.2 48V母线的必然性与挑战

为何选择48V而非12V或更高的400V?

对比12V: 48V降低了电流和损耗,使得120kW的功率传输在物理上成为可能。

对比400V: 48V(<60V)属于安全特低电压(SELV),是非绝缘电路,维护更加安全,且允许在服务器主板上使用更小间距的布线,有利于高密度计算芯片的布局。

中间总线转换(IBC): 计算托盘上需要高效的IBC模块将48V转换为12V或直接转换为GPU所需的低压大电流(<1V, >1000A)。这一级转换同样大量采用GaN或低压SiC器件以维持高效率。

7. 迈向800V HVDC

尽管48V架构解决了当前的燃眉之急,但随着机架功率向1MW迈进(如NVIDIA未来的GB300规划),48V母线所需的铜排重量将达到数百公斤,物理连接将变得极其困难 。

7.1 800V HVDC 直供技术

未来的AI工厂将趋向于800V HVDC架构:

电网直连: 采用固态变压器(SST)将中压交流电(13.8kV)直接转换为800V直流电。

机架内传输: 800V直流电直接进入机架,消除了传统的AC/DC电源架,取而代之的是机架内的DC/DC转换模块。

SiC的终极舞台: 在800V架构中,1200V和1700V的SiC MOSFET将成为绝对主角。它们需要承受更高的电压应力,同时保持高频开关以缩小隔离变压器的体积。基本半导体的 B3M011C120Z 等1200V产品线正是为这一趋势做好了技术储备 。

8. 结论

AI算力需求的爆发正在倒逼数据中心能源基础设施进行一场彻底的革命。从服务器电源到机架式电源架,从12V到48V再到未来的800V,每一次电压等级和拓扑架构的跃迁,其核心驱动力都是对功率密度和能源效率的极致追求。

在这一变革中,碳化硅(SiC)MOSFET凭借其无与伦比的开关特性、耐高压能力和热导率,成为了不可或缺的技术基石。

拓扑赋能: SiC使得图腾柱PFC等高效硬开关拓扑成为现实,将AC/DC级效率推向99%的极限。

密度提升: 通过支持高频开关,SiC大幅减小了磁性元件体积;通过高温低阻特性,减小了散热需求。

封装协同: 结合QDPAK、TOLT等顶部散热封装,SiC完美融入了AI时代的液冷生态系统。

对于数据中心运营商和电源制造商而言,尽早布局基于750V/1200V SiC MOSFET的高密度电源方案,不仅是满足ORv3标准的合规需求,更是赢得AI算力军备竞赛能源入场券的关键战略。

表 1:基本半导体 SiC MOSFET 规格对比及其在 AI 电源中的应用

| 参数 | B3M025065B | AB3M025065CQ | B3M010C075Z | B3M011C120Z |

|---|---|---|---|---|

| 电压等级 (VDS) | 650 V | 650 V | 750 V | 1200 V |

| 电流 (ID @ 25°C) | 108 A | 115 A | 240 A | 223 A |

| 典型导通电阻 (RDS(on) 18V) | 25 mΩ | 25 mΩ | 10 mΩ | 11 mΩ |

| 封装形式 | TOLT (顶部散热) | QDPAK (顶部散热) | TO-247-4 | TO-247-4 |

| 热阻 (RthJC) | 0.40 K/W | 0.35 K/W | 0.20 K/W | 0.15 K/W |

| 核心应用场景 | 3kW-5.5kW PSU PFC/LLC | 液冷电源模块, 高密度SMPS | 高可靠性PFC (抗浪涌/辐射) | 3相PFC, 800V HVDC架构 |

表 2:AI服务器电源技术演进路线图

| 阶段 | 传统计算 | 高性能计算 (HPC) | AI工厂 (当前主流) | 下一代 AI (未来) |

|---|---|---|---|---|

| 机架功率 | 10 - 15 kW | 20 - 40 kW | 100 - 132 kW | > 200 kW - 1 MW |

| 电源单元 (PSU) | 800 W - 1.6 kW CRPS | 2 kW - 3 kW CRPS | 5.5 kW - 8 kW 电源架 | 12 kW - 33 kW / 集中整流 |

| 母线电压 | 12 V | 12 V / 48 V | 48 V / 54 V | 400 V / 800 V HVDC |

| PFC 拓扑 | 硅基 Boost PFC | 交错并联 Boost (Si) | SiC 图腾柱 CCM PFC | 三相图腾柱 / 维也纳整流 |

| 散热方式 | 风冷 (Fans) | 风冷 + 热管 | 液冷 (冷板/背门) | 芯片级液冷 / 浸没式 |

表 3:SiC MOSFET 在 AI 电源关键拓扑中的价值分析

| 拓扑级 | 硅器件的瓶颈 | SiC 的解决方案 | 系统级价值 |

|---|---|---|---|

| 图腾柱 PFC (快桥臂) | 体二极管反向恢复电荷 (Qrr) 过大,导致CCM模式下严重的开关损耗和炸管风险。 | 近零 Qrr ,允许在CCM模式下进行高效硬开关。 | 实现99%以上的PFC效率;大幅减小电感体积 (频率提升2-3倍)。 |

| DC-DC (LLC 原边) | 输出电容 (Coss) 较大且非线性,限制了死区时间优化和开关频率。 | 更低且线性的 Coss,更低的关断损耗 (Eoff)。 | 支持 >500 kHz 开关频率;缩小变压器和谐振腔体积。 |

| BBU 双向变换 | 导通电阻随温度急剧上升,双向效率难以兼顾。 | 高温下 RDS(on) 极其稳定 (175°C仅增加~40%)。 | 提升电池充放电效率;减少散热需求,延长电池寿命。 |

| 热管理与封装 | 只能通过底部PCB散热,热阻大,无法应对高密度热流。 | QDPAK/TOLT 顶部散热封装,直接贴合冷板。 | 解除PCB热瓶颈;完美适配液冷机架设计;提升功率密度至100 W/in³+。 |

审核编辑 黄宇

-

碳化硅 (SiC) MOSFET dv/dt 极限物理本质深度研究报告2026-02-15 235

-

AI算力中心下一代液冷电源架构研究报告2026-02-10 323

-

电镀电源拓扑架构演进与SiC功率模块及驱动技术的深度价值分析报告2026-01-28 368

-

轨道计算基础设施:太空光伏为太空AI算力供电的电源架构演进2026-01-27 1358

-

B3M系列碳化硅MOSFET软反向恢复技术特性及其在桥式拓扑中的应用价值研究报告2026-01-06 279

-

MCS兆瓦级充电系统拓扑架构演进与SiC碳化硅模块升级替代IGBT模块技术研究报告2025-12-26 185

-

阳台微储的拓扑架构演进、技术趋势及碳化硅MOSFET在其中的应用2025-12-20 1524

-

倾佳电子主流厂商碳化硅 (SiC) MOSFET 驱动 IC 产品及其技术特征深度研究报告2025-11-23 1934

-

在开关电源转换器中充分利用碳化硅器件的性能优势2023-03-14 2865

-

图腾柱无桥PFC中混合碳化硅分立器件的应用2023-02-28 2316

-

浅谈硅IGBT与碳化硅MOSFET驱动的区别2023-02-27 2994

-

碳化硅MOSFET的SCT怎么样?2019-08-02 2386

全部0条评论

快来发表一下你的评论吧 !