从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

描述

黄晶晶 综合整理

高速互连芯片定义及分类高速互连芯片是支撑数据中心、服务器及计算机实现高速数据交互的必备芯片,主要解决智能算力系统持续升级背景下各类数据传输的瓶颈。高速互连芯片适配多种 标准化通信协议,通过信号处理、架构优化等方式,保障数据在各系统间高效、可靠传输。

全球数据正以指数级速度增长,预计 2025年全球数据生成量将达197.3 ZB(泽字节,1泽字节等于10²¹字节),到2030年将增长达到635.3 ZB,复合年增长率达到26.3%。海量数据的产生,使得数据处理及数据交互需求呈井喷式增长,高速互连芯片作为数据传输的必要支撑,潜 在需求量随之大幅提升。

各类标准化通信协议不断演进,传输速率持续提升,以PCIe协议为例,每次迭代升级,传输速率均会翻倍。数据传输速率加快,会带来显著的信号衰减、信号完整性等问题。高速互连芯片可有效解决这些难题,其在数据传输中的必要性和价值量与日俱增。

2022年ChatGPT问世,带动AI训练的需求;2024年后AI应用加速落地,带动AI推理的需求。大模型的训练和推理正在深层次改变AI服务器的架构,摒弃单纯增加服务器数量的方式,转而采用「强扩展」(Strong Scaling)模式,通过提升内存带宽、增加网络硬件密度等措施构建高带宽、低延迟的算力集群。这一转变使得芯片间、服务器机箱之间、服务器集群间互连以及数据中心间之间的互连需求激增,对高速互连芯片的数量和复杂度都提出了更高要求。

高速互联芯片的全球服务器及PC市场需求

高速互连芯片以服务器领域为主要应用场景,在PC领域亦有部分应用。

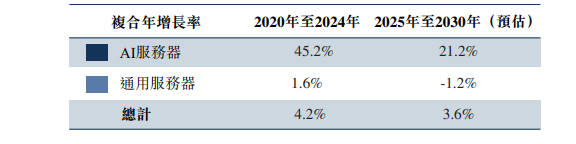

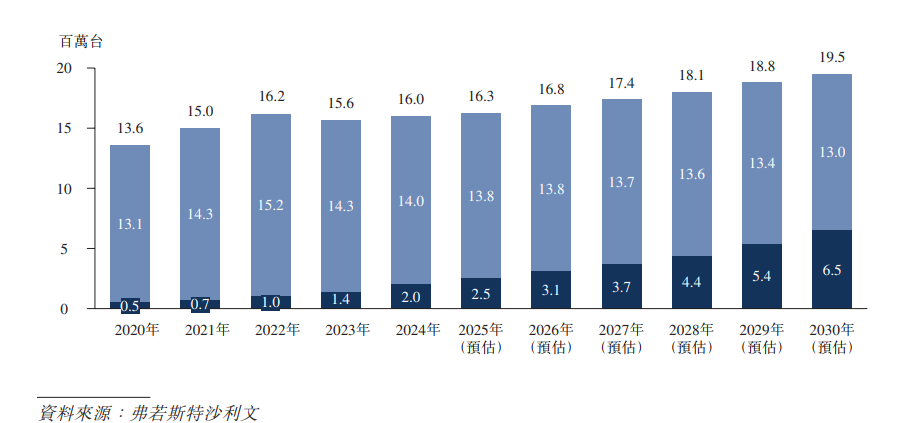

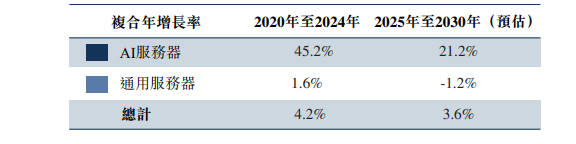

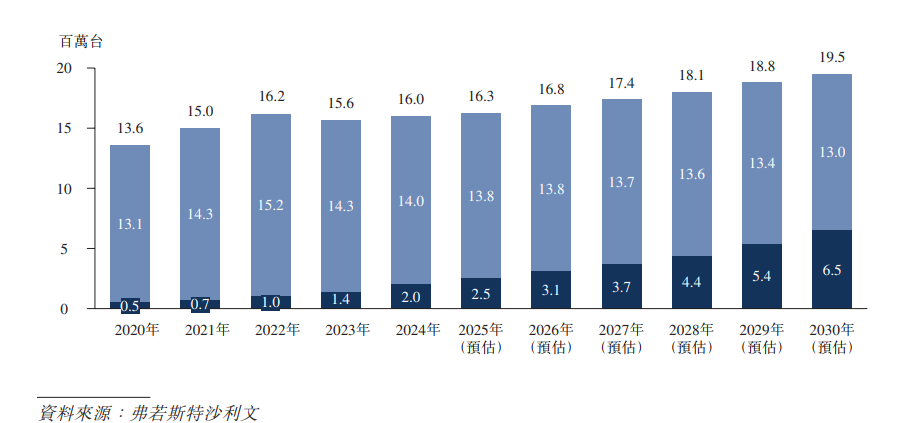

AI服务器对高速互连的需求与日俱增,成为支撑高速互连芯片市场扩容的因素之一。全球AI服务器出货量从2020年的0.5百万台增至2024年的2.0百万台,复合年增长率为45.2%;展望未来,其出货量预计将从2025年的2.5百万台增长至2030年的6.5百万台,复合年增长率为21.2%。AI服务器需求的增长,源于其计算负载对更高带宽、更高效数据交换的需求。多芯片集群架构需高带宽、低延时互连支撑大规模数据交互,从而推动PCIe/CXL互连芯片、以太网及光互连芯片的需求,同时推动对更大容量及 更高带宽系统主内存的需求。

随着AI服务器采用多卡互连+高速协议架构,支持PCIe 6.0、CXL 3.0等新一代标准的高速互连芯片需求将持续攀升。通用服务器市场需求相对稳定,但同时也需要高速互连芯片来提升数据访问稳定性,其增速虽较AI服务器更为平缓,仍是芯片市场的重要支撑。

全球服务器出货量,按服务器类型(AI、通用)拆分,2020年至2030年(预估)

全球PC出货量总体呈平稳增长趋势,2024年出货量为258.9百万台,未来预计出 货量将从2025年的262.9百万台增长至2030年的297.7百万台,复合年增长率为2.5%。

在AI时代,尤其是大模型爆发式发展以来,数据中心和服务器对于高速互连的需 求呈指数级增长,直接拉动高速互连芯片市场扩容。摩尔定律持续推动半导体进步, 因此需要创新的互连产品来克服日益多样化的算力架构中的带宽瓶颈。同时,Scaling Law表明,AI模型的性能随着模型规模、训练数据集规模及计算负荷(FLOPs)的扩大而提高,这对数据传输带宽及内存访问效率提出越来越严格的要求。这使得高速互连芯片成为AI算力扩展的关键技术。

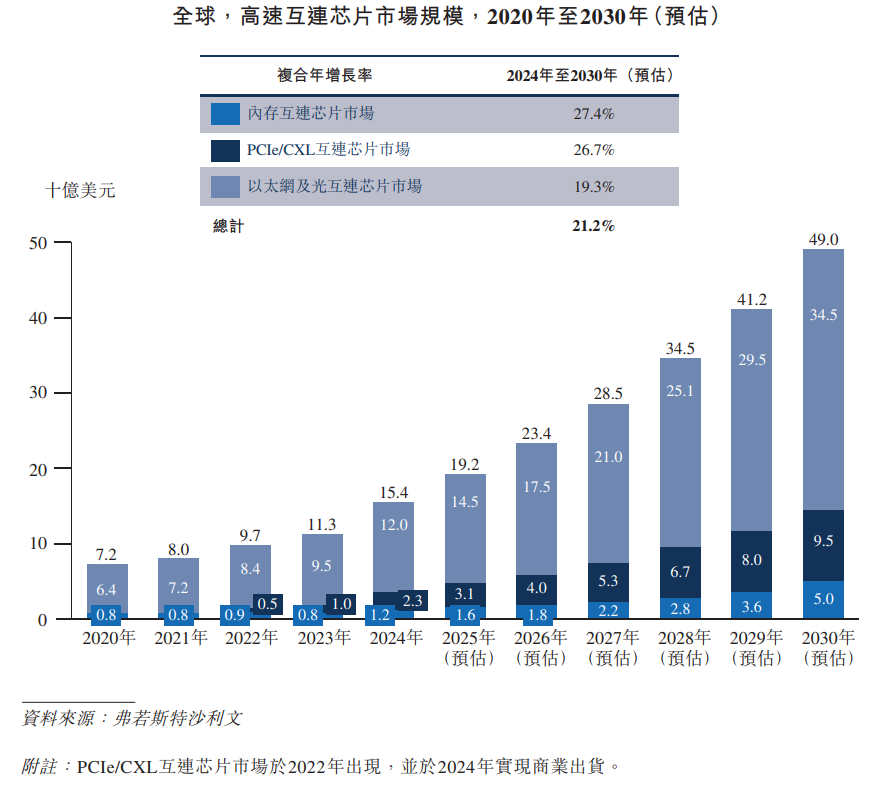

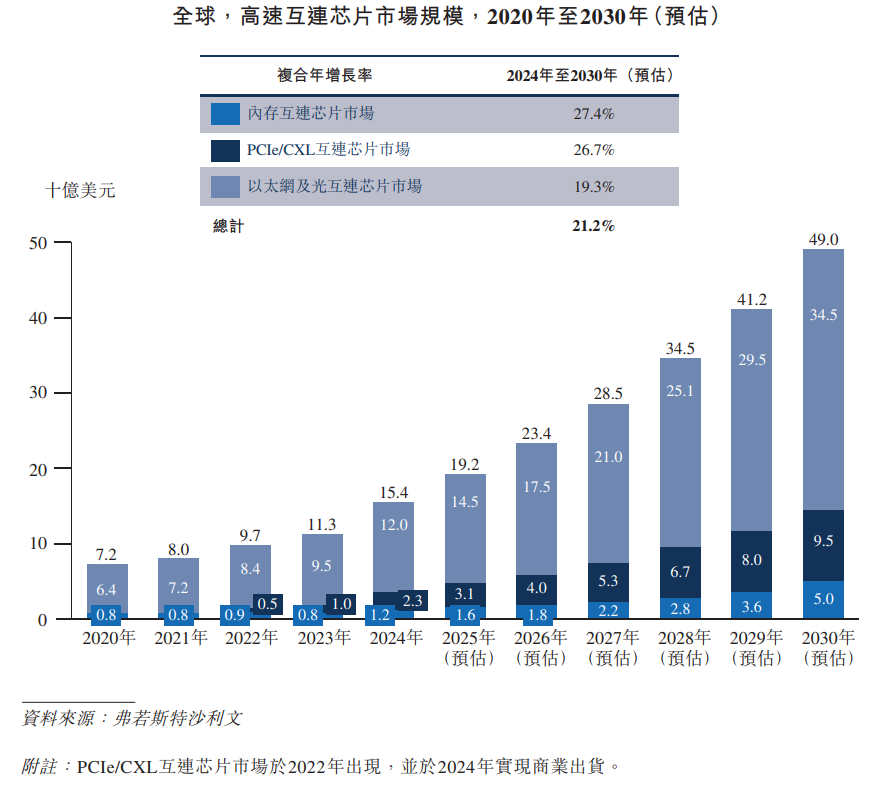

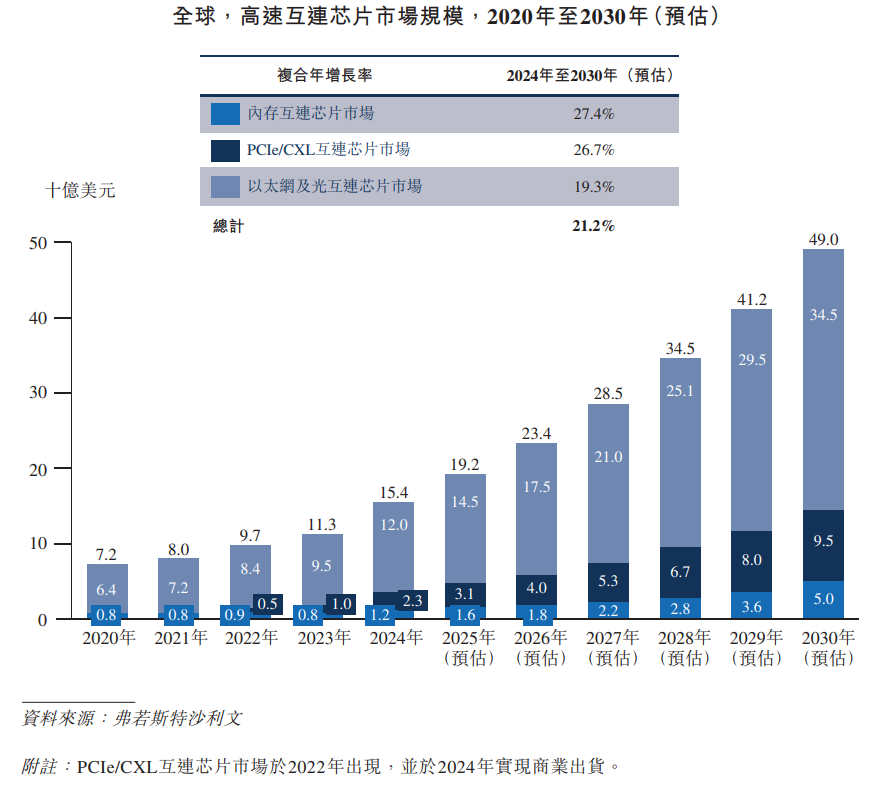

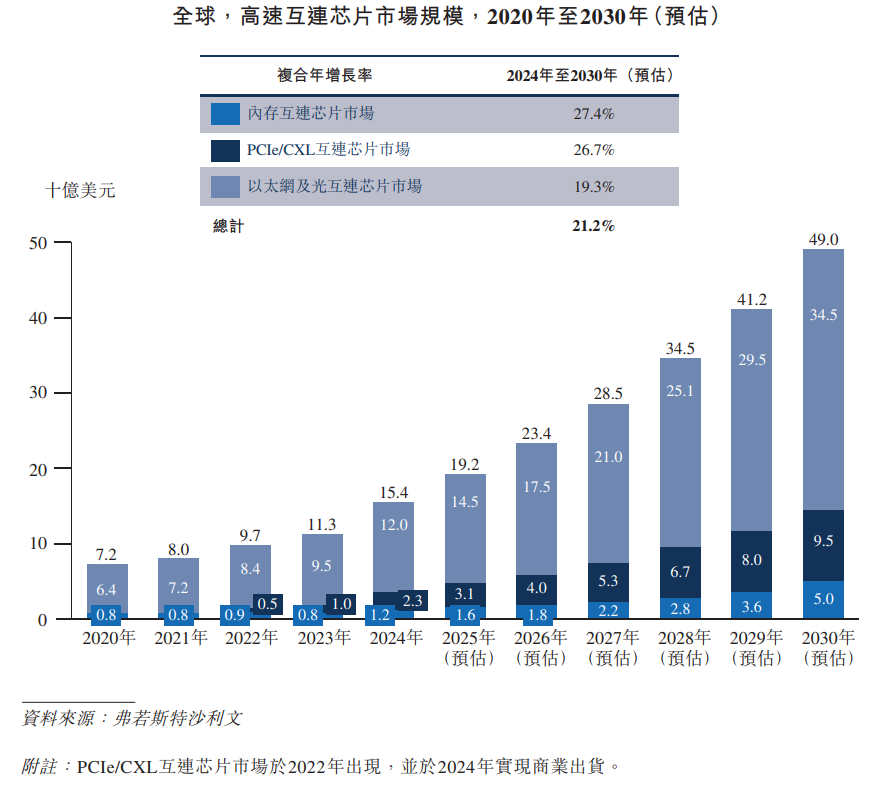

2024年全球高速互连芯片市场规模为154亿美元,预计将于2030年进一步增长至490亿美元,复合年增长率为21.2%;其中,中国市场成为增速最快的细分市场之一,2024年其市场规模占全球约为25%,2030年预计提升至30%,市场占比增长的主要原因为未来中国AI服务器需求增速预计将高于全球。

从技术类别来看,全球内存互连芯片市场规模预计从2024年的12亿美元增长至 2030年的50亿美元,复合年增长率为27.4%;PCIe/CXL互连芯片市场规模预计从2024 年的23亿美元增长至2030年的95亿美元,复合年增长率为26.7%;以太网及光互连芯片市场规模预计从2024年的120亿美元增长至2030年的345亿美元,复合年增长率为19.3%。

• 内存接口芯片(RCD/DB)

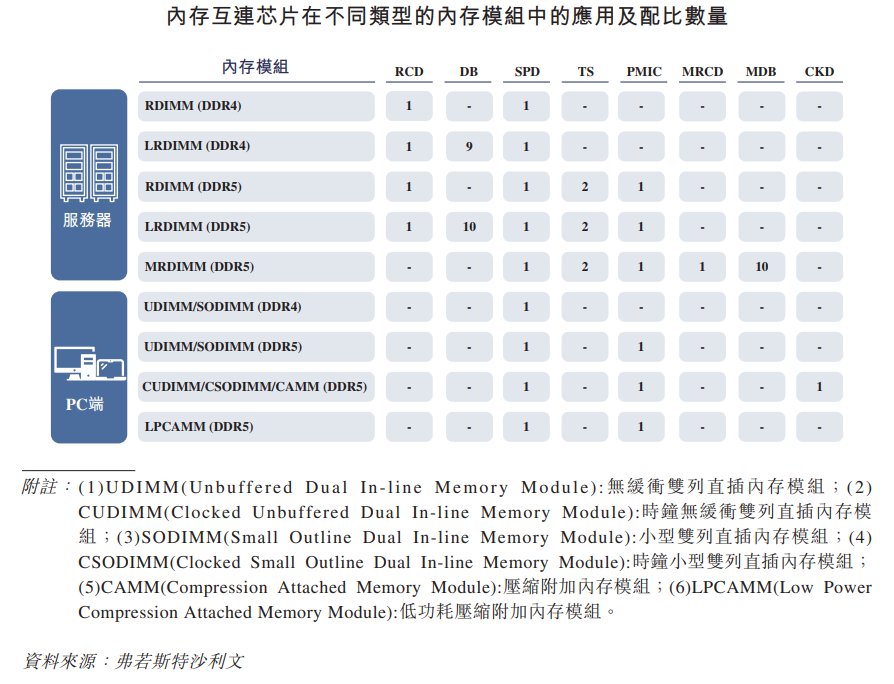

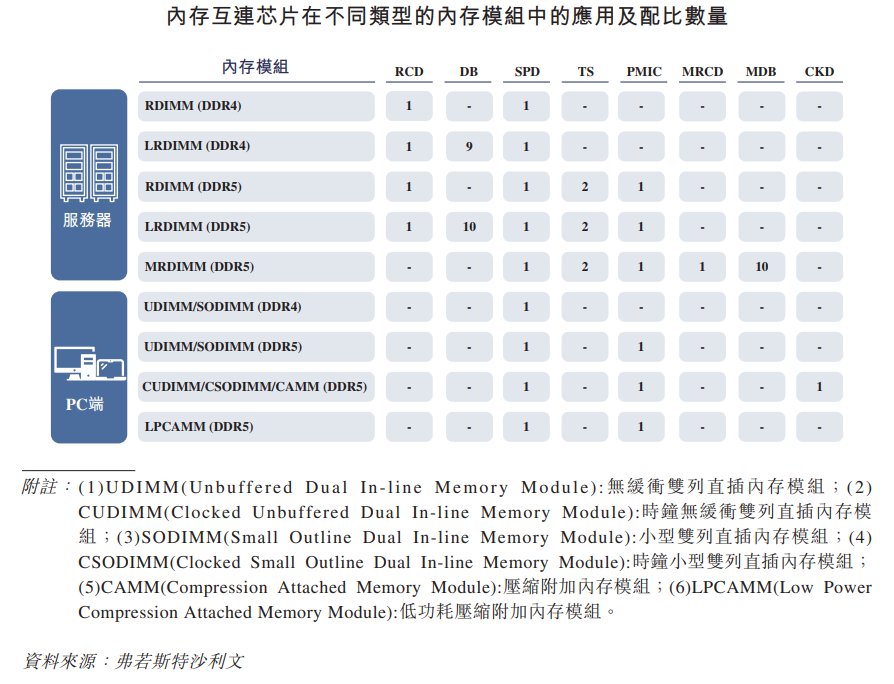

内存接口芯片(RCD/DB)是服务器内存模块的核心逻辑器件,作为服务器 CPU存取内存数据的必由通路,其主要作用是提升内存数据访问的速度及可靠性。 DDR4及DDR5内存接口芯片按功能可分为两类:一是RCD(寄存时钟驱 动器),用来缓冲来自内存控制器的地址、命令、时钟、控制信号;二是DB(数 据缓冲器),用来缓冲来自内存控制器或内存颗粒的数据信号。仅采用RCD的内 存模块为RDIMM(寄存双列直插内存模块),同时采用RCD和DB的内存模块为 LRDIMM(减载双列直插内存模块)。目前RDIMM为市场主流的内存模块类型。 根据JEDEC标准,每根DDR4或者DDR5服务器内存模块(RDIMM/LRDIMM)需 要一个RCD芯片。DB芯片用在LRDIMM上,其中每根DDR4 LRDIMM需要9颗 DB芯片,每根DDR5 LRDIMM需要10颗DB芯片。

• 内存模块配套芯片(SPD、TS、PMIC)

根据JEDEC标准,DDR5内存模块上除了内存颗粒及内存接口芯片外,还 需要三种配套芯片,分别是SPD(串行检测集线器)、TS(温度传感器)以及PMIC(电源管理芯片)。SPD内置EEPROM(带电可擦可编写只读存储器),用于存储内 存模块的相关信息以及模块上内存颗粒和相关器件的所有配置参数,同时SPD作为I2 C/I3C总线集线器,是系统主控设备与内存模块上组件之间的通信中心。此外,SPD内部还集成了一颗TS,可连续监测SPD所在位置的温度。TS是DDR5高精度温度传感器芯片,符合JEDEC规范,支持I2 C和I3C串行总线,用于实现对内存模块的温度监控。PMIC为内存模块上的其他芯片提供电源支持,进行电源管理。

根据JEDEC标准,每根DDR4和DDR5服务器内存模块都包含一个SPD。此 外,每根DDR5 RDIMM/LRDIMM/MRDIMM还需要一个PMIC及两个TS。主流的DDR4和DDR5 PC内存模块通常包含一个SPD,而DDR5 PC内存模块还需要一个PMIC。DDR5内存模块中的SPD相比DDR4中的更为复杂,价值也更高。

• 高带宽内存接口芯片(MRCD/MDB)

MRCD/MDB芯片是服务器高带宽内存模块MRDIMM的核心逻辑器件,每 根MRDIMM模块均需要搭配1颗MRCD、10颗MDB。MRDIMM通过MDB芯片 可以同时访问两个DRAM内存阵列(而传统RDIMM只能访问一个阵列),从而在 标准速率下实现双倍带宽。该产品主要应用于云计算、AI等对内存带宽要求较高 的应用领域。

• 时钟驱动器芯片(CKD)

根据JEDEC定义,当DDR5数据速率达到6400MT/s及以上时,PC内存模块需引入CKD芯片,对时钟信号进行缓冲和重新驱动,以满足高速时钟信号的完整性和可靠性要求,这对在有关数据速率下稳定运行至关重要。CKD芯片用于更高速率的PC端内存模块上,一般一根PC端内存模块需要配置一颗CKD芯片。一般来说,一台PC需要配置一至两根内存模块。

DDR4的生命周期覆盖2013年至2025年,DDR5的生命周期预计将从2021年延续至2030年。DDR5 MRDIMM预计从2025年前后开始规模应用。内存颗粒与内存模块产品的代际更迭,正从需求量与价值量双维度,驱动内存互连芯片市场增长进入快速发展通道。

内存互连芯片市场规模

内存互连芯片主要应用于服务器领域,部分内存互连芯片亦应用于PC领域,其市场规模与服务器及PC的出货量、单台配置的内存模块种类及数量密切相关。

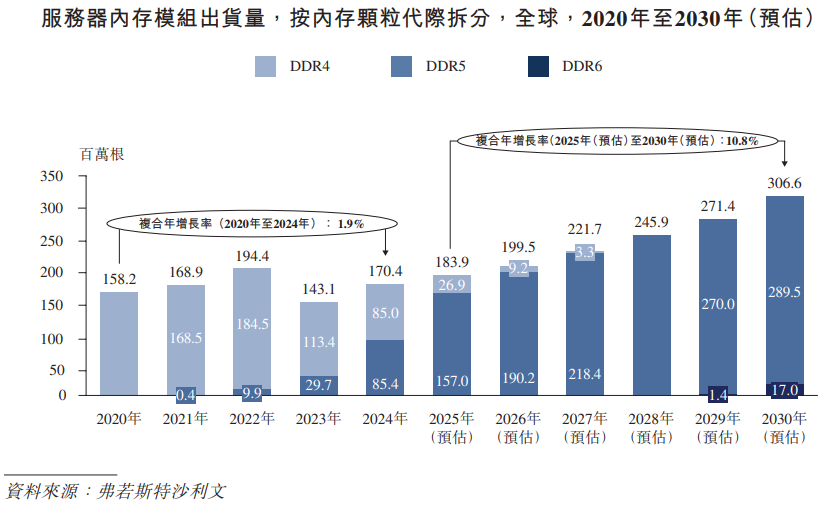

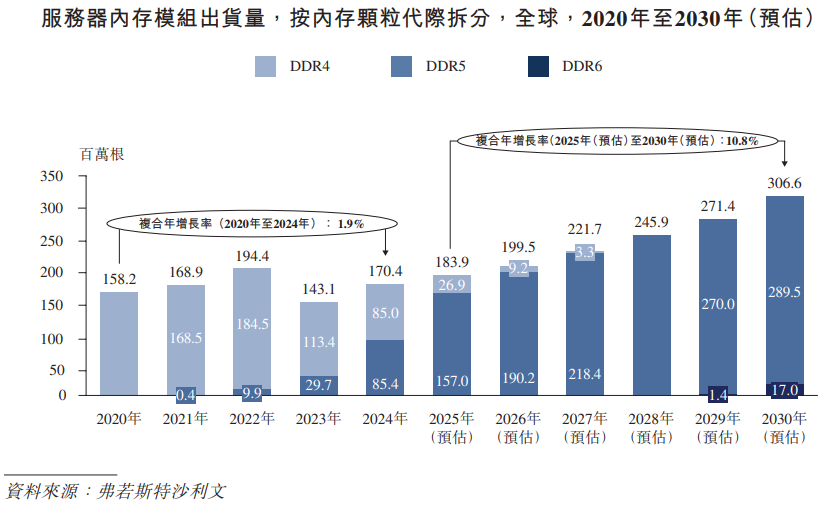

全球内存模块的市场需求 2020年至2024年,服务器内存模块出货量从158.2百万根增长至170.4百万根;到 2030年预计将攀升至306.6百万根,2025年至2030年间的复合年增长率约为10.8%,呈 现良好增长态势。从市场结构上看,服务器内存模块正加速向DDR5世代迈进:DDR5 从2021年开始在下游应用,到2024年渗透率已超过50%,预计在2025年将超过85%。同时,DDR6内存模块有望在2029年前后实现商业化应用,为市场注入新的增长动力。

驱动服务器内存模块需求量增长的核心因素,在于全球服务器出货量的增长,以及单台服务器内存模块配置数量的增加。AI服务器的崛起,进一步推动了市场需求。由于对内存容量的要求显著增加,一般来说,一台通用服务器配置8-12根内存模块,而一台AI服务器配置16-24根内存模块。因此,随着AI技术在各行业的广泛应用,AI 服务器渗透率持续提升,将直接推动服务器内存模块整体需求增速高于服务器增速, 进而为内存互连芯片市场带来广阔的发展空间。

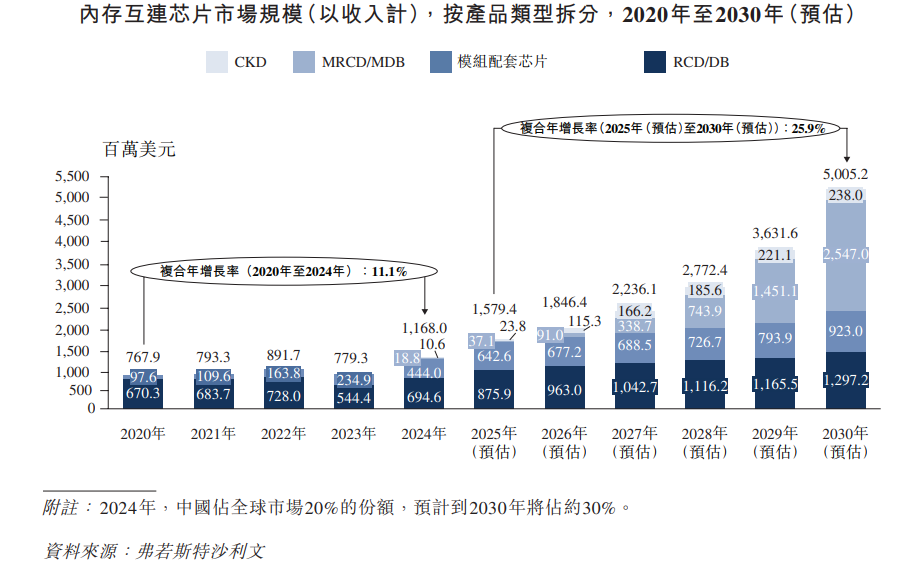

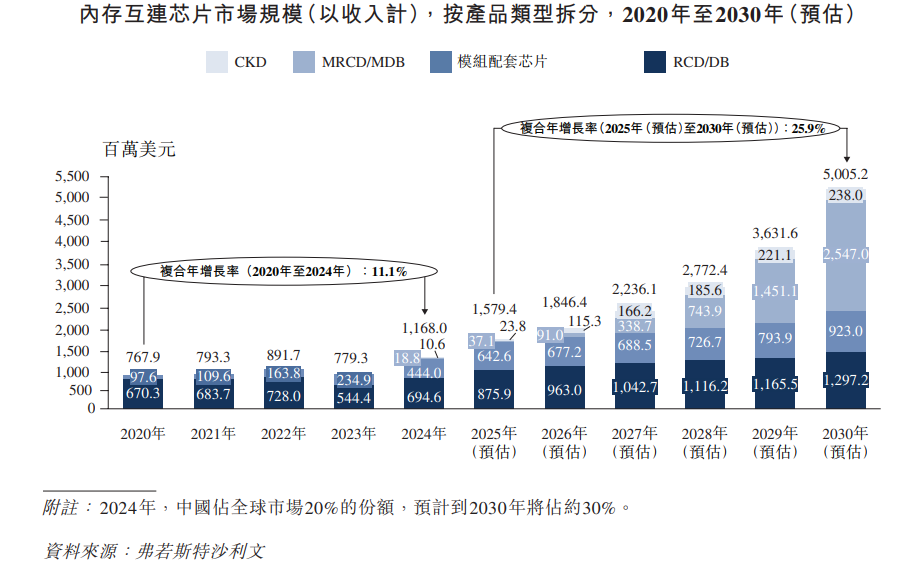

内存互连芯片是JEDEC定义的内存模块标准器件,其市场规模从2020年的767.9 百万美元增长至2024年的1,168.0百万美元,预计未来将进一步从2025年的1,579.4百万 美元增长至2030年的5,005.2百万美元,期间复合年增长率高达25.9%。

内存模块需求增长带动芯片市场扩容 内存互连芯片与内存模块有着明确的配比关系,其需求量与内存模块紧密相关。根据弗若斯特沙利文的资料,服务器内存模块的需求量将从2025年的183.9百万根跃升至2030年的306.6百万根,这一显著增长趋势,将直接促使内存互连芯片数量同频增长,成为市场规模扩张的基础。

服务器产品升级激发新的市场增长点

• DDR5技术升级提升芯片价值:由于产品技术难度、复杂度和性能的提升, DDR5 RCD、SPD芯片价值量较DDR4明显增加;同时,服务器DDR5内存模块 新增配套芯片的需求,包括TS和PMIC芯片。产品升级不仅带来芯片单价提升, 更拓展了芯片种类,成为DDR5世代市场增长的动力。

• 新型高带宽内存模块MRDIMM创造市场增量:基于AI应用对内存带宽的迫切需 求,MRDIMM以其优异的带宽性能,预计将成为主流AI服务器系统主内存的优 选方案。2025年,MRDIMM开始在下游规模应用,预计至2030年,其在AI服务 器内存模块中的渗透率将达30%,出货量高达53.4百万根,2025年至2030年的复 合年增长率为148.0%。相较广泛应用的RDIMM(仅需一个RCD),MRDIMM所 需的MRCD价值更高,同时新增10颗MDB的需求,因此随着MRDIMM渗透率不 断提升,将显著推高内存互连芯片市场规模。

• 子代持续迭代维系平均销售价格:DDR5 RCD芯片预计推出6个子代产品, MRCD/MDB芯片预计有3个子代产品,未来几年持续的子代迭代,将通过技术创 新与性能优化,维系产品的平均销售价格与毛利率,为内存互连芯片市场的长期 稳定增长提供保障。

PC领域市场主要增长逻辑

• DDR4至DDR5升级新增芯片需求:PC领域的DDR5内存模块(包括UDIMM/ SODIMM/CAMM/LPCAMM)需要搭配一颗更高规格、价值量更高的SPD,并新增一颗PMIC,推动DDR5世代芯片价值量提升。

• DDR5支持速率提升进一步带动芯片需求扩容:DDR5第一子代产品支持的速率 是4800MT/s,当数据速率达到6400MT/s及以上时,PC内存模块(包括CUDIMM/ CSODIMM/CAMM)需要新增加一颗CKD芯片,该芯片从2025年开始渗透,预计2029年覆盖几乎所有PC内存模块,开拓消费级市场新空间。

内存互连芯片市场的发展趋势

• 算力爆发驱动内存容量及带宽需求增长:大模型训练与推理对算力的迫切需求,正持续推高内存容量和带宽升级。以GPT为代表的大模型,参数规模突破万亿 级,推动AI服务器内存配置显著升级—-单台主流AI服务器通常需部署超20条 DDR5内存模块,内存容量和数量远超通用服务器。同时,算力的爆发也对内存 带宽提出了更高的要求,DDR5第一子代RDIMM支持速率为4800MT/s,第六子 代预计突破9000MT/s,而第二子代MRDIMM更是达到12800MT/s。随着技术成 熟及生态逐步完善,MRDIMM凭借更高带宽与综合性能,有望取代RDIMM成 为AI服务器主流方案,带动MRCD/MDB芯片需求激增。在PC领域同样呈现高速 发展态势,DDR5在游戏本和AI PC等高阶终端加速渗透,模块速率逐步迭代至 6400 MT/s及以上。为了保障高速运行下的信号完整性,预计到2029年几乎所有 的PC内存模块都将标配CKD芯片。

• 技术迭代周期显著缩短:内存互连芯片技术正沿「协议升级迭代 - 传输速率提 升-芯片功能复杂化」路径加速演进,高速信号处理与低功耗设计等技术成为核 心竞争点,内存互连芯片的价值量将持续提升。在服务器领域,DDR4仅经历四 个子代迭代,每个子代的迭代周期约为18~24个月;而DDR5预计有六个子代,DDR5第二子代产品2024年出货已超过第一子代产品,第三子代在2025年快速上量,当前子代迭代周期已逐步缩短至12-18个月,技术迭代节奏较DDR4世代明显 提速。

• 市场集中度持续提升:从内存互连芯片市场发展历史来看,行业领先企业凭借丰 富的产品组合、深厚的技术积累、完善的专利布局形成了完整的内存互连解决方 案能力,在标准制定、研发创新等方面发挥引领作用、具备显著优势,逐步实现 市场份额向少数几家头部企业集中。展望未来,行业头部企业基于其市场领先优势,持续通过前瞻性投入下一代技术研发、优化供应链管理,这些企业有望进一步提升其市场竞争力和市场份额,推动行业资源的高效整合与合理配置。

• PCIe Retimer芯片:适用于PCIe协议的超高速信号调理芯片,主要用于解 决数据在高速、远距离传输场景中时序不齐、损耗严重、完整性差等问 题,在CPU与高速外设(如GPU、AI加速卡、SSD卡及网卡等)的互连中发 挥重要作用。从定价来看,不同产品类型差异较大,2024年行业平均单价 范围为约25.0美元至50.0美元。

• PCIe Switch芯片:用於擴展接口數量,通過內部交換架構實現CPU與外圍 設備(如NIC、SSD、GPU)之間的高速數據轉發,實現更多設備間的高密 度PCIe互連。從定價來看,不同產品類型差異較大,芯片價格主要取決於 其支持的鏈路數。2024年行業平均單價範圍為約600.0美元至1,200.0美元。 近年來,PCIe協議技術迭代加速:從PCIe 5.0(32GT/s)升級至PCIe 6.0(64GT/s), 傳輸速率實現翻倍,最新發佈的PCIe 7.0規範更將單通道速率提升至128GT/s。在下游 應用方面,支持PCIe 5.0協議的相關芯片和設備正在成為市場主流,未來技術將持續向 更高速率、更低延遲及低功耗方向演進,以匹配AI服務器等新興場景的高速互連需求。

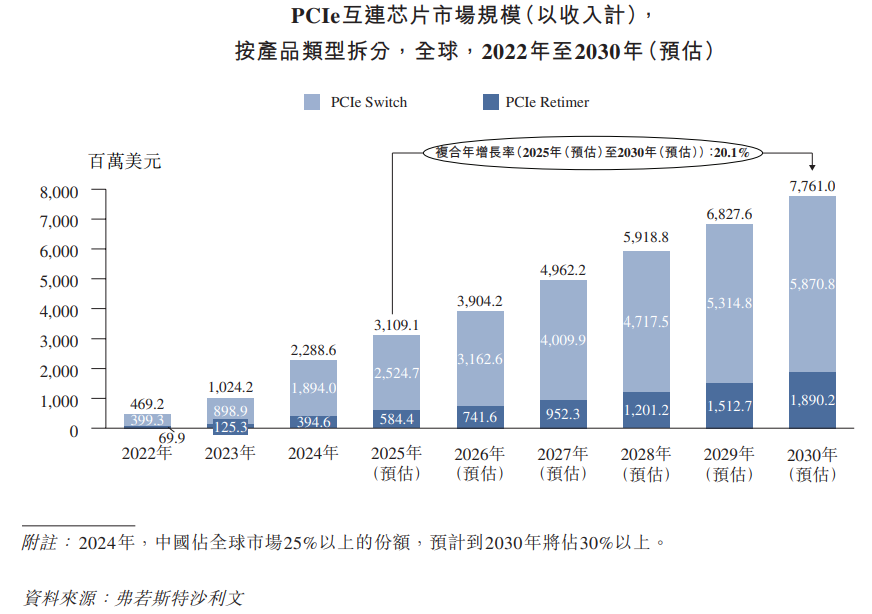

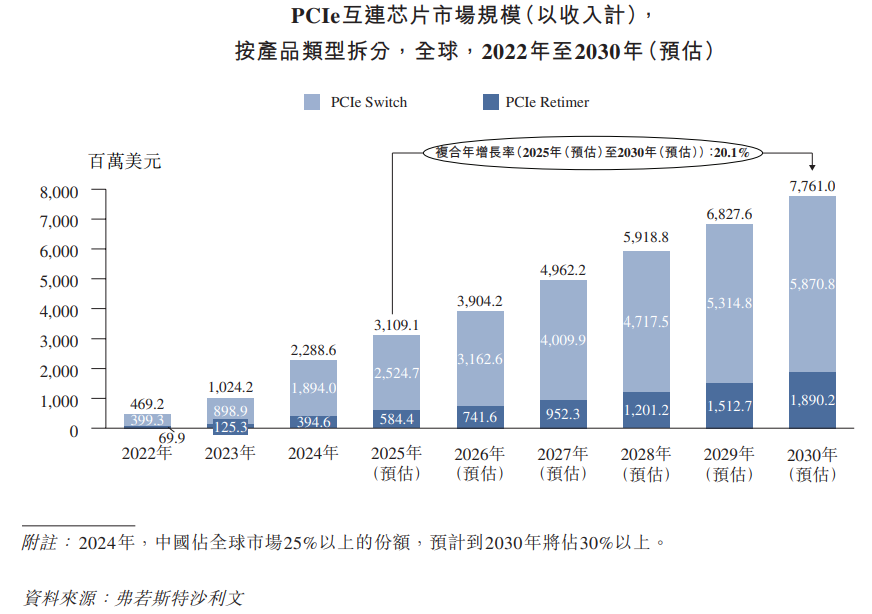

PCIe互連芯片市場規模 PCIe互連芯片市場規模從2022年的469.2百萬美元快速增長至2024年的2,288.6 百萬美元。行業預測顯示,未來該市場將持續高速增長,預計2030年市場規模將達到 7,761.0百萬美元,2025年至2030年間的年複合增長率高達20.1%。

PCIe互连芯片市场的主要驱动因素

• AI服务器出货量激增,拉动芯片需求放量:AI服务器架构中,随着GPU/AI芯片 数量持续攀升、模型规模迅速扩大,对系统带宽及高速互连需求大幅增长,PCIe 互连芯片已成为高速设备间互连的关键器件。PCIe Switch提供扩展或聚合能力, 并允许更多的设备连接到一个PCIe端口,而PCIe Retimer则用于保障系统的信号 完整性与稳定性,提升高速信号的有效传输距离。以一台主流8卡GPU服务器为 例,通常需配备2至4个PCIe Switch实现拓扑扩展,同时需要8至16个Retimer, 以延长CPU与外设间的有效传输距离。因此,PCIe互连芯片已成为AI服务器中 不可或缺的核心器件,其需求量与AI服务器出货量呈正相关。

• PCIe协议持续迭代升级,拓展应用场景边界:目前PCIe 5.0正在逐步成为市场主 流,未来还将进一步向PCIe 6.0及PCIe 7.0演进,PCIe协议每次迭代将带来数据 传输速率翻倍,由此驱动两大增长逻辑:一方面,更高速率带来更复杂的信号完 整性问题,PCIe Retimer的应用场景从当前的CPU及GPU/AI加速卡/SSD/网卡互 连,将延伸至有源线缆(AEC)、边缘计算设备、智能汽车等连接密集型场景;另 一方面,协议迭代推动服务器集群组网需求,PCIe Switch需承担多设备带宽优化 与拓扑架构升级任务,在AI推理服务、数据中心高密度部署等场景中重要性持续 提升。

CXL互连芯片市场概览及市场规模

CXL互连芯片市场的定义及分类 CXL互连芯片是基于CXL协议构建的高速互连核心器件,其物理层沿用PCIe标 准,可以实现CPU、GPU、内存间高速低延迟的数据交互,主要应用于内存扩展和内 存池化场景,主要产品分为两大类。从定价来看,由于CXL的应用和生态系统开发尚 处于早期,相关产品还未达到规模商业量产阶段,目前还未形成成熟的定价体系。现有产品的单价取决于规格及功能,范围一般为约100美元至1,000美元。

• CXL MXC芯片:作为处理器与CXL内存模块高速连接枢纽,负责完成协议转换、内存访问调度及一致性控制,是构建内存扩展和内存池化架构的 关键控制器;

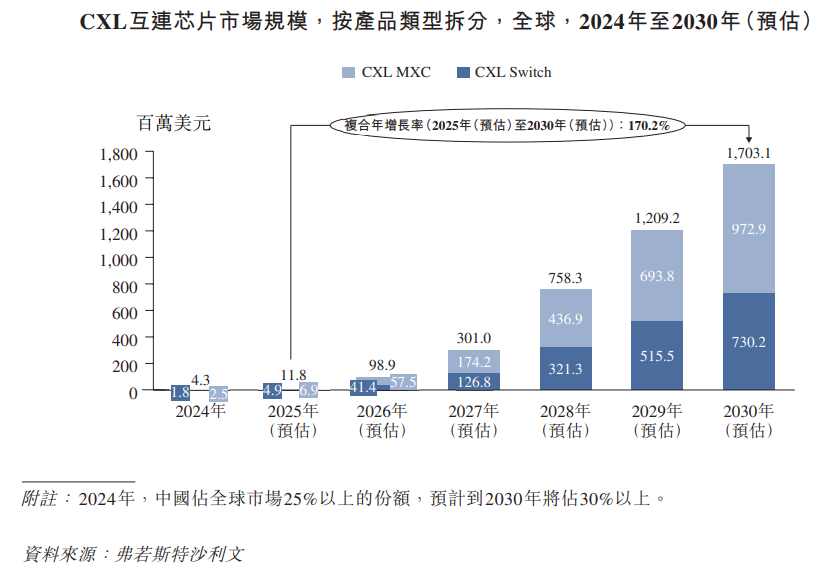

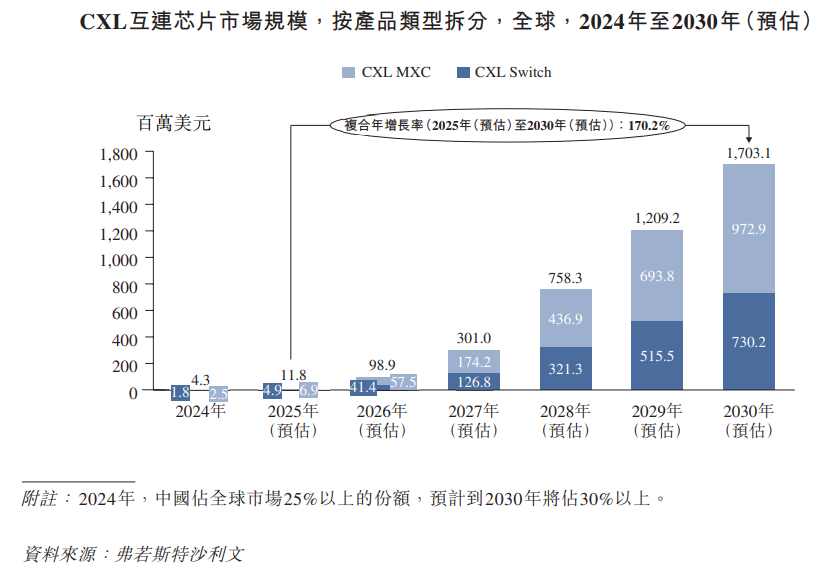

• CXL Switch芯片:用于实现多个CXL主机及设备之间的互连与资源管理,支持单个或者多个CPU连接多个CXL内存或加速设备,提升系统扩展能力 和资源利用效率,是大规模内存池化架构的核心支持组件。两者协同构建CXL互连解决方案,将在新一代数据中心架构中发挥重要作用。CXL互连芯片市场规模 2024年CXL互连芯片市场尚处于商业化初期,市场规模约为4.3百万美元,行业预测未来几年该市场将迎来爆发式增长,预计至2030年市场规模将达到1,703.1百万美元,2025年至2030年期间的复合年增长率高达170.2%。

CXL互连芯片市场的主要驱动因素

• CXL协议持续在AI领域渗透,拉动芯片需求增加:在AI领域,CXL技术通过支 持GPU和FPGA(现场可编程闸阵列)等加速器与主处理器的高效协作,可显著提 升AI模型训练和推理的速度,实现低延迟、高速的数据传输,从而大幅提高计算效率;同时CXL技术支持内存扩展和共享机制,为AI应用提供更大的内存空间 和更灵活的资源分配方案,解决内存带宽瓶颈。作为CXL技术落地的核心载体, CXL互连芯片支撑上述应用场景,其需求与AI服务器密切相关,并将在AI领域 发挥更大的作用。

• 系统架构重构及连接复杂度提升,推动应用场景拓展:AIGC推动数据中心向万 卡级集群演进,芯片至数据中心的多维互连复杂度指数级提升,传统互连方案难 以满足TB级带宽与百纳秒级延迟需求,CXL通过内存池化与高速互连实现架构 升级:CXL MXC在内存扩展及内存池化领域能够有效提升内存容量和带宽,以 适配云计算和AI等数据密集型应用的需求;同时,CXL Switch也逐步开始应用 于服务器平台,支持多节点设备的内存和资源共享,优化服务器集群的拓扑架构 与资源利用率。

目前,国际知名大型互联网厂商正在探索在其新型服务器集群中 部署CXL内存资源池,单个内存池通常需要配置16-32颗CXL MXC和2-4颗CXL Switch芯片。随着CXL内存池在服务器中渗透,CXL互连芯片市场将进入爆发增 长通道。CXL技术可通过内存池化赋能内存扩展,显著提升GPU集群的算力效 率,并降低总拥有成本(TCO)。

PCIe/CXL互连芯片的准入壁垒及关键成功因素

• 协议驱动的技术迭代与创新能力:PCIe/CXL互连芯片的核心竞争力根植于对协 议标准演进的快速响应及底层技术突破。企业需紧跟从PCIe从5.0向6.0乃至7.0、 CXL从1.0到3.x的协议迭代节奏,通过持续研发投入攻克信号处理、编码算法等关键技术。当PCIe协议持续升级时,需优化高速SerDes串行接口技术,以解决高频传输中的信号衰减、时序抖动等问题,保障芯片兼容性与稳定性;而CXL技术正朝着带宽倍增、延迟优化与功能拓展方向演进,在支持内存池化、点对点直 连的同时,未来或结合光互连技术突破TB级带宽与亚50ns延迟瓶颈。从底层技术看,SerDes作为高速串行传输的「神经中枢」,其速率提升(如PCIe 6.0所需的 64GT/s)与信号完整性优化能力直接决定互连芯片的稳定性与延迟表现;而DDR 控制器技术则通过影响内存访问效率,成为支撑CXL内存池化的关键技术节点。

• 深度需求洞察与生态协同能力:PCIe/CXL互连芯片的另一核心成功要素,在于 对下游客户需求的深度理解与生态关系的紧密维系。随着AI服务器、数据中心等 下游应用场景对高速互连需求的爆发式增长,企业需精准把握客户在PCIe 6.0、 CXL 3.0等协议迭代需求、低延迟、高带宽等性能指标要求,以及成本控制方面 的核心诉求,通过技术预研针对性开发,实现快速响应。同时,企业应与服务器 与云计算厂商等合作伙伴建立长期战略合作,深度参与硬件架构设计与标准制 定,形成「需求反馈-技术迭代-生态适配」的闭环。这种「需求驱动创新+ 生 态协同共进」的模式,不仅能提升产品竞争力,更能构筑起市场壁垒,成为企业在PCIe/CXL市场立足的关键。

以太网互连芯片

全球以太网互连芯片市场规模从2020年的60亿美元增长至2024年的94亿美元, 期间复合年增长率达11.6%,增长主要受云计算与数字基础设施建设的推动。未来随着 AI大模型部署加速,AI服务器、超大规模数据中心及高带宽存储系统对高速低延迟网络的需求激增,400G/800G以太网方案逐步落地,并向1.6T演进,驱动以太网互连芯片需求量和价值量同步提升,预计2030年市场规模将达到247亿美元,2025年至2030 年间复合年增长率高达17.9%。

光互连芯片

光互连芯片是实现高速数据传输的关键组件,通过光电转换技术,支撑下一代数据中心和AI基础设施对高带宽、低功耗互连的需求,已成为核心技术之一。光互连芯片主要分为三类:

• DSP芯片:负责高速信号的调制╱解调、波形整形及数字信号处理(DSP) 纠错功能,是400G、800G等先进调制格式不可或缺的核心器件;

• 激光驱动芯片(Driver)与跨阻放大器(TIA),其中Driver将电信号转换为高频 模拟信号以驱动光发射器,TIA将光探测器输出的微弱电流信号放大为电 压信号,保障高速、高灵敏度的接收链路;

• 硅光芯片:通过在单一硅基平台上集成光子和电子功能,实现小型化、高速光互连,有效解决先进计算系统中的带宽瓶颈与功耗挑战。全球光互连芯片市场规模从2020年的4亿美元迅速增长至2024年的26亿美元,复合年增长率高达57%,增长原因主要源于400G/800G光模块在AI数据中心规模化部署。

展望未来,随着大模型训练集群的GPU规模持续攀升,节点间通信带宽密度和能效比需求急剧增长,光互连技术将成为高性能架构中重要方案,预计至2030年市场规模将达到99亿美元,2025年至2030年期间的复合年增长率为21.5%。

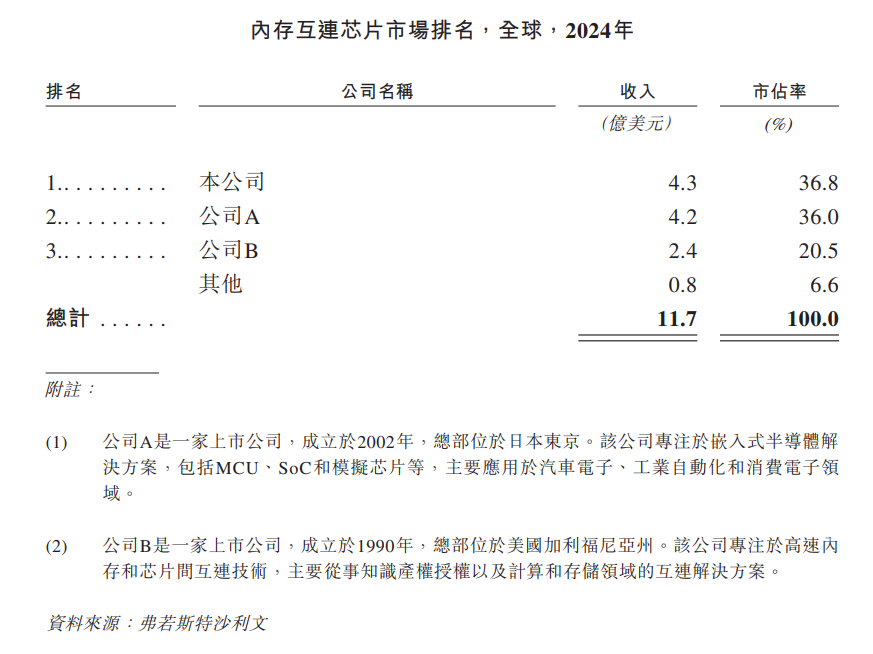

内存互连芯片市场:从DDR4到DDR5世代,该市场的主要厂商稳定在三家,即澜起科技、Renesas及Rambus,市场竞争份额高度集中,目前前三大厂商合计市场份额超过90%。头部 企业逐步形成了「技术壁垒+客户绑定」的双重竞争护城河。

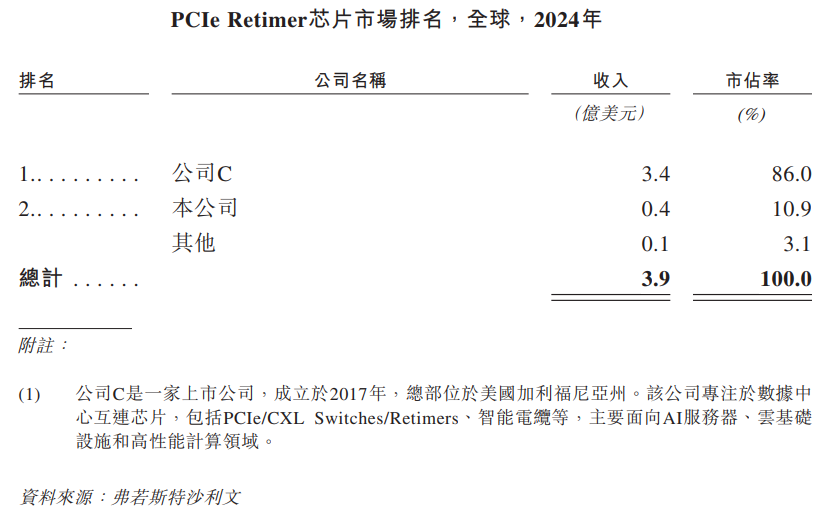

PCIe/CXL互连芯片市场:PCIe互连芯片市场相对较为成熟,展现出显著的头部集中态势,前五大厂商占据超90%的市场份额。2024年,前两大PCIe Retimer厂商合计市场份额96.9%,而PCIe Switch细分市场则由单一厂商占据主导地位。这些领先企业具备高速SerDes设计能力及PCIe协议迭代及产品产业化经验(如已量产PCIe 5.0产品并 送样PCIe 6.0产品),覆盖从芯片到系统级互连的复杂拓扑设计需求,进一步巩固其市场竞争力。

CXL互连技术是近几年兴起的前沿技术,基于该技术的应用和产业生态正在逐步完善,因此相关芯片目前尚未规模量产,市场处于起步阶段。

以太网及光互连芯片市场:少数国际巨头凭借技术及先发优势,占据以太网及光互连芯片市场主要份额。

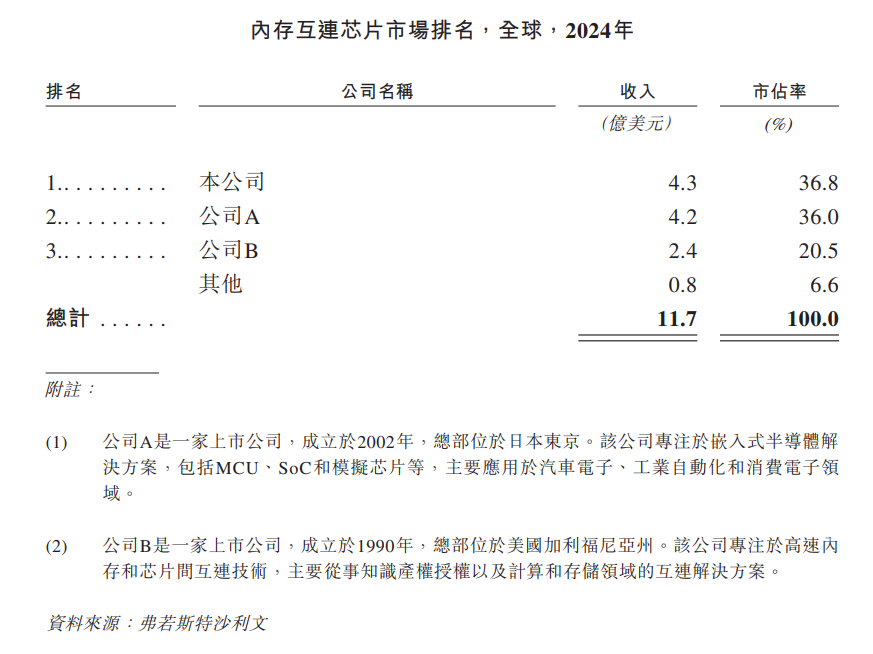

内存互连芯片2024年整体呈现高度集中的市场格局,前三家企业合计占据93.4%的市场份额; 其中,澜起科技以4.3亿美元的收入占据36.8%的市场份额,排名第一。

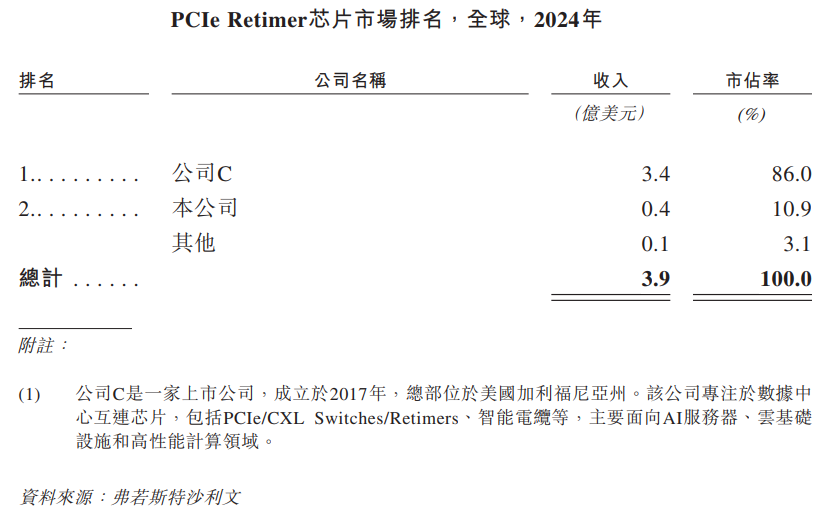

PCIe Retimer 2024年该市场同样也呈现出极高的市场集中度。按2024年的市场份额计, PCIe Retimer提供商中澜起科技排名全球第二。作为市场的新进入者,通过持续的产品研发和迭代,2024年产品出货快速增长,以4千万美元的收入占据10.9%的市场份额,排名第二。

Switch市场高度集中,单个全球供应商占据了超过90%的市场份额。其核心障碍在于高速SerDes和switching-fabric设计的复杂性限制了厂商的参与。凭借自主研发的SerDes IP、工程技术诀窍以及从PCIe Retimer芯片开发中积累的类似市场资源,澜起是少数几家能够开发先进PCIe Switch产品的企业之一,目前正在进行此类产品的研发。

CXL互连芯片是基于新兴的CXL高速互连协议设计的。由于CXL的应用和生态系统开发仍处于早期阶段,大规模商业部署尚未实现。因此,市场仍处于起步阶段,尚未形成客观完整的竞争格局。随着行业标准的成熟和应用场景的扩展,澜起作为已在CXL互连芯片领域建立技术能力和产品储备的企业,有望在市场发展过程中获得进一步的竞争力。

打开APP阅读更多精彩内容

高速互连芯片定义及分类高速互连芯片是支撑数据中心、服务器及计算机实现高速数据交互的必备芯片,主要解决智能算力系统持续升级背景下各类数据传输的瓶颈。高速互连芯片适配多种 标准化通信协议,通过信号处理、架构优化等方式,保障数据在各系统间高效、可靠传输。

高速互联芯片

按技术类别区分,高速互连芯片主要分为三大类:内存互连芯片、PCIe/CXL 互连芯片和以太网及光互连芯片等。其中,内存互连芯片包括内存接口及模块配套 芯片,主要用于提升内存数据访问的速度及可靠性;PCIe/CXL互连芯片包括PCIe Retimer、PCIe Switch、CXL MXC、CXL Switch等芯片,主要用于数据中心和服务器 单机多卡连接、内存池化、内存扩展等;以太网及光互连芯片包括Ethernet Retimer/ Switch、oDSP、NIC、硅光芯片等,主要用于数据中心集群组网等长距离、高带宽的 互连方案。全球数据正以指数级速度增长,预计 2025年全球数据生成量将达197.3 ZB(泽字节,1泽字节等于10²¹字节),到2030年将增长达到635.3 ZB,复合年增长率达到26.3%。海量数据的产生,使得数据处理及数据交互需求呈井喷式增长,高速互连芯片作为数据传输的必要支撑,潜 在需求量随之大幅提升。

各类标准化通信协议不断演进,传输速率持续提升,以PCIe协议为例,每次迭代升级,传输速率均会翻倍。数据传输速率加快,会带来显著的信号衰减、信号完整性等问题。高速互连芯片可有效解决这些难题,其在数据传输中的必要性和价值量与日俱增。

2022年ChatGPT问世,带动AI训练的需求;2024年后AI应用加速落地,带动AI推理的需求。大模型的训练和推理正在深层次改变AI服务器的架构,摒弃单纯增加服务器数量的方式,转而采用「强扩展」(Strong Scaling)模式,通过提升内存带宽、增加网络硬件密度等措施构建高带宽、低延迟的算力集群。这一转变使得芯片间、服务器机箱之间、服务器集群间互连以及数据中心间之间的互连需求激增,对高速互连芯片的数量和复杂度都提出了更高要求。

高速互联芯片的全球服务器及PC市场需求

高速互连芯片以服务器领域为主要应用场景,在PC领域亦有部分应用。

AI服务器对高速互连的需求与日俱增,成为支撑高速互连芯片市场扩容的因素之一。全球AI服务器出货量从2020年的0.5百万台增至2024年的2.0百万台,复合年增长率为45.2%;展望未来,其出货量预计将从2025年的2.5百万台增长至2030年的6.5百万台,复合年增长率为21.2%。AI服务器需求的增长,源于其计算负载对更高带宽、更高效数据交换的需求。多芯片集群架构需高带宽、低延时互连支撑大规模数据交互,从而推动PCIe/CXL互连芯片、以太网及光互连芯片的需求,同时推动对更大容量及 更高带宽系统主内存的需求。

随着AI服务器采用多卡互连+高速协议架构,支持PCIe 6.0、CXL 3.0等新一代标准的高速互连芯片需求将持续攀升。通用服务器市场需求相对稳定,但同时也需要高速互连芯片来提升数据访问稳定性,其增速虽较AI服务器更为平缓,仍是芯片市场的重要支撑。

全球服务器出货量,按服务器类型(AI、通用)拆分,2020年至2030年(预估)

全球PC出货量总体呈平稳增长趋势,2024年出货量为258.9百万台,未来预计出 货量将从2025年的262.9百万台增长至2030年的297.7百万台,复合年增长率为2.5%。

在AI时代,尤其是大模型爆发式发展以来,数据中心和服务器对于高速互连的需 求呈指数级增长,直接拉动高速互连芯片市场扩容。摩尔定律持续推动半导体进步, 因此需要创新的互连产品来克服日益多样化的算力架构中的带宽瓶颈。同时,Scaling Law表明,AI模型的性能随着模型规模、训练数据集规模及计算负荷(FLOPs)的扩大而提高,这对数据传输带宽及内存访问效率提出越来越严格的要求。这使得高速互连芯片成为AI算力扩展的关键技术。

2024年全球高速互连芯片市场规模为154亿美元,预计将于2030年进一步增长至490亿美元,复合年增长率为21.2%;其中,中国市场成为增速最快的细分市场之一,2024年其市场规模占全球约为25%,2030年预计提升至30%,市场占比增长的主要原因为未来中国AI服务器需求增速预计将高于全球。

从技术类别来看,全球内存互连芯片市场规模预计从2024年的12亿美元增长至 2030年的50亿美元,复合年增长率为27.4%;PCIe/CXL互连芯片市场规模预计从2024 年的23亿美元增长至2030年的95亿美元,复合年增长率为26.7%;以太网及光互连芯片市场规模预计从2024年的120亿美元增长至2030年的345亿美元,复合年增长率为19.3%。

内存互连芯片

内存互连芯片是实现内存数据高速传输与可靠访问的核心组件,传统产品体系包 括内存接口芯片(RCD/DB)和内存模块配套芯片(SPD、TS、PMIC),随着AI及大数据 应用的发展以及相关技术演进,内存互连芯片衍生出适应新型算力需求的品类,包括 用于服务器内存模块的高带宽内存接口芯片(MRCD/MDB)和用于PC内存模块的时钟驱 动器芯片(CKD)。从定价来看,不同产品类型差异较大,单价范围为约0.2美元至16.0美元。• 内存接口芯片(RCD/DB)

内存接口芯片(RCD/DB)是服务器内存模块的核心逻辑器件,作为服务器 CPU存取内存数据的必由通路,其主要作用是提升内存数据访问的速度及可靠性。 DDR4及DDR5内存接口芯片按功能可分为两类:一是RCD(寄存时钟驱 动器),用来缓冲来自内存控制器的地址、命令、时钟、控制信号;二是DB(数 据缓冲器),用来缓冲来自内存控制器或内存颗粒的数据信号。仅采用RCD的内 存模块为RDIMM(寄存双列直插内存模块),同时采用RCD和DB的内存模块为 LRDIMM(减载双列直插内存模块)。目前RDIMM为市场主流的内存模块类型。 根据JEDEC标准,每根DDR4或者DDR5服务器内存模块(RDIMM/LRDIMM)需 要一个RCD芯片。DB芯片用在LRDIMM上,其中每根DDR4 LRDIMM需要9颗 DB芯片,每根DDR5 LRDIMM需要10颗DB芯片。

• 内存模块配套芯片(SPD、TS、PMIC)

根据JEDEC标准,DDR5内存模块上除了内存颗粒及内存接口芯片外,还 需要三种配套芯片,分别是SPD(串行检测集线器)、TS(温度传感器)以及PMIC(电源管理芯片)。SPD内置EEPROM(带电可擦可编写只读存储器),用于存储内 存模块的相关信息以及模块上内存颗粒和相关器件的所有配置参数,同时SPD作为I2 C/I3C总线集线器,是系统主控设备与内存模块上组件之间的通信中心。此外,SPD内部还集成了一颗TS,可连续监测SPD所在位置的温度。TS是DDR5高精度温度传感器芯片,符合JEDEC规范,支持I2 C和I3C串行总线,用于实现对内存模块的温度监控。PMIC为内存模块上的其他芯片提供电源支持,进行电源管理。

根据JEDEC标准,每根DDR4和DDR5服务器内存模块都包含一个SPD。此 外,每根DDR5 RDIMM/LRDIMM/MRDIMM还需要一个PMIC及两个TS。主流的DDR4和DDR5 PC内存模块通常包含一个SPD,而DDR5 PC内存模块还需要一个PMIC。DDR5内存模块中的SPD相比DDR4中的更为复杂,价值也更高。

• 高带宽内存接口芯片(MRCD/MDB)

MRCD/MDB芯片是服务器高带宽内存模块MRDIMM的核心逻辑器件,每 根MRDIMM模块均需要搭配1颗MRCD、10颗MDB。MRDIMM通过MDB芯片 可以同时访问两个DRAM内存阵列(而传统RDIMM只能访问一个阵列),从而在 标准速率下实现双倍带宽。该产品主要应用于云计算、AI等对内存带宽要求较高 的应用领域。

• 时钟驱动器芯片(CKD)

根据JEDEC定义,当DDR5数据速率达到6400MT/s及以上时,PC内存模块需引入CKD芯片,对时钟信号进行缓冲和重新驱动,以满足高速时钟信号的完整性和可靠性要求,这对在有关数据速率下稳定运行至关重要。CKD芯片用于更高速率的PC端内存模块上,一般一根PC端内存模块需要配置一颗CKD芯片。一般来说,一台PC需要配置一至两根内存模块。

DDR4的生命周期覆盖2013年至2025年,DDR5的生命周期预计将从2021年延续至2030年。DDR5 MRDIMM预计从2025年前后开始规模应用。内存颗粒与内存模块产品的代际更迭,正从需求量与价值量双维度,驱动内存互连芯片市场增长进入快速发展通道。

内存互连芯片市场规模

内存互连芯片主要应用于服务器领域,部分内存互连芯片亦应用于PC领域,其市场规模与服务器及PC的出货量、单台配置的内存模块种类及数量密切相关。

全球内存模块的市场需求 2020年至2024年,服务器内存模块出货量从158.2百万根增长至170.4百万根;到 2030年预计将攀升至306.6百万根,2025年至2030年间的复合年增长率约为10.8%,呈 现良好增长态势。从市场结构上看,服务器内存模块正加速向DDR5世代迈进:DDR5 从2021年开始在下游应用,到2024年渗透率已超过50%,预计在2025年将超过85%。同时,DDR6内存模块有望在2029年前后实现商业化应用,为市场注入新的增长动力。

驱动服务器内存模块需求量增长的核心因素,在于全球服务器出货量的增长,以及单台服务器内存模块配置数量的增加。AI服务器的崛起,进一步推动了市场需求。由于对内存容量的要求显著增加,一般来说,一台通用服务器配置8-12根内存模块,而一台AI服务器配置16-24根内存模块。因此,随着AI技术在各行业的广泛应用,AI 服务器渗透率持续提升,将直接推动服务器内存模块整体需求增速高于服务器增速, 进而为内存互连芯片市场带来广阔的发展空间。

内存互连芯片是JEDEC定义的内存模块标准器件,其市场规模从2020年的767.9 百万美元增长至2024年的1,168.0百万美元,预计未来将进一步从2025年的1,579.4百万 美元增长至2030年的5,005.2百万美元,期间复合年增长率高达25.9%。

内存模块需求增长带动芯片市场扩容 内存互连芯片与内存模块有着明确的配比关系,其需求量与内存模块紧密相关。根据弗若斯特沙利文的资料,服务器内存模块的需求量将从2025年的183.9百万根跃升至2030年的306.6百万根,这一显著增长趋势,将直接促使内存互连芯片数量同频增长,成为市场规模扩张的基础。

服务器产品升级激发新的市场增长点

• DDR5技术升级提升芯片价值:由于产品技术难度、复杂度和性能的提升, DDR5 RCD、SPD芯片价值量较DDR4明显增加;同时,服务器DDR5内存模块 新增配套芯片的需求,包括TS和PMIC芯片。产品升级不仅带来芯片单价提升, 更拓展了芯片种类,成为DDR5世代市场增长的动力。

• 新型高带宽内存模块MRDIMM创造市场增量:基于AI应用对内存带宽的迫切需 求,MRDIMM以其优异的带宽性能,预计将成为主流AI服务器系统主内存的优 选方案。2025年,MRDIMM开始在下游规模应用,预计至2030年,其在AI服务 器内存模块中的渗透率将达30%,出货量高达53.4百万根,2025年至2030年的复 合年增长率为148.0%。相较广泛应用的RDIMM(仅需一个RCD),MRDIMM所 需的MRCD价值更高,同时新增10颗MDB的需求,因此随着MRDIMM渗透率不 断提升,将显著推高内存互连芯片市场规模。

• 子代持续迭代维系平均销售价格:DDR5 RCD芯片预计推出6个子代产品, MRCD/MDB芯片预计有3个子代产品,未来几年持续的子代迭代,将通过技术创 新与性能优化,维系产品的平均销售价格与毛利率,为内存互连芯片市场的长期 稳定增长提供保障。

PC领域市场主要增长逻辑

• DDR4至DDR5升级新增芯片需求:PC领域的DDR5内存模块(包括UDIMM/ SODIMM/CAMM/LPCAMM)需要搭配一颗更高规格、价值量更高的SPD,并新增一颗PMIC,推动DDR5世代芯片价值量提升。

• DDR5支持速率提升进一步带动芯片需求扩容:DDR5第一子代产品支持的速率 是4800MT/s,当数据速率达到6400MT/s及以上时,PC内存模块(包括CUDIMM/ CSODIMM/CAMM)需要新增加一颗CKD芯片,该芯片从2025年开始渗透,预计2029年覆盖几乎所有PC内存模块,开拓消费级市场新空间。

内存互连芯片市场的发展趋势

• 算力爆发驱动内存容量及带宽需求增长:大模型训练与推理对算力的迫切需求,正持续推高内存容量和带宽升级。以GPT为代表的大模型,参数规模突破万亿 级,推动AI服务器内存配置显著升级—-单台主流AI服务器通常需部署超20条 DDR5内存模块,内存容量和数量远超通用服务器。同时,算力的爆发也对内存 带宽提出了更高的要求,DDR5第一子代RDIMM支持速率为4800MT/s,第六子 代预计突破9000MT/s,而第二子代MRDIMM更是达到12800MT/s。随着技术成 熟及生态逐步完善,MRDIMM凭借更高带宽与综合性能,有望取代RDIMM成 为AI服务器主流方案,带动MRCD/MDB芯片需求激增。在PC领域同样呈现高速 发展态势,DDR5在游戏本和AI PC等高阶终端加速渗透,模块速率逐步迭代至 6400 MT/s及以上。为了保障高速运行下的信号完整性,预计到2029年几乎所有 的PC内存模块都将标配CKD芯片。

• 技术迭代周期显著缩短:内存互连芯片技术正沿「协议升级迭代 - 传输速率提 升-芯片功能复杂化」路径加速演进,高速信号处理与低功耗设计等技术成为核 心竞争点,内存互连芯片的价值量将持续提升。在服务器领域,DDR4仅经历四 个子代迭代,每个子代的迭代周期约为18~24个月;而DDR5预计有六个子代,DDR5第二子代产品2024年出货已超过第一子代产品,第三子代在2025年快速上量,当前子代迭代周期已逐步缩短至12-18个月,技术迭代节奏较DDR4世代明显 提速。

• 市场集中度持续提升:从内存互连芯片市场发展历史来看,行业领先企业凭借丰 富的产品组合、深厚的技术积累、完善的专利布局形成了完整的内存互连解决方 案能力,在标准制定、研发创新等方面发挥引领作用、具备显著优势,逐步实现 市场份额向少数几家头部企业集中。展望未来,行业头部企业基于其市场领先优势,持续通过前瞻性投入下一代技术研发、优化供应链管理,这些企业有望进一步提升其市场竞争力和市场份额,推动行业资源的高效整合与合理配置。

PCIe/CXL互连芯片

全球PCIe/CXL互连芯片市场 PCIe互连芯片市场概览及市场规模 PCIe互连芯片的定义及分类 PCIe互连芯片是数据中心和服务器高速数据互连的核心组件,遵循PCI-SIG标准体系,主要产品分为两大类:• PCIe Retimer芯片:适用于PCIe协议的超高速信号调理芯片,主要用于解 决数据在高速、远距离传输场景中时序不齐、损耗严重、完整性差等问 题,在CPU与高速外设(如GPU、AI加速卡、SSD卡及网卡等)的互连中发 挥重要作用。从定价来看,不同产品类型差异较大,2024年行业平均单价 范围为约25.0美元至50.0美元。

• PCIe Switch芯片:用於擴展接口數量,通過內部交換架構實現CPU與外圍 設備(如NIC、SSD、GPU)之間的高速數據轉發,實現更多設備間的高密 度PCIe互連。從定價來看,不同產品類型差異較大,芯片價格主要取決於 其支持的鏈路數。2024年行業平均單價範圍為約600.0美元至1,200.0美元。 近年來,PCIe協議技術迭代加速:從PCIe 5.0(32GT/s)升級至PCIe 6.0(64GT/s), 傳輸速率實現翻倍,最新發佈的PCIe 7.0規範更將單通道速率提升至128GT/s。在下游 應用方面,支持PCIe 5.0協議的相關芯片和設備正在成為市場主流,未來技術將持續向 更高速率、更低延遲及低功耗方向演進,以匹配AI服務器等新興場景的高速互連需求。

PCIe互連芯片市場規模 PCIe互連芯片市場規模從2022年的469.2百萬美元快速增長至2024年的2,288.6 百萬美元。行業預測顯示,未來該市場將持續高速增長,預計2030年市場規模將達到 7,761.0百萬美元,2025年至2030年間的年複合增長率高達20.1%。

PCIe互连芯片市场的主要驱动因素

• AI服务器出货量激增,拉动芯片需求放量:AI服务器架构中,随着GPU/AI芯片 数量持续攀升、模型规模迅速扩大,对系统带宽及高速互连需求大幅增长,PCIe 互连芯片已成为高速设备间互连的关键器件。PCIe Switch提供扩展或聚合能力, 并允许更多的设备连接到一个PCIe端口,而PCIe Retimer则用于保障系统的信号 完整性与稳定性,提升高速信号的有效传输距离。以一台主流8卡GPU服务器为 例,通常需配备2至4个PCIe Switch实现拓扑扩展,同时需要8至16个Retimer, 以延长CPU与外设间的有效传输距离。因此,PCIe互连芯片已成为AI服务器中 不可或缺的核心器件,其需求量与AI服务器出货量呈正相关。

• PCIe协议持续迭代升级,拓展应用场景边界:目前PCIe 5.0正在逐步成为市场主 流,未来还将进一步向PCIe 6.0及PCIe 7.0演进,PCIe协议每次迭代将带来数据 传输速率翻倍,由此驱动两大增长逻辑:一方面,更高速率带来更复杂的信号完 整性问题,PCIe Retimer的应用场景从当前的CPU及GPU/AI加速卡/SSD/网卡互 连,将延伸至有源线缆(AEC)、边缘计算设备、智能汽车等连接密集型场景;另 一方面,协议迭代推动服务器集群组网需求,PCIe Switch需承担多设备带宽优化 与拓扑架构升级任务,在AI推理服务、数据中心高密度部署等场景中重要性持续 提升。

CXL互连芯片市场概览及市场规模

CXL互连芯片市场的定义及分类 CXL互连芯片是基于CXL协议构建的高速互连核心器件,其物理层沿用PCIe标 准,可以实现CPU、GPU、内存间高速低延迟的数据交互,主要应用于内存扩展和内 存池化场景,主要产品分为两大类。从定价来看,由于CXL的应用和生态系统开发尚 处于早期,相关产品还未达到规模商业量产阶段,目前还未形成成熟的定价体系。现有产品的单价取决于规格及功能,范围一般为约100美元至1,000美元。

• CXL MXC芯片:作为处理器与CXL内存模块高速连接枢纽,负责完成协议转换、内存访问调度及一致性控制,是构建内存扩展和内存池化架构的 关键控制器;

• CXL Switch芯片:用于实现多个CXL主机及设备之间的互连与资源管理,支持单个或者多个CPU连接多个CXL内存或加速设备,提升系统扩展能力 和资源利用效率,是大规模内存池化架构的核心支持组件。两者协同构建CXL互连解决方案,将在新一代数据中心架构中发挥重要作用。CXL互连芯片市场规模 2024年CXL互连芯片市场尚处于商业化初期,市场规模约为4.3百万美元,行业预测未来几年该市场将迎来爆发式增长,预计至2030年市场规模将达到1,703.1百万美元,2025年至2030年期间的复合年增长率高达170.2%。

CXL互连芯片市场的主要驱动因素

• CXL协议持续在AI领域渗透,拉动芯片需求增加:在AI领域,CXL技术通过支 持GPU和FPGA(现场可编程闸阵列)等加速器与主处理器的高效协作,可显著提 升AI模型训练和推理的速度,实现低延迟、高速的数据传输,从而大幅提高计算效率;同时CXL技术支持内存扩展和共享机制,为AI应用提供更大的内存空间 和更灵活的资源分配方案,解决内存带宽瓶颈。作为CXL技术落地的核心载体, CXL互连芯片支撑上述应用场景,其需求与AI服务器密切相关,并将在AI领域 发挥更大的作用。

• 系统架构重构及连接复杂度提升,推动应用场景拓展:AIGC推动数据中心向万 卡级集群演进,芯片至数据中心的多维互连复杂度指数级提升,传统互连方案难 以满足TB级带宽与百纳秒级延迟需求,CXL通过内存池化与高速互连实现架构 升级:CXL MXC在内存扩展及内存池化领域能够有效提升内存容量和带宽,以 适配云计算和AI等数据密集型应用的需求;同时,CXL Switch也逐步开始应用 于服务器平台,支持多节点设备的内存和资源共享,优化服务器集群的拓扑架构 与资源利用率。

目前,国际知名大型互联网厂商正在探索在其新型服务器集群中 部署CXL内存资源池,单个内存池通常需要配置16-32颗CXL MXC和2-4颗CXL Switch芯片。随着CXL内存池在服务器中渗透,CXL互连芯片市场将进入爆发增 长通道。CXL技术可通过内存池化赋能内存扩展,显著提升GPU集群的算力效 率,并降低总拥有成本(TCO)。

PCIe/CXL互连芯片的准入壁垒及关键成功因素

• 协议驱动的技术迭代与创新能力:PCIe/CXL互连芯片的核心竞争力根植于对协 议标准演进的快速响应及底层技术突破。企业需紧跟从PCIe从5.0向6.0乃至7.0、 CXL从1.0到3.x的协议迭代节奏,通过持续研发投入攻克信号处理、编码算法等关键技术。当PCIe协议持续升级时,需优化高速SerDes串行接口技术,以解决高频传输中的信号衰减、时序抖动等问题,保障芯片兼容性与稳定性;而CXL技术正朝着带宽倍增、延迟优化与功能拓展方向演进,在支持内存池化、点对点直 连的同时,未来或结合光互连技术突破TB级带宽与亚50ns延迟瓶颈。从底层技术看,SerDes作为高速串行传输的「神经中枢」,其速率提升(如PCIe 6.0所需的 64GT/s)与信号完整性优化能力直接决定互连芯片的稳定性与延迟表现;而DDR 控制器技术则通过影响内存访问效率,成为支撑CXL内存池化的关键技术节点。

• 深度需求洞察与生态协同能力:PCIe/CXL互连芯片的另一核心成功要素,在于 对下游客户需求的深度理解与生态关系的紧密维系。随着AI服务器、数据中心等 下游应用场景对高速互连需求的爆发式增长,企业需精准把握客户在PCIe 6.0、 CXL 3.0等协议迭代需求、低延迟、高带宽等性能指标要求,以及成本控制方面 的核心诉求,通过技术预研针对性开发,实现快速响应。同时,企业应与服务器 与云计算厂商等合作伙伴建立长期战略合作,深度参与硬件架构设计与标准制 定,形成「需求反馈-技术迭代-生态适配」的闭环。这种「需求驱动创新+ 生 态协同共进」的模式,不仅能提升产品竞争力,更能构筑起市场壁垒,成为企业在PCIe/CXL市场立足的关键。

以太网及光互连芯片

以太网互连芯片是数据中心、云计算及AI基础设施的核心硬件,实现设备间高速数据交换与低时延通信。主要分为三类:(i)以太网交换芯片(Ethernet Switch),用于数据包的转发和网络流量的调度,是数据中心网络的骨干器件;(ii)NIC(网卡芯片),部署于服务器端,是主机接入以太网并实现数据传输的关键接口;及(iii)Ethernet Retimer 芯片,解决长距离高速信号传输中的时序失真与信号衰减,保障数据传输的完整性与系统稳定性,尤其适用于AI服务器与云计算节点。以太网互连芯片

全球以太网互连芯片市场规模从2020年的60亿美元增长至2024年的94亿美元, 期间复合年增长率达11.6%,增长主要受云计算与数字基础设施建设的推动。未来随着 AI大模型部署加速,AI服务器、超大规模数据中心及高带宽存储系统对高速低延迟网络的需求激增,400G/800G以太网方案逐步落地,并向1.6T演进,驱动以太网互连芯片需求量和价值量同步提升,预计2030年市场规模将达到247亿美元,2025年至2030 年间复合年增长率高达17.9%。

光互连芯片

光互连芯片是实现高速数据传输的关键组件,通过光电转换技术,支撑下一代数据中心和AI基础设施对高带宽、低功耗互连的需求,已成为核心技术之一。光互连芯片主要分为三类:

• DSP芯片:负责高速信号的调制╱解调、波形整形及数字信号处理(DSP) 纠错功能,是400G、800G等先进调制格式不可或缺的核心器件;

• 激光驱动芯片(Driver)与跨阻放大器(TIA),其中Driver将电信号转换为高频 模拟信号以驱动光发射器,TIA将光探测器输出的微弱电流信号放大为电 压信号,保障高速、高灵敏度的接收链路;

• 硅光芯片:通过在单一硅基平台上集成光子和电子功能,实现小型化、高速光互连,有效解决先进计算系统中的带宽瓶颈与功耗挑战。全球光互连芯片市场规模从2020年的4亿美元迅速增长至2024年的26亿美元,复合年增长率高达57%,增长原因主要源于400G/800G光模块在AI数据中心规模化部署。

展望未来,随着大模型训练集群的GPU规模持续攀升,节点间通信带宽密度和能效比需求急剧增长,光互连技术将成为高性能架构中重要方案,预计至2030年市场规模将达到99亿美元,2025年至2030年期间的复合年增长率为21.5%。

高速互连芯片市场竞争格局

全球高速互连芯片市场正伴随AI基础设施扩建和服务器架构升级进入高速增长期。当前市场已形成多个技术方向并行演进的格局。内存互连芯片市场:从DDR4到DDR5世代,该市场的主要厂商稳定在三家,即澜起科技、Renesas及Rambus,市场竞争份额高度集中,目前前三大厂商合计市场份额超过90%。头部 企业逐步形成了「技术壁垒+客户绑定」的双重竞争护城河。

PCIe/CXL互连芯片市场:PCIe互连芯片市场相对较为成熟,展现出显著的头部集中态势,前五大厂商占据超90%的市场份额。2024年,前两大PCIe Retimer厂商合计市场份额96.9%,而PCIe Switch细分市场则由单一厂商占据主导地位。这些领先企业具备高速SerDes设计能力及PCIe协议迭代及产品产业化经验(如已量产PCIe 5.0产品并 送样PCIe 6.0产品),覆盖从芯片到系统级互连的复杂拓扑设计需求,进一步巩固其市场竞争力。

CXL互连技术是近几年兴起的前沿技术,基于该技术的应用和产业生态正在逐步完善,因此相关芯片目前尚未规模量产,市场处于起步阶段。

以太网及光互连芯片市场:少数国际巨头凭借技术及先发优势,占据以太网及光互连芯片市场主要份额。

内存互连芯片2024年整体呈现高度集中的市场格局,前三家企业合计占据93.4%的市场份额; 其中,澜起科技以4.3亿美元的收入占据36.8%的市场份额,排名第一。

PCIe Retimer 2024年该市场同样也呈现出极高的市场集中度。按2024年的市场份额计, PCIe Retimer提供商中澜起科技排名全球第二。作为市场的新进入者,通过持续的产品研发和迭代,2024年产品出货快速增长,以4千万美元的收入占据10.9%的市场份额,排名第二。

Switch市场高度集中,单个全球供应商占据了超过90%的市场份额。其核心障碍在于高速SerDes和switching-fabric设计的复杂性限制了厂商的参与。凭借自主研发的SerDes IP、工程技术诀窍以及从PCIe Retimer芯片开发中积累的类似市场资源,澜起是少数几家能够开发先进PCIe Switch产品的企业之一,目前正在进行此类产品的研发。

CXL互连芯片是基于新兴的CXL高速互连协议设计的。由于CXL的应用和生态系统开发仍处于早期阶段,大规模商业部署尚未实现。因此,市场仍处于起步阶段,尚未形成客观完整的竞争格局。随着行业标准的成熟和应用场景的扩展,澜起作为已在CXL互连芯片领域建立技术能力和产品储备的企业,有望在市场发展过程中获得进一步的竞争力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

-

PCIe协议分析仪能测试哪些设备?2025-07-25 1686

-

澜起科技推出PCIe 6.x/CXL 3.x Retimer芯片2025-01-22 1613

-

曦智科技发布全新光互连产品,获2023全球闪存峰会多项殊荣2023-08-15 1226

-

以太网接口的类型及参数2023-02-14 4638

-

使用多代 PCIe 构建高性能互连2022-07-21 2700

-

光互连有什么优势?2019-10-17 1666

-

10Gb以太网物理层接口的发展趋势2019-04-24 2228

-

互连领域的里程碑!英特尔携手行业伙伴推出CXL技术2019-03-14 490

-

低成本CAN与以太网互连的方案2017-09-07 1350

-

【我是电子发烧友】了解以太网术语 – 数据速率、互连介质和物理层2017-06-14 5071

-

光互连技术2016-01-29 2844

-

LON现场控制网络到以太网互连适配器的设计2011-09-09 1003

-

高速接口互连2010-08-20 1119

-

CAN总线互连中网关的设计与实现2009-08-12 584

全部0条评论

快来发表一下你的评论吧 !