不同verilog代码的RTL视图

可编程逻辑

描述

刚开始玩CPLD/FPGA开发板的时候使用的一块基于EPM240T100的板子,alter的这块芯片虽说功耗小体积小,但是资源还是很小的,你写点稍微复杂的程序,如果不注意coding style,很容易就溢出了。当时做一个三位数的解码基本就让我苦死了,对coding style的重要性也算是有一个比较深刻的认识了。

后来因为一直在玩xilinx的spartan3 xc3s400,这块芯片资源相当丰富,甚至于我在它里面缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显示用)。而最近接触EPM7128,它的资源似乎也不丰富,我写着写着有时不注意就无法布线了。由此可见coding style对设计的重要性,尤其是在资源紧张或者速度要求较高的设计中。我个人对前者的体会深一些,高速的设计没有涉及过,只是明白一些用流水线提高速度的方法。

可以步入正题了,先拿一段简单的代码开始吧。我先提一点,这回我用的是quartus II 7.0进行测试,其它的EDA工具综合出来的RTL视图可能会不一样,所以仅作为在quartus II 7.0环境下的一些参考吧。不过思路是一样的,可以借鉴的。

Ex1:

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0);

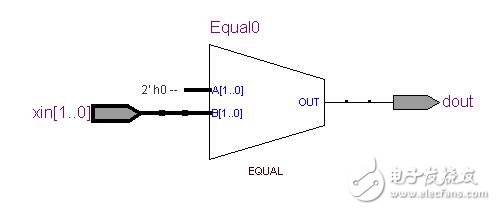

代码很简单,就是当xin==2’b0时dout=1,否则dout=0。上面这段程序的RTL视图如下:

其实就是一个比较器,如果xin=2’h0,那么输出OUT就为1。和设想一样。

下面是我在参考一些别人的代码的时候看到别人一种常见的写法,它是用了?语句。

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0) ? 1'b1:1'b0;

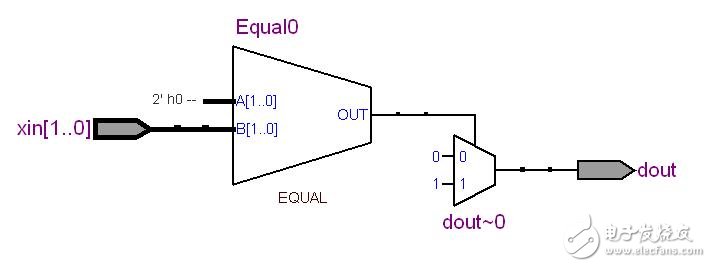

RTL如下:

是不是发现多了以一个选择器(可能不叫选择器吧,但是你明白意思就可以),这样平白无故的就多耗用了一点资源,刚开始的时候我也是傻乎乎的跟着别人用这种写法,但是看到RTL视图后我就不这么干了,既然前者一样可以得到预期结果,为什么我还要画蛇添足多一个选择器呢。所以,推荐使用前者。资源的节约是潜移默化的~_~

(先说一点吧,其它的待我想起或者是感悟到了再提吧,以上也完全是我的个人愚见,如有不妥之处欢迎拍砖~_~)

-

如何自动生成verilog代码2024-11-05 2109

-

JK触发器与T触发器的Verilog代码实现和RTL电路实现2023-10-09 7081

-

Verilog边沿检测的基本原理和代码实现2023-05-12 5800

-

什么样的Verilog代码风格是好的风格?2022-10-24 2554

-

Verilog HIDL的RTL设计风格指南资源下载2021-04-13 1352

-

HDL如何转换成RTL视图?2020-03-23 1733

-

Verilog HDL代码书写规范2017-12-08 9992

-

8051 verilog 版代码2016-05-24 1134

-

verilog代码规范2016-03-25 729

-

verilog_代码资料2016-02-18 760

-

RTL级代码和仿真代码的区别2012-07-21 10441

-

FFT Verilog RTL2010-07-08 983

-

Verilog代码书写规范2010-04-15 678

全部0条评论

快来发表一下你的评论吧 !