FPGA中的testbench介绍

电子说

描述

testbench就是对写的FPGA文件进行测试的文件,可以是verilog也可以是VHDL。verilog和VHDL的国际标准里面有很多不能被综合实现的语句,比如initial,forever,repeat,延时语句#1等等,这些语句就是用来测试的时候使用的。运行环境一般是ise或者vivado或者quartus自带的仿真工具,或者如modelsim一样的第三方仿真工具。

测试机制

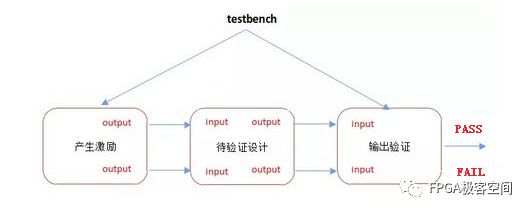

任何一个设计好的模块,都有输入和输出,此模块是否满足要求就是看给定满足要求的输入,是否能够得到满足要求的输出。所以testbench的测试机制就是:用各种verilog或者VHDL语法,产生满足条件的激励信号(也就是对被模块的输入),同时对模块的输出进行捕捉,测试输出是否满足要求。如下图,产生激励输出验证模块两个模块都属于testbench,最好的输出验证模块最终只需要给一个pass和fail的答案出来就可以了。不管是用一个信号表示pass和fail还是用$display()函数打印,最终简单明了的给出过或者不过的信息就好了。请大家写仿真文件的时候尽量做到这点。

运行顺序

跟大家解释一点,所有testbench本质上都是串行执行,因为在CPU环境下,没有可靠并行执行的能力。所有并行的语句,比如两个always模块,fork join语句块,都是软件模拟并行执行的。所以老一点的编译器,信号定义要在initial语句前面,initial的信号要先有初始值后面的语句才能从给定初值开始执行。所以大家写testbench的时候,要注意,最好先定义信号,再写initial语句,后面的语句交换顺序不影响,软件可以识别并按照IEEE标准的顺序去执行。

如果一个模块里面想用并行执行语句用fork join语句,顺序执行用begin end语句。initial语句可以写多个,都是并行执行的,当两个信号在initial冲突的时候,会先执行前面的initial的值。

-

在testbench中如何使用阻塞赋值和非阻塞赋值2025-04-15 1399

-

语法纠错和testbench的自动生成2025-10-27 307

-

testbench_book2016-12-13 778

-

testbench怎么写_testbench经典教程VHDL2017-12-01 58223

-

FPGA教程之简单的Testbench设计的详细资料说明2019-03-01 1661

-

简单的Testbench设计2019-03-08 3083

-

FPGA视频教程:简单的Testbench设计2019-12-11 2779

-

关于testbench在FPGA编程中的技巧2019-07-31 1514

-

介绍FPGA中testbench的编写技巧2020-01-06 2335

-

在模块化设计过程中编写testbench并仿真的方法2020-11-20 5241

-

FPGA验证简介之FPGA开发分析一个testbench2021-04-11 4143

-

testbench是什么? testbench测试的机制是什么?2023-06-28 6902

-

Verilog Testbench怎么写 Verilog Testbench文件的编写要点2023-08-01 6142

-

Testbench自动化验证方法介绍2023-09-04 2085

-

编写高效Testbench的指南和示例2024-10-29 3379

全部0条评论

快来发表一下你的评论吧 !