在高频率下切换高输入电压降压DC/DC转换器的利弊分析

描述

为了减小输出电容和电感的尺寸以节省印刷电路板(PCB)空间,越来越多的高输入电压DC/DC转换器在更高的开关频率下工作。然而,随着输出电压降至5V和更低,设计更快的开关高输入电压降压DC/DC转换器由于几个原因变得越来越困难。其中的关键是较低的工作周期。因此,工作频率超过1 MHz的转换器会以更多的方式影响电源系统,而不仅仅是其尺寸和效率。因此,在设计具有高输入和低输出电压的高开关频率DC/DC转换器时存在折衷。本文探讨了一些设计实例,这些实例证明了在较高频率下切换高输入电压降压DC/DC转换器的好处和缺陷。

为了解释这些权衡,德州仪器工程师建造了三个独立的电源,每个电源的开关频率分别为100,300和750 kHz。如应用笔记“设计高频,高输入电压DC/DC转换器的挑战”所述,¹所有三个DC/DC转换器设计的输入电压为48 V,而输出电压为5 V,输出电流为1A。根据设计人员的说法,这种降压转换器通常用于为5 V逻辑USB供电或作为中间总线转换器来驱动电路板上的其他负载点(POL)稳压器。

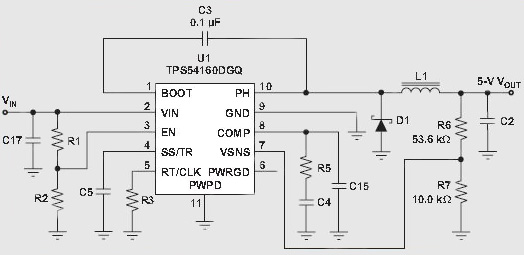

在构建耗材之前,工程师建立了一些设计约束。例如,可接受的纹波电压设置为输出电压的1%,在这种情况下达到50 mV。此外,所选择的峰峰值电感电流为0.5 A.每种设计均基于图1中的电路,采用TI的TPS54160,2.5 MHz,60 V,1.5 A降压DC/DC转换器,集成MOSFET。

图1:基于TPS54160的高频高输入电压降压转换器用作评估设计性能的参考电路在三个不同的频率。

选择滤波器组件

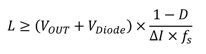

以下公式用于计算每个设计实例的输出电感器和电容器的值。

对于电感,V = L×di/dt

上述公式进一步重组为:

其中占空比D = VOUT/VIN = 5-V/48-V = 0.104,ΔI= 0.5峰 - 峰值,fs是开关频率,VDiode是所用二极管的正向压降。

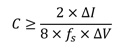

类似地,对于电容器,

I = C×dv/dt

重新组合上述等式,C给出为

其中ΔI= 0.5 A峰值 - 到峰值,ΔV= 50 mV,fs是开关频率。

在根据公式2b选择这些设计的电容器时,工程师认为所选的电容器具有可忽略的等效串联电阻(ESR),这对陶瓷电容器来说是正确的。因此,由于它们的低电阻和小尺寸,所有三种设计都选择了陶瓷电容器,如应用说明中所述。此外,TI建议等式2b的分子中的乘法器2考虑与DC偏置相关的电容降。通常,大多数陶瓷电容器的数据表中都没有考虑到这种影响,TI的设计人员也是如此。

使用图1中的参考电路,设计人员评估了三种不同解决方案的性能,每种解决方案的工作频率分别为100,300和750 kHz。基于使用等式1a至2b的计算选择的输出滤波器组件L1和C2的值与组件大小一起列于表1中。由于误差放大器的补偿元件是单独计算的,因此不在本讨论中介绍。

开关频率(kHz)电容C2(μF/尺寸)电容器面积(mm²)电感器L1(μH)电感器面积(mm²)总计面积(mm²)100 47/1206 18.9 100 150 420 300 10/0805 11.5 33 43.5 192 750 4.7/0603 6.5 15 43.5 182

表1:输出滤波器元件L1和C2的值,开关频率为100,300,和750 kHz。

优点和缺陷

最小输出电压取决于DC/DC转换器IC的最小导通时间和占空比(输出电压与输入电压之比),因此可以轻松计算。最小占空比通过将最小导通时间乘以开关频率来计算(表2)。一旦知道了最小占空比,就可以通过将VIN乘以最小占空比来计算可达到的最低输出电压,如表2所示。可以看出,最低输出电压也受到转换器参考电压的限制,对于TPS54160,开关频率为0.8 V.

开关频率最小占空比最小VOUT为48 VIN(V)100 kHz 0.013 0.8(VREF)300 kHz 0.039 1.87 750 kHz 0.098 4.7 1 MHz 0.13 6

表2:最小输出电压基于130 ns最小导通时间,分别为100 kHz,300 kHz,750 kHz和1 MHz的开关频率。

表2表明设计人员根本无法切换到更高频率以减小组件的尺寸。例如,该表显示在1 MHz开关和130 ns导通时间时,最低可能输出电压限制为6 V.低于6 V意味着跳过脉冲,这会导致更高的纹波电压和噪声。实际上,限流电路可能无法正常工作,因为转换器IC可能无法响应大电流尖峰。因此,表2表明,对于5 V输出,可与TPS54160一起使用的最高频率为750 kHz。在选择更高的开关频率之前,TI设计人员建议检查DC/DC转换器IC的数据表,以确保最小可控导通时间。

由于效率和功耗是DC/DC转换器设计的重要方面,并且它们取决于开关频率,功率MOSFET和输出电感,因此TI工程师仔细检查了这些功能和相关组件。他们发现,与功率转换效率相关的总功耗来自MOSFET驱动,开关和电感器损耗。 FET导通电阻和IC损耗是一致的,因为在所有三种设计中使用相同的IC和MOSFET。由于在每种设计中都选择了具有低ESR的陶瓷电容器,因此认为电容器损耗可以忽略不计。

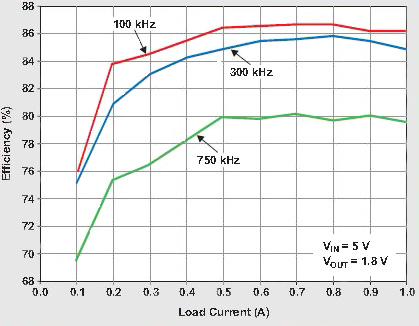

图2中绘制了在三个不同频率下切换的参考转换器电路的测量效率性能。但是,此情况下的输入电压为5 V.该图表明降压转换器效率随着开关频率的增加而降低。/p》

图2:测得的性能表明,对于相同的输入输出电压比,开关频率增加时,降压转换器的效率会降低。

应该注意的是,当输入电压较高时,这些效率数字会进一步下降,尤其是48 V,因为阶跃比现在变得更高,导致更高开关频率下的更多损耗。为了提高所需高频率下的效率性能,TI建议使用具有极低漏极 - 源极导通电阻,低栅极电荷以及满载时低静态电流规格的功率MOSFET。此外,利用具有较低ESR的电容器和电感器有助于进一步减少损耗并提高效率。

表1中的数据反映了电容和电感尺寸与频率的关系。虽然100 kHz和750 kHz设计之间的总面积可节省近250 mm2,但滤波器尺寸减小50%,电路板空间减少55%,必须采用递减收益定律。简而言之,频率越高并不意味着电感器尺寸会相应下降。如该表所示,300 kHz和750 kHz的电感占据相同的面积。

另一个性能参数是瞬态响应。基于开关频率,TI工程师已将表3中参考转换器电路的实际瞬态响应制成表格.TI指出,设计人员必须确保功率IC的误差放大器具有足够的带宽以支持高交叉频率。对于TPS54160,误差放大器的单位增益带宽通常为2.7 MHz。表3显示瞬态响应在较高频率下更好,电压过冲也较低。

开关频率(kHz)交叉频率(kHz)相位裕度响应时间(μs)电压峰值(mV)100 10 60°1000 350 300 30 60°300 300 750 60 50°150 240

表3:对于参考转换器电路,瞬态响应在更高的开关频率下更好,并且电压过冲更低。

最后,TI工程师检查了抖动噪声,这似乎是高转换率和更高开关频率的问题。当占空比很小时,抖动噪声成为开关脉冲的较大百分比。

总之,设计高频开关转换器需要权衡利弊。虽然在尺寸,瞬态响应,电压过冲和欠射等方面存在一些优势,但是缺陷是效率降低和功耗增加,这需要PCB上的散热片或更多的铜。此外,抖动噪声也会随着频率而增加。

-

什么是DC/DC转换器?2024-09-29 851

-

介绍碳化硅器件在高频率LLC谐振DC/DC转换器中的应用2023-02-27 1592

-

非隔离式DC-DC降压转换器如何实现高降压比2022-04-02 7360

-

DC/DC转换器分为几类2021-11-16 2619

-

DC/DC转换器在高频下开关存在的一些好处和挑战2021-04-06 2402

-

NCP3063系列是对流行的MC34063A和MC33063A单片DC-DC转换器的更高频率升级2019-09-25 2294

-

高频率下切换高输入电压降压DC/DC转换器的利弊探讨2019-07-16 2785

-

高输入电压下变频器的高频切换2017-06-24 1373

-

高频、高输入电压DC/DC转换器设计挑战2017-06-16 1521

-

应对高频率高输入电压DC/DC转换器设计挑战的方法2012-05-09 1887

-

高频率、高输入电压DC/DC转换器设计与挑战2011-10-14 17252

-

DC-DC转换器2010-04-19 4166

全部0条评论

快来发表一下你的评论吧 !