详解米勒平台的米勒效应和形成原理

描述

在描述米勒平台(miller plateau)之前,首先来看看“罪魁祸首”米勒效应(miller effect) 。

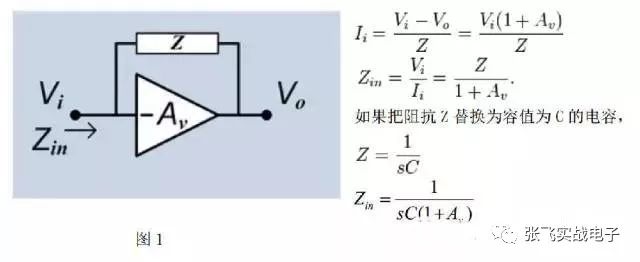

假设一个增益为-Av的理想反向电压放大器如图 1 所示,在放大器的输出和输入端之间连接一个阻值为 Z 的阻抗。定义输入电流为 Ii(假设放大器的输入电流为 0) ,输入阻抗为 Zin,那么有如下的等式关系,

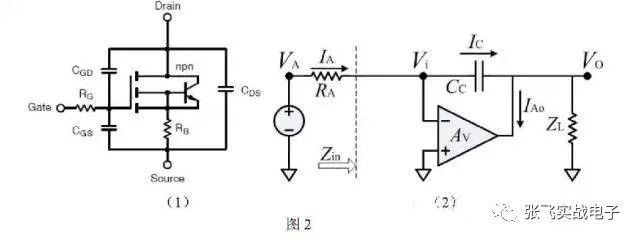

由此可见,反向电压放大器增加了电路的输入电容,并且放大系数为(1+Av) 。这个效应最早是由 John Milton Miller 发现的并发表在他 1920 的著作中,所以称之为米勒效应。再联系到我们的 MOSFET,加入寄生电容的原理图可以由下左图来表示。假设想象图 2(1)的的 MOSFET 是一个共源电路(common source) :Drain 为输出端,Source 接地,Gate为输入端。根据 MOSFET 的小信号模型,MOSFET 形成了一个反向电压放大器,其等效电路可以由图 2(2)来表示。

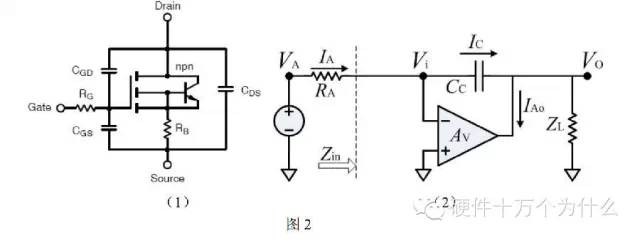

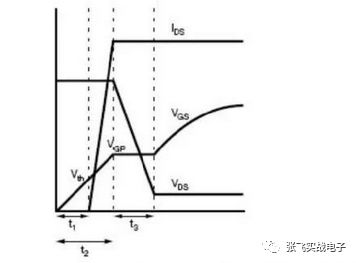

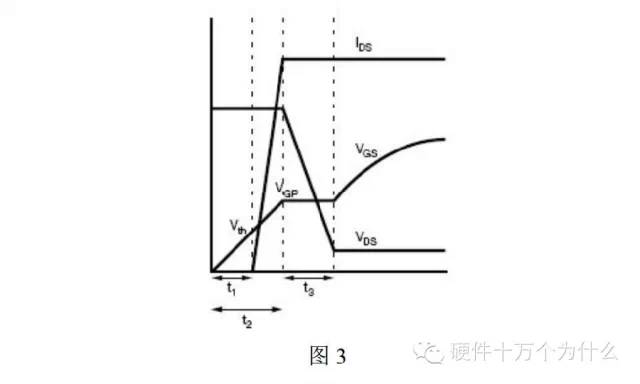

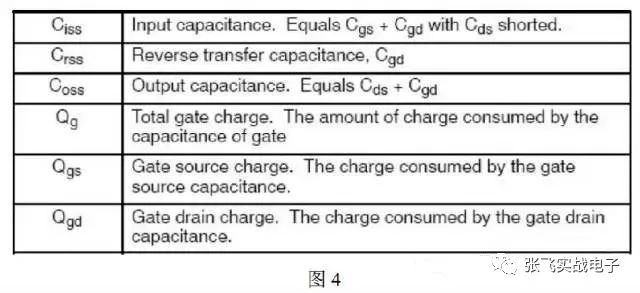

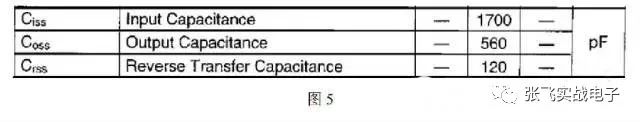

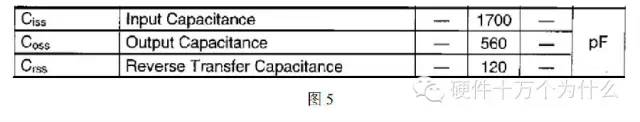

在 0-t1的时间内上升到 MOSFET 的阈值电压。 漏极电流 IDS从 t1结束时到 t3开始时从 0 上升到稳定负载电流,VGS继续上升到米勒平台电压 VGP。在 t3时间内,VGS一直处于平台电压,VDS开始下降至正向导通电压 VF。在 t3 时间后,VGS继续上升。这里我们来分析一下为什么波形会是这个样子。首先,我们需要先要了解一下 MOSFET 寄生电容的大体情况。在 MOSFET 的 DATASHEET中,采用的定义方法如图 4 所示。需要注意的是,Crss就是我们所说的 CGD。

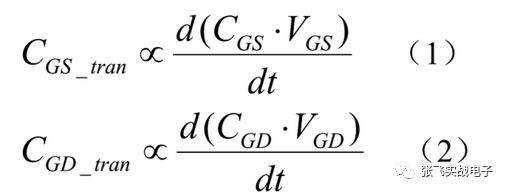

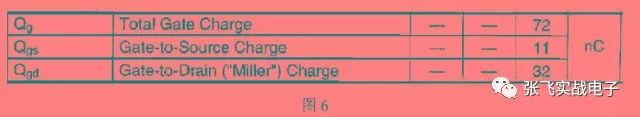

因此,相应的瞬态电容值与乘积(CGS*VGS)和(CGD*VGD)的斜率有关,既接合 MOSFET 的图 3 来看,在 t3时间之前,由于 CGS远大于 CGD,所以在此时间段内 VGS的上升斜率主要有 CGS决定。当 t3开始时,参照式(2, )VGD的变化使得给 CGD在这个时间段内的电容值增加,同样使得充电电流迅速增加。所以在 t3时间内,VGS的斜率主要由 CGD的来决定。值得注意的是,VGS在 t3阶段内的斜率往往都很小甚至为 0,这是因为 VGD在这段时间的电压变化非常大, 使得门极中的大部分电流都用来给 CGD充电, 从而只有很少或者没有电流流向CGS。再次使用IRF540为例, 在DATASHEET上的有这么一组数据, Qgs=11nC,Qgd=32nC. 从前面可以看出,MOSFET 关断状态下的 CGD 远远小于 CGS,但是却需要更多的充电电荷。仔细看 Qgd 的注释中,标明了是受到了“Miller”米勒效果的放大。

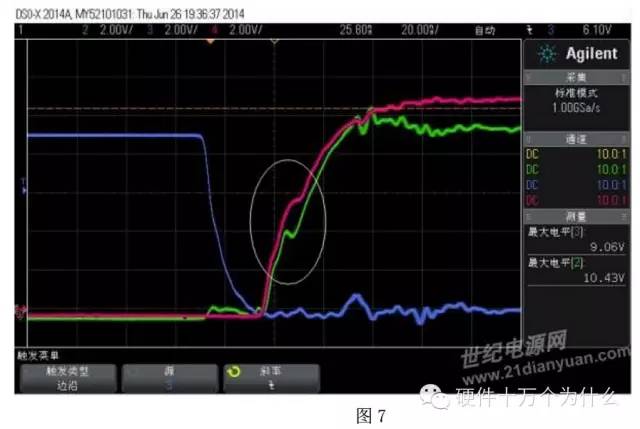

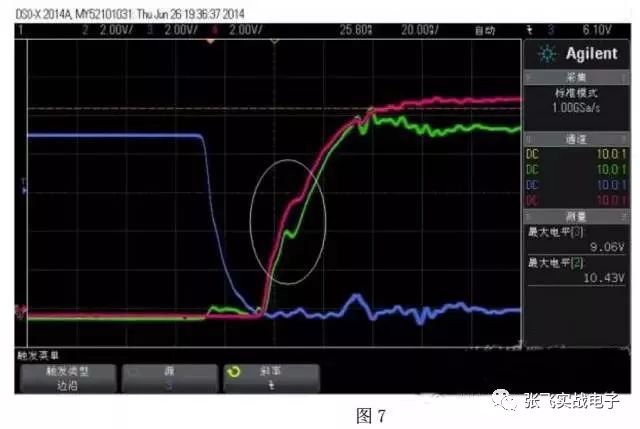

尖峰的主要形成原因与米勒效应并无太大关系, 主要是由于源极附近的杂散电感所致。 在图3 的 t1-t3时刻之间,骤然增加的源极极电流在杂散电感上感应生成了电压尖峰。

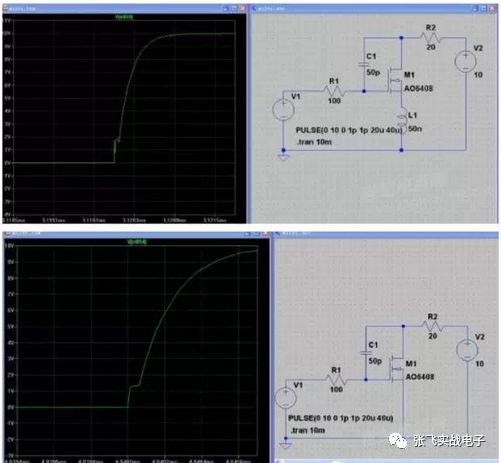

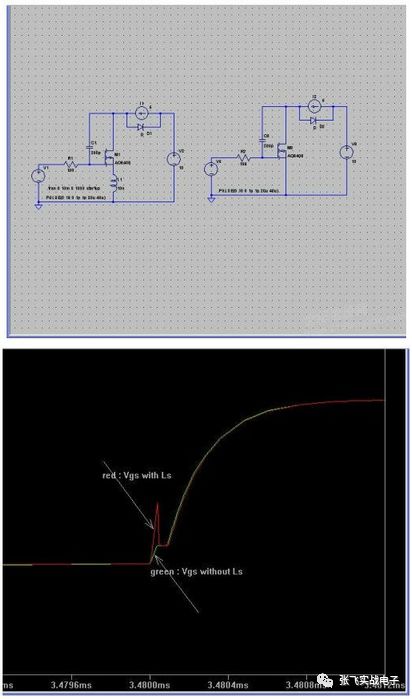

以下是网友一花一天堂的仿真对比试验, 通过在 MOSFET 的源级处加入 nH 级的电感来模拟杂散电感。对比上下两幅图可知,源级附近的杂散电感为米勒平台间电压尖峰的主要原因。

图8

这里需要指出的是,图 3 只是一个近似的画法,大家普遍认同 IDS的拐点与 VGS进入米勒平台发生在同一时刻。这样杂散电感产生的尖峰就出现在了米勒平台之前。但是 VGS进入米勒平台的时间是由 CGD与 VGD的乘积(CGD*VGD)的斜率决定的。当漏极电流很小且输出阻抗很大的时候,VGS进入米勒平台的时间要早于 IDS的拐点。这时,源极的杂散电感形成的电压尖峰就出现在了米勒平台之间。由于上面那段话过于生涩,经 greendot 老师的指点,这里可以用一个比较简单的方法或者说是经验来判断杂散电感的尖峰所处的位置。若 MOSFET 连接的负载为感性(连接于 MOSFET的漏极) ,则产生的波形如图 3 所示,产生的尖峰处于平台之前。其作用原理:假设用一个电流源来模拟感性负载,并在其两端反向并联一个二极管用于模拟 MOSFET 关断期间的电流回路,如图 9 所示。当 Vgs上升至 Vth时,IDS从 0 开始上升,并由式(3)在 VGS上产生感应电压。在 IDS上升至拐点既 IDS等于电流源电流之前,会有一部分的电流通过二极管返回至电流源。此时,由于二极管嵌位的作用,VDS两端的电压为供电电压 Vcc(忽略二极管正向导通电压) 。联系本文关于米勒效应的描述,VDS电压不变的时候,MOSFET 的放大增益为 0,所以此时的 VGS曲线还没有受到米勒效应的影响。当 IDS上升至拐点后,二极管关断,VDS的电压再开始下降,如图 3 所示。此时 MOSFET 形成了一个放大电路,CGD受到米勒效应的影响,使得 VGS进入米勒平台。但 IDS已不再变化,此刻的式(3)为 0,所以形成的电压尖峰处于米勒平台之前。再次感谢一花一天堂的仿真图。通过对比可以发现,感性负载是的杂散电感在 VGS上生成的电压尖峰处于米勒平台之前。

图9

若负载为阻性时,其波形过程为:IDS从 0 开始上升时,VDS=Vcc-(IDS*Load) ,所以 VDS同时开始下降,MOSFET 即刻形成一个放大电路,VGS 进入米勒平台。由于 IDS的上升过程和 VGS进入米勒平台为同一时间, 在杂散电感上形成的感应电压便叠加在了米勒平台区间。 仿真结果如图 10(下图中的 Vds 应为 Vgs)

参考资料:1.Wikipedia, Miller Effect, Common Source.2.Vishay APP NOTE AN605, AN6083.IRF540 Datashee

-

MOS管的米勒效应:如何减小米勒平台2023-02-14 14593

-

米勒效应对MOSFET的危害2023-04-26 5639

-

说说MOSFET中的米勒效应2023-05-16 4026

-

MOS管的米勒效应-讲的很详细2025-03-25 506

-

米勒效应问题2017-12-21 7009

-

揭秘MOS管开关时米勒效应的详情2018-12-19 3939

-

米勒平台是如何形成的?是什么工作原理?2021-03-18 13333

-

米勒平台形成的原理2016-11-02 2070

-

详细分析MOSFET开关过程米勒效应的影响2022-03-10 8615

-

米勒平台的形成原理2022-03-17 1123

-

MOS管的米勒效应:如何平衡抑制米勒效应和抑制EMI风险的关系2023-04-17 9710

-

MOSFET米勒效应详解2023-05-15 11499

-

IGBT中米勒效应的影响和处理方法2023-05-25 11329

-

米勒电容、米勒效应和器件与系统设计对策2023-03-03 5820

-

如何减轻米勒电容所引起的寄生导通效应?2023-09-05 2454

全部0条评论

快来发表一下你的评论吧 !