资料下载

×

51单片机学习教程之中断的详细资料和外部中断及定时器中断程序说明

消耗积分:1 |

格式:pdf |

大小:0.07 MB |

2019-04-16

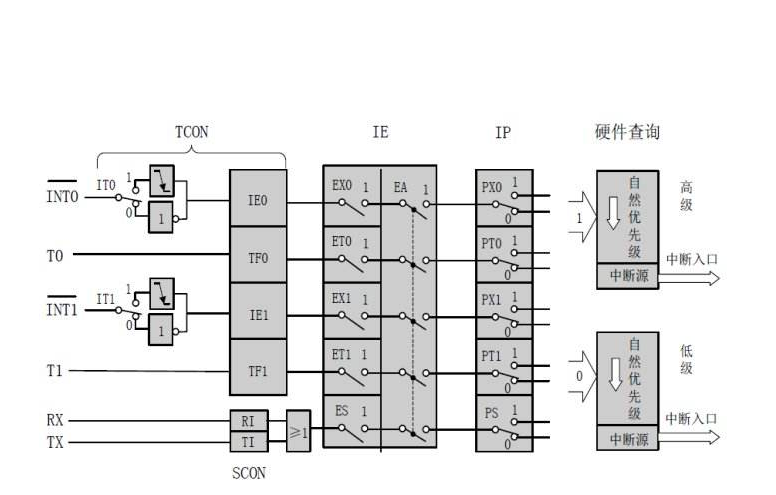

51的中断系统有5个中断源,2个优先级,可实现二级中断嵌套。

P3.2口可由IT0选择其为低电平有效还是下降沿有效。当CPU检测到P3.2引脚上出现有效的中断信号时,中断标志置1,向CPU申请中断。

P3.3口可由IT1选择其为低电平有效还是下降沿有效。当CPU检测到P3.3引脚上出现有效的中断信号时,中断标志置1,向CPU申请中断。

TF0,片内定时/计数器T0溢出中断请求标志。当定时/计数器T0发生溢出时,置位TF0,向CPU申请中断。

TF1,片内定时/计数器T1溢出中断请求标志。当定时/计数器T1发生溢出时,置位TF1,向CPU申请中断。

RI或TI,串行口中断请求标志。当串行口接收完一帧串行数据时置位RI或当串行口发送完一帧串行数据时置位TI,向CPU请求中断。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章